Студопедия КАТЕГОРИИ: АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция |

АППАРАТНЫЕ СРЕДСТВА ВСТРОЕННЫХ СИСТЕМ 7 страницаИсточник сигнала (драйвер). Выход элемента схемы формирует сигнал на проводнике, подсоединенном к этому выходу, он является источником сигнала в этой точке схемы. Когда несколько выходов элементов подсоединяются проводниками в одну точку схемы, то получается, что для этой точки схемы имеется несколько источников сигналов. Результирующий сигнал в этой точке схемы формируется как результат выполнения (на физическом уровне) некоторых преобразований над сигналами, сформированными всеми источниками. Вид выполняемого преобразования зависит от элементной базы, используемой в устройстве, и определяется решающей функцией. В описании каждого сигнала указывается его имя, тип (необязательные части описываются в квадратных скобках):

signal имя1,имя2, …, имяN: идентификатор_типа[:=начальное значение]; Например: signal flag: bit:=’1’; Процессы являются базовыми конструкциями для задания поведения архитектуры с учетом параллельности выполняемых действий. Процессы выполняются параллельно относительно друг друга, а действия внутри тела процесса выполняются последовательно. Выполнение процессов осуществляется в соответствии с изменением значений сигналов. Описание процесса имеет следующий синтаксис:

[метка_процесса:] process [(список_сигналов)] [is] [декларативная_часть_процесса;] begin последовательные_операторы; end process [метка_процесса]; «Список_сигналов» в круглых скобках называется списком чувствительности. Если в описании процесса задан список чувствительности, то процесс активизируется при изменении значения любого из этих сигналов. Если список чувствительности отсутствует, то процесс активизируется при изменении любого сигнала в модели, если не указано иное с помощью операторов ожидания внутри самого процесса. Для синтеза список чувствительности не имеет значения. Когда по программе на VHDL выполняется синтез, для процесса синтезируется фрагмент схемы, использующий все сигналы, указанные в теле процесса, т.е. синтезирующий компилятор игнорирует список чувствительности.  В результате, преобразования сигналов, заданные процессом, в синтезированной схеме выполняется всегда при изменениях любых сигналов, в то время как в программе-модели на VHDL эти преобразования не выполняются, если не было изменений из списка чувствительности. Это является одной из типовых причин расхождения результатов моделирования до синтеза (по программе-модели) и после синтеза (по синтезированной схеме). В секции «декларативная_часть_процесса» могут включаться описания локальных констант, типов и переменных, используемых в процессе. Сигналы не могут быть описаны как локальные данные процесса. Когда в ходе моделирования процесс активизируется, его выполнение начинается с первого оператора, указанного в теле процесса (секция последовательные операторы). В этой секции располагаются последовательные операторы, которые определяют будущие значения сигналов на базе текущих значений. Кроме того, в теле процесса, как в обычных последовательных программах на языках высокого уровня, для изменения последовательности выполнения могут использоваться последовательные управляющие операторы. В комбинационных схемах, где выходные сигналы зависят только от входных сигналов, любое изменение входного сигнала может привести к изменениям выходных сигналов. Для синхронных последовательных схем тактовый сигнал определяет моменты, в которые только и могут быть считаны входные сигналы, влияющие на функционирование схемы, или же выданы новые значения выходных сигналов. Программные конструкции, соответствующие в модели схемам такого рода, их параллельные операторы могут запускаться на выполнение только в некоторые моменты модельного времени (или при определенных событиях, например, при выполнении условий, определяемых для некоторой совокупности входных сигналов). Можно было бы применить тот же принцип управления запуском процессов – список чувствительности, но это часто приводило бы к выполнению очевидно лишних циклов моделирования, тем самым существенно его замедляя. Для исключения этого в VHDL введен оператор ожидания wait. Оператор wait позволяет управлять моментами времени, в которые параллельные операторы будут реагировать на изменения сигналов. Операторы ожидания имеют следующий синтаксис:

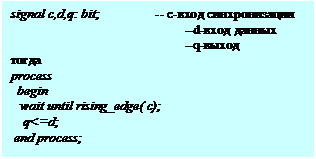

wait [on имя_сигнала {, …}] [until булево_выражение] [for выражение_времени] ; Оператор wait позволяет приостановить выполнение параллельного оператора в модели и программно задавать условия, при которых его выполнение может быть возобновлено. Как только заданные условия будут выполнены, процесс продолжит свое выполнение. Для синтеза используется секция until, позволяющая определить булево выражение, которое должно иметь значение true (для того, чтобы процесс продолжил выполнение после этой инструкции). Если же в момент выполнения оператора wait условие уже имело значение true, то выполнение процесса будет продолжено только после того , как заданное условие сначала примет значение false, потом вновь значение true. Рассмотрим модель синхронного (по фронту) D-триггера. Пусть:

Конструкция wait until приостанавливает выполнение процесса до выполнения условия, задающего передний фронт импульса с. Новое значение присваивается сигналу только в момент завершения процесса, а оно отложено до момента прихода переднего (восходящего) фронта импульса сигнала с. Если событие уже произошло в момент срабатывания процесса, то условие в wait until истинно, и процесс завершается без остановки.

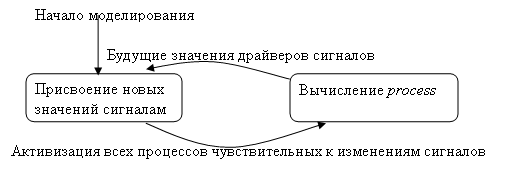

1.10.2.4. Цикл моделирования VHDL В соответствии со стандартом [20] выполнение модели в VHDL описывается следующим образом. Выполнение модели состоит из фазы инициализации с последующим повторяющимся выполнением операторов process и параллельных операторов присвоения, описанных в модели. Каждое такое повторение называется циклом моделирования. В каждом цикле вычисляются значения сигналов, присутствующих в описании. Если в результате вычисления данный сигнал меняет свое значение, то оператор process чувствительный к этому сигналу будет выполнен как часть цикла моделирования. В фазе инициализации, оговоренные начальные значения присваиваются сигналам, текущему модельному времени Tc присваивается значение 0 и однократно выполняется каждый оператор process. Каждый цикл моделирования начинается с установки текущего времени в следующий момент времени, на который назначены изменения значений сигналов. Это время Tn было вычислено во время инициализации или последнего выполнения цикла моделирования. Моделирование прекращается, когда текущее время достигнет установленного максимума. Каждый цикл моделирования содержит следующие шаги: а) Tc присваивается Tn. б) Каждый сигнал явно заданный в модели обновляется (в результате могут появиться события, если сигналы меняют свое значение). В цикле, предшествовавшем текущему циклу, были вычислены новые будущие значения. Если Tc соответствует времени, в которое эти значения становятся действительными, то они и присваиваются сигналам. Новые значения никогда сразу не присваиваются в выполняемом цикле моделирования. Сигналы, которые изменяют свое значение, генерируют события, которые в свою очередь могут запустить выполнение операторов process, чувствительных к этим сигналам. в) Для каждого process P, если P чувствителен к сигналу S и если событие имеет место для сигнала S в этом цикле моделирования, тогда P выполняется. г) Каждый process, который получил разрешение на выполнение в текущем цикле выполняется до момента простановки. д) Время следующего цикла Tn определяется установкой его в наиболее раннее из значений: 1)TIME’HIGH – время окончания моделирования. 2) Время, когда драйвер сигнала становится активным (задержка формирования значения сигнала). 3) Время, в которое разрешается выполняться оператору process (это время определяется операторами wait for. Если Tn = Tc, то следующий цикл моделирования будет δ-циклом. На рис.53 иллюстрирует итеративную природу цикла моделирования. Итак, принцип продвижения модельного времени системой моделирования формулируется следующим образом: от момента события до следующего момента модельного времени, в котором происходит хотя бы одно событие, пропуская промежуточные моменты, в которые не происходит никаких событий. В системах моделирования это называют событийным моделированием.

Рис.53. Цикл моделирования VHDL

Транзакция. В реализации сигналов, изменяемых в модельном времени, основным становится планирование в этом времени изменений сигналов. При выполнении операторов присваивания значения сигналу, системой моделирования формируется специальная структура данных, пара: значение сигнала/момент модельного времени, когда сигнал примет это значение. Такая пара в VHDL называется транзакцией. Транзакция – это внутренняя инструкция системы моделирования по изменению указанного сигнала в заданный момент модельного времени. В реализации языка VHDL запланированная источником временная диаграмма сигнала представляется упорядоченным списком транзакций, формирующих моменты изменения сигнала на временной диаграмме. Часто в описании VHDL именно этот список, связанный с одним источником сигнала называют драйвером.

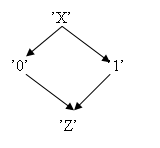

1.10.2.5. Многозначная логика и стандарт IEEE 1164 Во многих случаях может быть целесообразным или необходимым использовать для моделирования цифровых устройств логику с числом значений больше двух. Например, в системе могут бать электрические сигналы различной «силы», и может потребоваться вычислить «силу» и логический уровень в результате соединения двух или более таких источников сигналов. Использование дискретного множества «сил» позволяет избежать необходимости решать уравнения Кирхгофа и получить результат с требуемой точностью. Сигнал с одной силой (две логических величины). Это простейший случай с двумя логическими значениями ‘0’ и ‘1’ и одной силой для каждого значения означает, что если соединить сигналы один со значением ‘0’, а другой со значением ‘1’, то ничего не будет известно об уровне результирующего сигнала. Сигнал одой силы достаточен для систем, в которых нет таких соединений. Сигнал с двумя силами (три или четыре логических величины). Во многих схемах некоторый проводник может быть не соединен с землей, источником питания или с другим узлом схемы. Например, могут содержать схемы с открытым коллектором (истоком), или для выхода с тремя состояниями (‘0’, ‘1’ и ’Z’) при одном из вариантов управления оба транзистора закрыты (не проводят, т.е. Z состояние). В результате выход будет отключен от полюсов источника. Очевидно, что сила сигнала у отключенных таким образом выходов меньше в состоянии ’Z’ по сравнению с ‘0’ и ‘1’. Если сигнал со значением ’Z’ соединен с другим сигналом, то этот другой сигнал будет доминировать. Функцию, выполняющую вычисление результирующей величины при таких соединениях, называют функцией разрешения. Во многих случаях трехзначное множество значений {’0’,’1’,’Z’} дополняется значением ’X’, представляющем неизвестную величину такой же силы как ‘0’ и ‘1’. Функция разрешения для этого случая получается весьма простой и может быть наглядно представлена с помощью схемы частичного порядка, как на рис. 54. Определим операцию sup над двумя сигналами, которая возвращает верхнее значение двух сигналов. Верхнее значение c двух сигналов a и b является наислабейшей величиной, для которой сохраняется c ≥ a и c ≥ b. Например, sup (’Z’, ’0’)=’0’, sup(’Z’,’1’)=’1’.

Рис. 54. Граф частичного порядка для значений из множества {’0’,’1’,’Z’, ’X’}

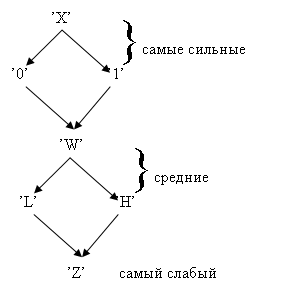

Сигнал с тремя силами (семь логических величины). Во многих случаях двух сил сигналов недостаточно, например, когда верхний МОП транзистор комплиментарного каскада является транзистором с обеднением. Эффект от этого транзистора подобен резистору низкой проводимости на пути к источнику питания (протекает маленький ток). Этот транзистор вместе с нижним транзистором управляют величиной выходного сигнала схемы, которая может быть вычислена с помощью функции разрешения. Нижний транзистор обеспечивает выход значениями ’0’ или’Z’. Транзистор с обеднением обеспечивает значение сигнала слабее, чем для ’0’ и ’1’, а его уровень соответствует ’1’. Это значение транзистора с обеднением обозначают, как ’H’ – слабая логическая ’1’. Подобным образом определяется слабый логический ’0’ - ’L’, результат взаимодействия слабых сигналов – слабая логическая неопределенность, обозначаемая как ’W’. В результате получаем три силы и семь значений величины сигнала {’0’, ’1’, ’L’, ’H’, ’W’, ’X’, ’Z’}. Граф частичного порядка представлен на рис. 55.

Рис. 55. Граф частичного порядка для значений из множества {’0’, ’1’, ’L’, ’H’, ’W’, ’X’, ’Z’}.

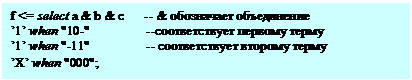

В VHDL предопределена только двузначная логика (тип dit). Поэтому был разработан стандарт IEEE 1164, содержащий девять значений {’0’, ’1’, ’L’, ’H’, ’X’, ’W’, ’Z’, ’U’, ’-’}, где ’U’ обозначает неинициализированное значение, используемое при моделировании сигналов без точной инициализации. Символ ’-’ обозначает «беззаботный вход» или вход не имеет значения для описания булевых функций. В качестве примера рассмотрим условный параллельный оператор присвоения сигнала select подобный операторам switchи case языков программирования.

Это должно легко моделироваться. К сожалению, получим не то, что хотели. Всякий раз, когда средства разработки VHDL оценивают подобный оператор, они проверяют выражение в пункте select (в примере a & b & c) на значения из пунктов when, в частности "10-". Т.к. значение ’-’ никогда не присваиваются сигналам эта проверка никогда не даст истины. Приведенное нереализуемое удобство плата за гибкость введения девятизначного множества значений, но все-таки стало можно моделировать схемы с обедненными МОП транзисторами.

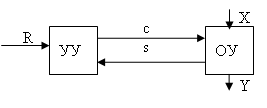

1.11. Проектирование устройств ввода-вывода и контроллеров интерфейсов ввода-вывода по модели программно-управляемого автомата. Поведенческий уровень является наивысшим уровнем абстракции поддерживаемым VHDL. Создание поведенческого описания устройства ведется в терминах операций, выполняемых во времени. Концепция времени является важным отличием между поведенческим описанием и низкоуровневым описанием. Примеры поведенческих форм представления могут содержать диаграммы состояний (графы переходов), временные диаграммы и алгоритмические описания. В поведенческом описании концепция времени может быть выражена точно с помощью требуемых задержек между событиями или просто упорядочиванием выполнения операций. При создании проектов на VHDL для синтеза можно использовать поведенческие операторы, предполагая наличие регистров в устройстве. Необходимо иметь в виду, что современные средства синтеза игнорируют временные спецификации, оставляя реальные временные результаты на милость целевой технологии устройства. Синтезаторы также не способны поддерживать широкий спектр стилей описания. Для тех, кто имеет дело с разработкой программного обеспечения, написание проектов на поведенческом уровне VHDL не будет казаться как что-нибудь новое. Разница состоит в базовой исполнительной платформе: в случае программного обеспечения все исполняет CPU; в случае VHDL исполнителем является симулятор или синтезированная аппаратура. На поведенческом уровне описание может выполняться в виде алгоритма, потока данных или простых булевых выражений. На алгоритмическом уровне абстракции схема описывается в терминах последовательных операторов без привязки к тактовой частоте и деталей задержек преобразований. Временной аспект выводится из порядка операций в алгоритме. Некоторые инструменты синтеза допускают на входе такое представление, однако, требуют наличие конструкции типа «тактовая частота алгоритма» для синхронизации операций. Основными компонентами цифровых систем являются регистры. На уровне абстракции потока данных описывается перемещение данных между регистрами схемы. Поэтому этот уровень часто называют уровнем регистровых передач (RTL - register transfer level). Это промежуточный уровень позволяет упростить рутинную работу с комбинационной логикой (отдать ее средствам синтеза) и сконцентрироваться на более полной спецификации регистров, как наиболее важной части схемы. В RTL описании присутствует точное задание тактовой частоты. Операции планируется выполнять в специфическом тактовом периоде, но не детализируются задержки внутри периода. Глобальная тактовая частота не является обязательным элементом, но может быть предпочтительной. Дополнительной особенностью может быть коррекция синхронизации, позволяющая перепланировать операции. Для проектирования сложных цифровых устройств часто применяют модель программно-управляемого автомата (ПУА) [16]. ПУА состоит из устройства управления (УУ) и операционного устройства (ОУ), как показано на рис. 56.

Рис.56. Программно-управляемый автомат

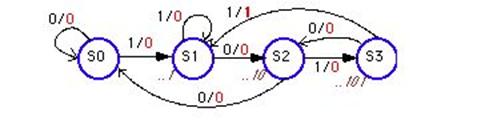

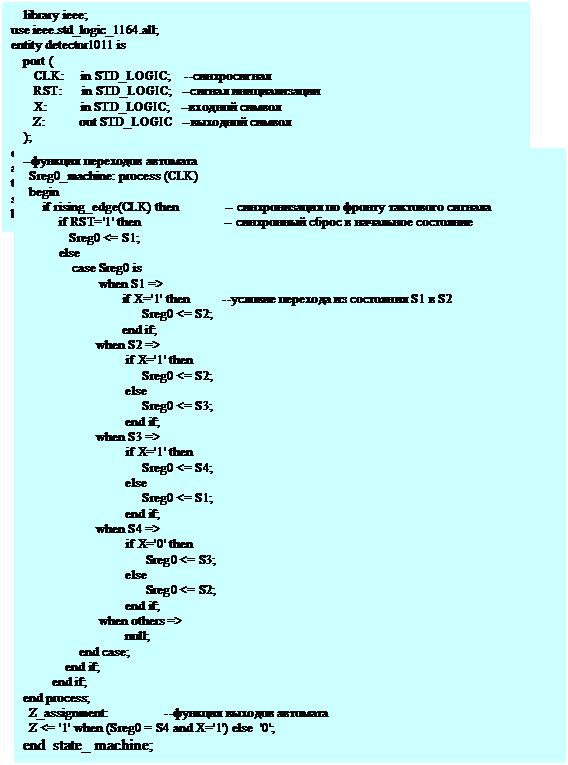

Первое свойство этой модели гласит, что операционное устройство задается на уровне RTL, а устройство управления задается на алгоритмическом уровне (в частности конечным автоматом). Второе свойство утверждает, что ПУА является рекурсивной моделью. Это означает, что УУ может представлено в виде ПУА1 (ОУ1, УУ1), УУ1 в виде ПУА2 (ОУ2, УУ2) и так далее. На ОУ определено множество микроопераций (МО), выполняющих преобразование входных сигналов X из окружающей среды в выходные сигналы Y для окружающей среды. Выполнение той или иной МО инициируется выходными сигналами c УУ, зависящими от состояния УУ, его входов R и s. Сигналы s характеризуют результаты выполнения операций в ОУ, а R – управляющие воздействия окружающей среды. Рассмотрим пример описания для синтеза синхронного автомата Мили, реализующего детектор входной последовательности 1011 [21]. На рис. 57 представлена его диаграмма состояний, а ниже текст на VHDL.

Рис. 57. Диаграмма состояний детектора последовательности 1011, реализующая автомат Мура

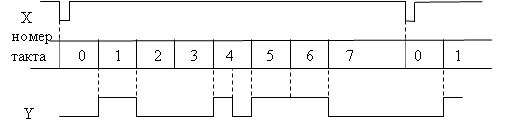

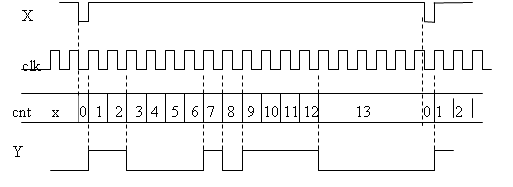

Разработка описание на VHDL ОУ базируется на задании временной диаграммы устройства. Пусть необходимо разработать синхронное устройство, на выходе Y которого формируется последовательность из трех импульсов в ответ на входной импульсX, как показано на рис.58 (выходные импульсы сопоставлены с тактами работы устройства).

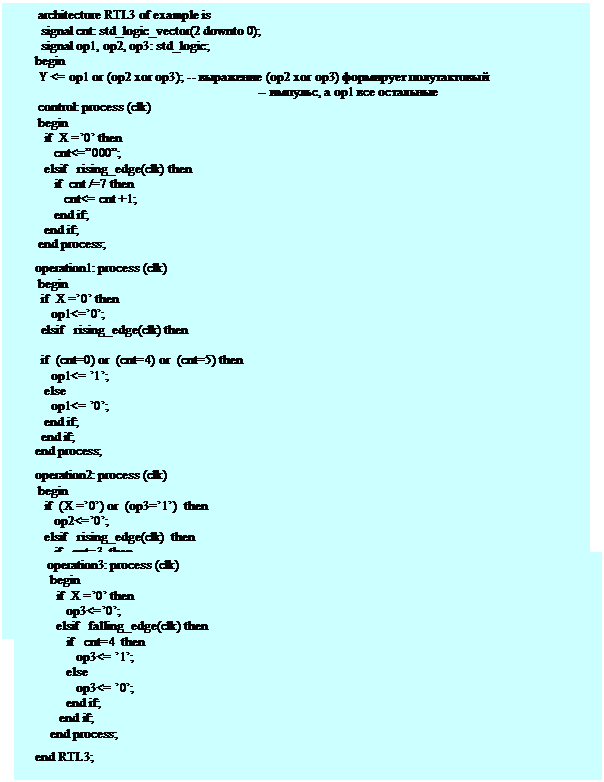

Возможны различные варианты реализации архитектуры. Рассмотрим первый вариант, основанный на организации механизма нумерации тактов. Для этого потребуется двоичный счетчик. В синхронных устройсвах изменение состояния элемента памяти может происходить либо только по фронту синхросигнала, либо только по его срезу. Потому изменения таких сигналов может происходить через минимальное время равное длительности периода тактового интервала. Для формирования полутактовых интервалов необходимо увеличить вдвое частоту тактового сигнала. На рис.59 приведена временная диаграмма работа устройства (ниже текст на VHDL). Сигнал cnt представляет четырехразрядный двоичный счетчик, изменяющий свое состояние по фронту синхросигнала clk. Длительность clk составляет половину длительности исходного такта. Рис.59. Временная диаграмма первого варианта описания

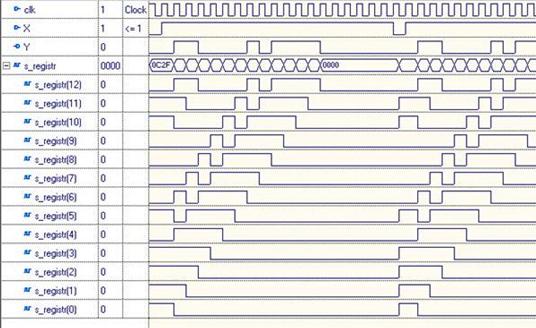

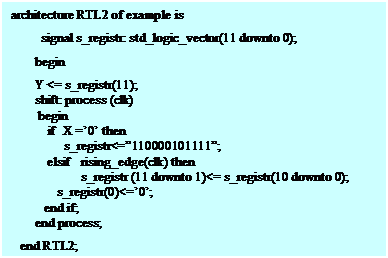

Второй вариант реализации архитектуры основан на сдвиговом регистре s_registr, выполняющем роль одноразрядной памяти магазинного типа. Эта память по сигналу Х запоминает по тактам временную диаграмму для сигнала Y, подключенного к старшему разряду s_registrt(11) (это реализует параллельный оператор присвоения Y <= s_registrt(11);), далее выполняется сдвиг s_registrt в сторону старших разрядов по фронту clk. На рис.60 приведена временная диаграмма работы этого варианта описания устройства, а ниже текст на VHDL.

Рис.60. Временная диаграмма второго варианта описания

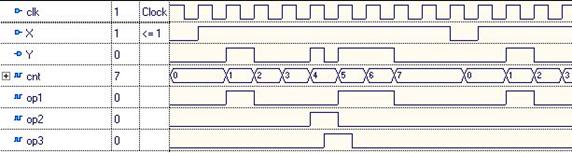

Третий вариант реализации архитектуры, в котором частота clk в два раза меньше чем в предыдущих двух вариантах. Для формирования полутактовых интервалов, поэтому потребовалось ввести три однобитных вспомогательных сигнала op1, op2, op3, разрядность cnt уменьшилась с четырех до трех разрядов. На рис.61 приведена временная диаграмма работы этого варианта описания устройства, а ниже текст на VHDL

Рис.61. Временная диаграмма третьего варианта описания

Сравним эти три варианта описания с точки зрения аппаратных затрат и требований к быстродействию при реализации на FPGA. Последний вариант может быть реализован на более медленных FPGA, т.к. требуется частота в два раза ниже остальных. Для первого варианта потребуется 5 триггеров, для второго 13, а для третьего 6. Описание второго варианта самое компактное, а у третьего самое громоздкое. Наличие вариантов реализации даже для простого устройства лишний раз подтверждает, что проектирование продолжает оставаться искусством.

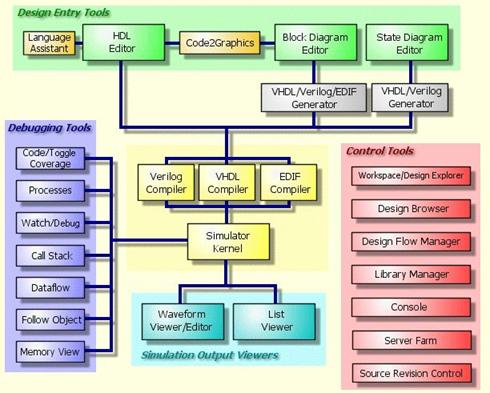

1.12. Интегрированная среда разработки аппаратных средств Active-HDLTM Автоматизированное проектирование — это магистральное направление развития технологий создания электронной аппаратуры [22]. До недавнего времени образцом решения таких задач считались разработки на базе серийно выпускаемых стандартных интегральных микросхем, и большинство САПР ориентировались на реализацию именно этой технологии проектирования. Идеальным вариантом казались «сквозные» САПР, которые позволяли выполнить всю цепочку проектирования: от входного описания до создания эскиза печатной платы. Примерами сквозных САПР являются PCAD, DesignLab и OrCAD. В последние годы набирают силу новые технологии проектирования электронной аппаратуры, основанные на современных персональных компьютерах, интегрированных САПР и программируемой логике. Яркий представитель таких САПР нового поколения — это интегрированная среда проектирования Active-HDL. Ее отличает особая легкость и «элегантность» в работе. Фирма ALDEC, создатель этого программного продукта, год от года совершенствует свое детище и наделяет его новыми возможностями. Продукт Active-HDL является самым популярным среди разработчиков цифровой аппаратуры интегрированной средой разработки для проектирования цифровых схем, созданных с помощью языков описания оборудования VHDL, Verilog/SystemVerilog, EDIF и SystemC. Она содержит инструменты для входа в систему, компиляторы VHDL и Verilog, отдельное ядро моделирования, несколько стандартных и продвинутых инструментов отладки, программы просмотра результатов моделирования в графической и текстовой форме. Также содержит вспомогательные утилиты для упрощения управления ресурсными файлами, проектами и библиотеками проектов; также встроенные интерфейсы для запуска моделирования, синтеза, управления версиями исходных файлов, взаимодействия со средствами поддержки моделей сторонних производителей. На рис. 62 показаны инструменты и компоненты Active-HDL.

Рис. 62. Инструменты и компоненты Active-HDL

Console (Консоль). Окно консоли является интерактивным механизмом для ввода макрокоманд Active-HDL и пользовательских скриптов, вывода сообщений, генерируемых инструментами Active-HDL. Workspace/Design Explorer (Анализатор рабочей области/проекта) позволяет администрировать проекты Active-HDL, так что нет необходимости беспокоится о месте нахождения файлов на компьютере. Design Browser (Программа просмотра проекта). Окно просмотра показывает содержимое текущего проекта: - ресурсные файлы, прикрепленные к проекту, - рабочие библиотеки по умолчанию, - структуру узла, выбранного для моделирования, - VHDL, Verilog, и EDIF объекты, объявленные внутри выбранной области текущего проекта. Design Flow Manager (Менеджер процесса проектирования) помогает автоматизировать обработку Active-HDL проектов. Он показывает типовую последовательность проектирования в форме диаграммы. Встроенные в диаграмму программные кнопки вызывают приложения, участвующие в преобразованиях. Language Assistant (Языковый помощник ) является вспомогательным инструментом для представления шаблонов логических примитивов и функциональных блоков. Он интегрирован с редактором HDL, так что можно автоматически вводить требуемые шаблоны в редактируемый исходный файл. Языковый помощник также позволяет определять собственные шаблоны пользователя. HDL Editor (Редактор HDL) – это тестовый редактор. Он индицирует специфические синтаксические категории различными цветами. Редактор неразрывно интегрирован с симумятором для получения возможности отлаживать исходный код. State Diagram Editor (Редактор диаграммы состояний) – это графическое средство разработано для редактирования графов переходов автоматов. Редактор автоматически транслирует графически спроектированный граф в VHDL или Verilog код. Waveform Viewer/Editor (Программа просмотра/редактирования временной диаграммы) показывает результаты моделирования в виде временной диаграммы. Она дает возможность графической редакции временной диаграммы как требуемых тестовых векторов. Block Diagram Editor (Редактор блок-диаграмм) является графическим инструментом для создания блок-диаграмм. Он автоматически транслирует графически представленную схему в VHDL или Verilog код. Окно List (Список) показывает результаты моделирования в табличном текстовом формате. Это позволяет выполнять трассировку результатов с точность до дельта-цикла. Окно Watch (Наблюдение) показывает текущие значения выбранных объектов VHDL или Verilog во время моделирования. |

||||||||||||||

|

Последнее изменение этой страницы: 2018-04-12; просмотров: 376. stydopedya.ru не претендует на авторское право материалов, которые вылажены, но предоставляет бесплатный доступ к ним. В случае нарушения авторского права или персональных данных напишите сюда... |

Пусть необходимо представить булеву функцию f (a,b,c) = ab’+bc, неопределенную для случая a=b=c=’0’. Наиболее удобный способ представлен ниже:

Пусть необходимо представить булеву функцию f (a,b,c) = ab’+bc, неопределенную для случая a=b=c=’0’. Наиболее удобный способ представлен ниже: