Студопедия КАТЕГОРИИ: АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция |

АППАРАТНЫЕ СРЕДСТВА ВСТРОЕННЫХ СИСТЕМ 6 страницаТопология шины USB – “монтажная звезда” (tiered star) или дерево, наращиваемое с помощью концентраторов (hub). USB хост-порт (один на всю шину) содержит корневой хаб и приемопередатчики (трансиверы) для подключения новых хабов или устройств (device). Кабель состоит из 4 проводников: Vbus – питание +5В, GND – земля и свитые D- и D+ - дифференциальная пара для полудуплексной передачи данных. Определение скоростных характеристик устройства и самого факта подключения его на шину производится с помощьюя имеющихся в устройстве подтягивающих резисторов, подключенных к линии D- или D+. Подключение к линии D+ сигнализирует подключение полноскоростного устройства, а к D- – низко скоростного. Данные передаются самосинхронизирующимся кодом NRZIspace с битстаффингом. Текущая 1 передается инверсией потенциала предыдущего бита, текущий 0 передается потенциалом предыдущего бита. Длинные последовательности нулей исключаются из передачи вставкой 1 после n подряд идущих 0. Передаче кадра предшествует передача преамбулы – последовательности длины m из одних 1, обеспечивающей вхождение в работу выделителя тактовой частоты на приемной стороне. Интерфейс USB полностью контролируется хостом (ведущим) шины, который может быть только один. Устройства USB (ведомые) только отвечают на запросы хоста и не могут по собственной инициативе начать передачу. Каждое устройство на интерфейсе USB может имеет несколько конечных точек (ep – end point). Эти пронумерованные точки являются окончаниями логических каналов данных между хостом и устройством. Таким образом, между хостом и устройством реализуется многоканальная передача данных.  При подключении устройства к шине хост присваивает ему номер. Номера ep задаются при изготовлении у стройства. Любое устройство должно поддерживать ep 0 (DCP - Default Control Pipe), так как это средство конфигурирования устройства по умолчанию в USB после включения или получения сигнала сброса по шине. Конечные точки имеют собственные характеристики, их необходимо знать клиентскому программному обеспечению (ПО) для определения типа соединения: частота передачи, требования по пропускной способности канала, номер ep, требования по обработке ошибок, максимальный размер пакета отправляемого/принимаемого ep, тип и направление передачи. Передача по USB состоит из пакетов, отмеченных специальными кодами, называемыми идентификаторами пакетов (PID). PID показывает какого типа пакет был передан. Рис.43. иллюстрирует передачу по USB от хоста к устройству.

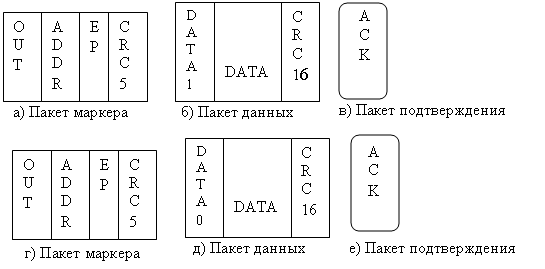

Рис.43. Пример передачи по USB от хоста к устройству Пакет а) – признак передачи, индицируемый OUT PID. Признак индицирует, что данные от хоста будут переданы по шине. Пакет б) содержит данные, о чем говорит PID DATA1. Пакет в) – квитирование (handshake), отправляется устройством с использованием ACK PID для подтверждения хосту, что устройство получило данные без ошибок. Вторая передача начинается с еще одного пакета OUT г). Далее следуют данные д), на этот раз с PID DATA0. В конце передачи устройство опять подтверждает успешную передачу, передавая ACK PID. Наличие DATA1 и DATA0 (два циклических номера пакетов) обусловлено коррекцией ошибок. Пакет ACK – это сигнал хосту, что периферия получила данные без ошибок (поля CRC в пакетах используются для определения ошибок). Каждая сторона устанавливает переменную, изменяющуюся между DATA1 и DATA0. Значение этой переменной сравнивается с полем PID, приходящим с данными, DATA1 или DATA0. При передаче данных хост или устройство посылает перемежающиеся пакеты DATA1 - DATA0. Путем сравнения идентификатора DATA со значением внутренней переменной, хост или устройство могут определить поврежденный пакет. Признак SETUP предназначен для передачи типа CONTROL. Они предваряют 8 байт данных, из которых периферия определяет запросы хоста. Признак SOF приходит каждую миллисекунду, обозначая кадр USB. Пакеты согласования: – ACK означает, что данные приняты без ошибок. – NAK означает занято, передайте еще раз. – STALL означает, что произошло нечто непредвиденное. Устройство посылает STALL , показывая, что не поняло запрос. – PRE предшествует передаче на низкой скорости. Передаче данных хосту предшествует пакет IN. Если хост не посылает этот запрос, данные навсегда останутся в буфере устройства. Пакет SOH обеспечивает распределение времени и включает в себя 11-разрядный счетчик кадров. Возможны четыре типа передач: Передача типа Bulk – “прорывная”, пакетами по 8, 16, 32, 64 байт. Доставка информации гарантирована по причине автоматической пересылки поврежденных данных. Хост позволяет передавать пакеты bulk, когда шина освобождается. Этот тип передачи применяется для принтера, сканера или модема. Данные, передаваемые таким способом, имеют встроенный контроль передачи, обеспечиваемый пакетами согласования. Передача типа Interrupt похожа на bulk, но передача происходит только для IN каналов. Блок данных может иметь длину от 1 до 64 байт. Каналы interrupt типа имеют ассоциированный временной интервал, через эти интервалы хост посылает признак IN. Передача типа Isochronous используется для потоковой передачи, критичной ко времени информации, такой как аудио или видео информация. В каждом кадре USB определенная жесткая часть времени отводится для передачи типа isochronous. Такая передача не имеет признаков согласования и не имеет пересылок. Передается всегда PID DATA0. Передача типа Сontrol используется для конфигурирования и посылки команд устройству. При передаче типа сontrol обеспечивается наилучшая защита от ошибок. Хост резервирует часть каждого фрейма для передачи сontrol. Передачи сontrol состоят из 2 или 3 стадий. Стадия SETUP содержит 8 байт управляющих данных. Необязательная часть DATA содержит дополнительные данные. Стадия STATUS позволяет устройству индицировать благополучное завершение процесса конфигурирования.

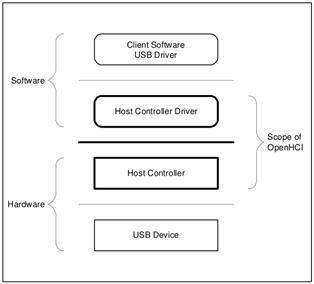

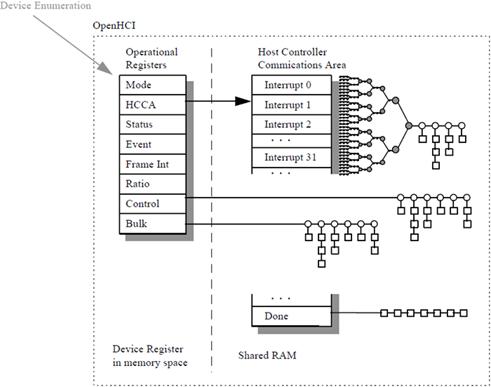

1.9.4.2. Интерфейс Open Host Controller для USB Спецификация интерфейса Open Host Controller (OpenHCI) для USB является описанием на уровне регистров хост контроллера шины USB, который в свою очередь описывается спецификацией USB выпущенной корпорацией Intel. Интерфейс OpenHCI позволяет разрабатывать хост контроллеры с общим программным интерфейсом, тем самым освобождаясь от написания и распространения драйверов к ним. Целью разработки OpenHCI было подобрать оптимальный баланс между сложностью оборудования и программного обеспечения, так, чтобы хост-контроллер шины USB, соответствующий спецификации OpenHCI, был наиболее простым и при этом имел максимум функционала [15]. Современные μC поддерживают OpenHCI. На рис. 44 показаны четыре основные составляющие USB. Это Клиентское ПО (Драйвер USB), Драйвер Хост Контроллера (HCD), Хост Контроллер (HC), и USB-устройство. Драйвер USB и Драйвер Хост Контроллера реализован на программном уровне. Хост Контроллер и USB-устройство реализован на аппаратном уровне. Спецификация OpenHCI определяет интерфейс между драйвером хост контроллера и хост контроллером, а так же описывает основы работы каждого из них. Существует два канала взаимодействия между хост контроллером и драйвером хост контроллера (рис. 45). Первый канал - это набор регистров хост контроллера. Хост-контроллер является ведомым на этом канале (сам только принимает события). В набор регистров входят управляющие и статусные регистры, а так же регистры, в которых хранятся указатели на списки дескрипторов. В наборе регистров есть регистр, хранящий указатель на область в разделяемой памяти, называемую Host Controller Communications Area (HCCA). Область HCCA является вторым каналом взаимодействия. Хост контроллер является ведущим на этом канале (сам только генерирует события). HCCA содержит указатели на заголовки списков дескрипторов конечных точек типа Interrupt, указатель на заголовок очереди обработанных дескрипторов передачи (done queue), а так же статусную информацию, связанную с обработкой признака начала кадра.

Рис. 44. Основные составляющие системы USB

Рис. 45. Каналы взаимодействия

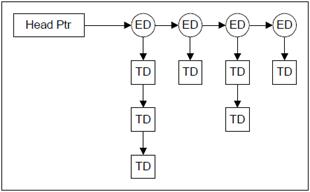

Основными структурами данных при взаимодействии с интерфейсом хост контроллера являются дескрипторы конечных точек (ED) и дескрипторы передачи (TD). Драйвер хост контроллера ассоциирует с каждой конечной точкой, доступной в системе, дескриптор конечной точки. Дескриптор конечной точки содержит информацию, необходимую хост контроллеру для связи с ассоциированной конечной точкой. Дескриптор включает в себя поля, содержащие максимальный размер пакета, адрес конечной точки, её скорость и направление потока данных. Дескрипторы конечных точек хранятся в списках. С каждой конкретной конечной точкой связана очередь дескрипторов передачи. Дескриптор передачи содержит информацию, описывающую пакеты данных, которые будут переданы конечной точке. Дескриптор передачи включает в себя поля, содержащие информацию о триггере данных, адрес буфера в разделяемой памяти и коды статуса завершения передачи. Каждый дескриптор передачи содержит информацию, которая описывает один или несколько пакетов данных. Буфер данных каждого дескриптора передачи может иметь размер в диапазоне от 0 до 8192 байт и иметь максимум один переход через границу физической страницы памяти. Дескрипторы передачи связаны между собой с помощью очередей, обрабатываемых по принципу: первым пришёл, первым обработан. Каждый тип передачи данных имеет свой собственный список дескрипторов конечных точек, подлежащих обработке. На рис. 46 приведена типичная структура списков, которая отображает взаимосвязи между структурами данных. Указатели на заголовки списков конечных точек типа bulk и control хранятся в регистрах хост контроллера. Драйвер хост контроллера инициализирует эти указатели до того, как хост-контроллер осуществит доступ к ним. Если эти указатели понадобится обновить, драйверу хост контроллера, возможно, потребуется остановить обработку хост контроллером определенного списка, обновить указатель, и снова включить хост-контроллер.

Рис. 46. Типичная структура списков

Указатель на заголовок списка дескрипторов конечных точек типа interrupt (вернее, массив указателей) хранится в HCCA. На заголовок списка дескрипторов конечных точек типа isochronous не существует отдельного указателя. Первый дескриптор конечной точки типа isochronous помещается в список сразу после последнего дескриптора конечной точки типа interrupt. Всего доступно 32 указателя на заголовки списков типа interrupt, которые организованны в виде массива. Указатель на заголовок списка, используемый в конкретном кадре, определяется с помощью последних 5 битов счетчика кадров. Эти 5 бит используются в качестве смещения в массиве указателей на заголовки списков. Дескрипторы конечных точек типа interrupt организованы в древовидную структуру, где указатели на списки являются листьями. Требуемый интервал обслуживания конечной точки типа interrupt достигается за счет размещения дескриптора конечной точки на соответствующей глубине в дереве. Наибольшая частота опроса достигается ближе к корню дерева, так как чем ближе узел к корню, тем больше в нем сходится списков. Чтобы увеличить частоту опроса конечной точки, необходимо поместить её в большем количестве списков.

Вопросы для самоконтроля 1. К архитектуре какого типа (Гарвардской или фон Неймана) относится процессор, изображенный на рис.4? 2. Какие элементы входят в понятие архитектуры процессора? 3. В чем разница между регистрами адреса, данных и общего назначения? 4. Какую цель преследовали разработчики архитектуры некоторых процессоров, когда ввели механизм регистровых окон? 5. С какими особенностями процессоров связано понятие когерентности памяти? 6. Как соотносятся прерывания и исключения? 7. Зачем в системе прерываний появилась вторичная система приоритетов? 8. Для каких целей были придуманы механизмы виртуальной памяти и сегментации памяти? 9. В чем особенность коммуникационных процессоров? 10. Какова роль пузырей в конвейере? 11. Какой вариант перекрытия внутренних банков SDRAM более эффективный? 12. Какие усовершенствования преобразовали EEPROM память во флэш-память? 13. В чем отличия блокнотной и кэш памяти? 14. Чему равно значение параметра Е для кэш-памяти с прямым отображением? 15. На что направлено обеспечение когерентности кэш-памяти? 16. В чем суть различия асинхронных магистралей в манерах Intel и Motorola? 17. Какую роль в аналого-цифровом преобразователе играет схеме выборки/хранения. 18. Как в UART выполняется синхронизация на уровне бит? 19. Возможно ли взаимодействие через интерфейс SPI более двух устройств, если да то как?

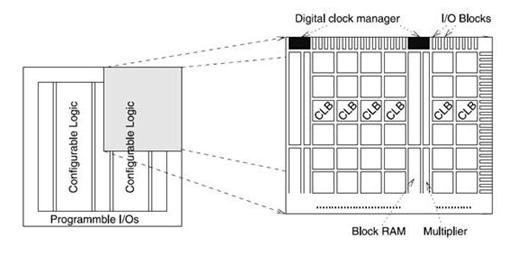

МОДУЛЬ 2 1.10. Язык проектирования аппаратуры VHDL 1.10.1. Реконфигурируемая логика Уже отмечалось, что во многих случаях полностью заказные СБИС (ASIC) дороги, а решения, основанные на программной реализации медленные или энергоемкие. Реконфигурируемая логика обеспечивает решение задачи для случаев, если алгоритмы могут быть эффективно реализованы с помощью заказных СБИС. Такие решения дают почти такое же быстродействие, как и ASIC, но зато реализованные функции могут быть легко изменены конфигурационными данными. Поэтому реконфигурируемая логика находит применение в следующих областях. Быстрое создание прототипа. Современные ASIC очень сложные, требуют больших усилий разработчиков и длительного времени проектирования. Поэтому часто желательно создать прототип, который мог бы быть использован для экспериментов с системой, работающей «почти» как окончательная система. При этом потребляемая мощность может быть больше, временные ограничения смягчены и только определяющие функции соответствуют техническим требованиям. Поэтому прототип может бать использован для проверки основополагающего поведения системы. Малый объем приложений. Если ожидаемый объем рынка мал для оправдания реализации приложения в виде ASIC, а программная реализация была бы медленной или неэффективной, тогда выбор остается за реконфигурируемой логикой. Системы реального времени. Временные характеристики проектов на реконфигурируемой логике обычно хорошо определенны. Поэтому решения получаются с предсказуемым временем выполнения. Микропроцессорные системы. Для встроенных микропроцессорных систем могут потребоваться нестандартные устройства ввода-вывода, интерфейсы или реализация некоторых функций с большим быстродействием. СБИС с названием Field Programmable Gate Array (FPGA, программируемая пользователем вентильная матрица) – наиболее общая форма реконфигурируемой логики. Название подчеркивает, что устройство программируется в пользователем в полевых условиях, т.е. после производства и без особых трудностей. Реконфигурируемая логика часто содержит RAM для хранения конфигурации. Однако RAM является энергозависимой памятью. Поэтому конфигурационные данные должны копироваться в RAM при включении питания из внешней энергонезависимой памяти, такой как ROM или Flash. На рис. 47 в качестве примера приведена схема планировки FPGA Virtex-II фирмы Xilinx [17]. В более поздней FPGA Virtex-5 [18] матрица содержит 240 × 108 конфигурируемых логических блоков (CLB - Configurable Logic Blocks), которые можно соединить, используя программируемую структуру соединений. Матрица также содержит 1200 пользовательских входов-выходов и 1056 блока DSP включающих умножитель 25 × 18 бит и 16416 Кбит RAM блок.

Рис. 47. Схема планировки FPGA Virtex-II

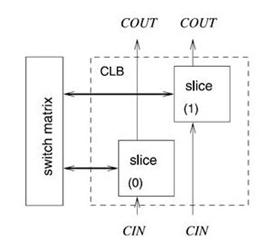

Каждый CLB состоит из двух секций (slice), как показано на рис. 48.

Рис. 48. Virtex-5 CLB

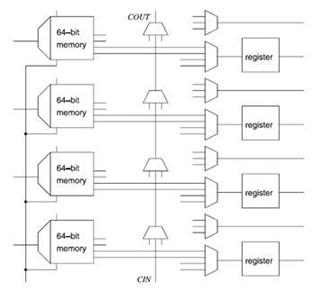

Секция состоит из четырех элементов памяти (рис. 49). Каждый элемент памяти может быть использован как таблица соответствия (LUT - Look-Up Table) для реализации одной 6-входовой логической функций (таких функций 2^64) или двух 5-входовых логических функций (таких функций 2^32), а также сконфигурированы как RAM или сдвиговые регистры (SRL). С помощью мультиплексоров несколько элементов памяти могут быть объединены. Каждая секция содержит еще 4 выходных регистра и специальную логику для реализации быстрых операций арифметического сложения. Конфигурационные данные определяют установки для мультиплексоров, синхронизацию регистров и RAM, содержимое RAM и соединения между CLB. Обычно эти данные генерируются из проектов, написанных, например, на VHDL.

Рис. 49. Упрощенная схема секцииVirtex-5

1.10.2. Введение в VHDL Существует два популярных представителя группы языков HDL (Hardware Description Language), предназначенных для описания цифровых аппаратных средств, это Verilog и VHDL: первый более краткий, менее гибкий, менее приятный; второй многословный, очень гибкий и более приятный. История VHDL восходит к 80-м годам прошлого века. В это время многие системы проектирования использовали графические HDL, когда наиболее общим строительным блоком был логический вентиль. Однако разработчики использовали и текстовые HDL, преимущество которых состояло в простоте представления сложных преобразований с использованием переменных, циклов и рекурсий. По мере усложнения устройств текстовые HDL почти полностью вытеснили графические. Язык VHDL (VHSIC Hardware Description Language) был разработан в рамках программы VHSIC (Very High Speed Integrated Circuits) министерства обороны Соединенных Штатов. В 1987 VHDL приобрел статус стандарта IEEE (IEEE Std. 1076 - 1987). В 1993 после ревизии начальной версии стал VHDL’93, и далее на его основе VHDL’98, VHDL’2000, VHDL’2002, VHDL’2006, VHDL’2008, а подмножество VHDL AMS (Analog Mixed Signal) позволяет описывать как чисто аналоговые, так и смешанные, цифро-аналоговые схемы. При разработке VHDL использовался язык программирования ADA, как отправная точка, т.к. оба языка разрабатывались для министерства обороны. В свою очередь ADA базируется на PASCAL, поэтому VHDL является синтаксическим сленгом PASCAL. Однако синтаксис VHDL более сложный.

1.10.2.1. Программирование на VHDL для моделирования и синтеза [19] Программа на VHDL используется как модель, отражающая некоторое устройство. Система моделирования исполняет программу на VHDL, имитируя работу реального устройства. Поведение устройства представляется в модели через события изменения сигналов и формируемые временные диаграммы сигналов. Наблюдая это поведение, разработчик анализирует свой проект, делает выводы о его правильности. Здесь программа на VHDL рассматривается как модель – VHDL программа-модель. Синтез является обратным процессом. При синтезе программа на VHDL рассматривается как спецификация, детальное описание, исходные данные и требования, по которым должна быть сгенерирована реализация физического устройства на СБИС. Синтезирующие компиляторы САПР по программе на VHDL генерируют реализацию проектируемого устройства. Здесь программа на VHDL выступает как программа-спецификация для синтеза. Не всякая программа-модель может быть использования как программа-спецификация для синтеза. Не для всякой программы на VHDL ее поведение при моделировании будет соответствовать поведению устройства, синтезированного по этой же программе. Поэтому говорят о синтезируемом подмножестве языка VHDL. Имеется в виду та часть конструкций и понятий VHDL, которые могут использоваться в программе-спецификации для синтеза, исключая запрещенные для синтеза конструкции. Однако такого стандартизованного подмножества не существует. Компиляция устройства по VHDL программе-спецификации может использовать разные наборы элементов (элементный базис). Базис реализации может состоять из элементов разного уровня – от вентилей и логических блоков табличного типа (LUT) до макроячеек сложных функциональных блоков – мультиплексоров, регистровых блоков, блоков памяти, умножителей и процессорных ядер. После компиляции производится оптимизация схемы с целью увеличения быстродействия или сокращения аппаратных затрат, уменьшения размеров на кристалле. Оптимизация схемы приводит к ее трансформациям, иногда весьма существенно меняющей структуру, которая просматривается в исходном тексте. Результатом может быть расхождение в поведении модели устройства и поведении реализации устройства, синтезированной по той же программе на VHDL. Разработчик должен учитывать возможность таких трансформаций, когда пишет программу-спецификацию. Те или иные программные конструкции VHDL синтезирующий компилятор может принимать или игнорировать, т.е. данная конструкция, ее секция или атрибут не будут влиять на результат синтеза схемы.

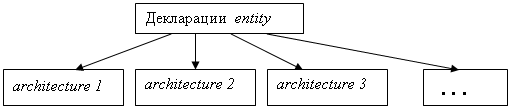

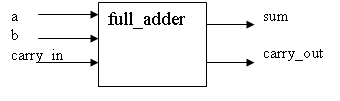

1.10.2.2. Entity и architecture VHDL, как и все HDL, включает необходимые средства для поддержки моделирования одновременной работы аппаратных компонент. Аппаратные компоненты моделируются с помощью конструкции entity. Entity содержит несколько операторов process для моделирования одновременных действий. Entity образуется из двух типов составляющих: декларации entity и одной или нескольких architecture (рис. 50).

Рис. 50. entity состоит из декларации entity и одной или нескольких architecture В качестве примера рассмотрим полный сумматор (full adder) на рис. 51.

Рис. 51. Полный сумматор и его интерфейсные сигналы

Его декларации entity соответствует следующий текст:

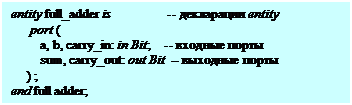

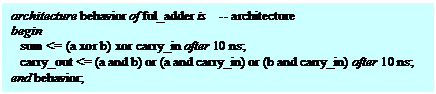

Два дефиса (--) обозначают начало комментария и действуют до конца строки. Architecture состоит из заголовка и тела. Различают два стиля написания архитектурных тел: структурное и поведенческое. Поведенческое тело включает только информацию достаточную для вычисления значений выходных сигналов по значениям входных и состоянию внутренних сигналов. Поведенческое тело full_adder выглядит следующим образом (<= обозначает оператор присвоения значения сигналу):

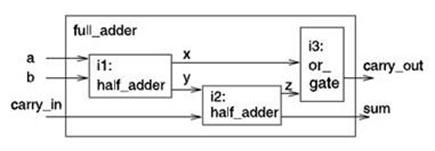

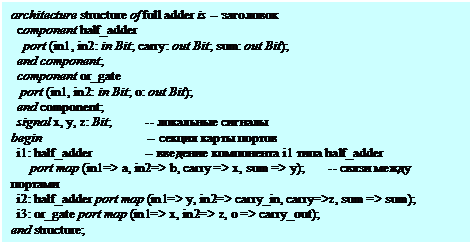

Напротив структурное тело описывает композицию из более простых Entit (рис. 52). В примере компоненты названы от i1 до i3 и принадлежат к типам half _adder или or_gate.

Рис. 52. Схема структурного тела full_adder В текстовом виде эта структура представляется следующим образом:

Конструкции port map описывают связи между локальными компонентами, портами componentипортами entity с помощью символов =>.

1.10.2.3. Операторы присваиваниеи process [19] Цифровые устройства функционируют непрерывно и параллельно. Множество компонентов схемы работают одновременно, формируя значения определенных сигналов. В результате в моделируемом устройстве параллельно, в физическом времени, происходит множество изменений состояния сигналов. Соответственно, и в модели устройства изменения значений сигналов должны производиться параллельно, в модельном времени. Это определяет построение VHDL как языка параллельного по своей природе. Тело архитектурного описания специфицируемого объекта, заключенное между begin и end, содержит совокупность параллельных операторов. Это определяет построение VHDL как языка параллельного по своей природе. Последовательность записи параллельных операторов в теле архитектурного описания значения не имеет. Порядок выполнения определяется не порядком их текстуальной записи, а другими правилами. Основным принципом здесь является управление от потока изменений сигналов, входных для параллельного оператора. Событие изменения сигнала, являющегося входным для параллельного оператора, запускает срабатывание данного оператора. В общем формате описания архитектуры объекта моделирования, секция параллельных операторов содержит один или несколько параллельно выполняемых операторов, с помощью которых задается зависимость выходных сигналов от входных, как по значению, так и по временным соотношениям. В VHDL введен целый ряд параллельных операторов, основными из которых являются процессы и операторы параллельного присвоения значений сигналам. В VHDL существует два вида операторов присвоения значения: переменной и сигналу. Синтаксис оператора присвоения значения переменной:

Идентификатор переменной:= выражение;

Этот оператор присвоения выполняется как в обычных языках программирования. Понятие сигнала не имеет аналогов в традиционных языках программирования высокого уровня типа C, PASCAL и др. Цифровые устройства работают во времени, преобразуя и передавая сигналы. Поэтому понятие сигнала является базовым в VHDL. Сигналы являются абстракцией, представлением в модели на VHDL состояния проводников в структуре цифрового устройства. Физическое время моделируемого устройства непрерывно. Это время, в котором протекают реальные физические процессы, изменяются электрические сигналы в цифровых устройствах, наблюдаемые на логическом уровне как изменение логических состояний. Модельное время – это время в модели устройства. Модельное время является обобщенным представлением физического времени, в котором работает моделируемое устройство. Модельное время дискретно. Время моделирования – это время выполнения программы на VHDL. В семантике программы на VHDL оно напрямую не наблюдается, однако, проявляется через упорядочение операторов программы по времени выполнения. Не имея для программиста на VHDL числовых значений, время работы системы моделирования позволяет определить отношение порядка над событиями – выполнением операторов программы на VHDL. Для каждой пары исполняемых операторов программы определены отношения «выполнен раньше»/«выполнен позже». Изменение сигнала на входе некоторого элемента может привести к изменению сигналы на его выходе, но не мгновенно, а через интервал времени td, определяемый задержкой элемента. Таким образом, подавая сигнал на вход элемента в момент времени t1, мы как бы “запланировали” изменение сигнала на его выходе на время t2=t1+td. В текущий момент физического времени в устройстве одновременно идет множество процессов в разных его элементах и на связях между ними. Процессы в устройстве, которые приведут к изменению сигнала, уже идут, но в измененном состоянии сигнала они проявятся через некоторые промежутки времени. Переменная характеризуется только значением, тогда как сигнал парой значений – значение момента модельного времени/значение уровня сигнала, которое сигнал имеет в этот момент времени. Последовательность значений сигнала в привязке к моментам модельного времени в течение некоторого промежутка времени формирует временную диаграмму сигнала. В модели устройства на VHDL воздействие, изменяющее состояние сигнала, принимает форму присвоения значения сигналу. Параллельный оператор присваивания значения сигналу имеет следующий синтаксис:

Идентификатор сигнала <= выражение; Идентификатор сигнала <= transportвыражение afterвеличиназадержки; Идентификатор сигнала <= выражениеafterвеличиназадержки; Идентификатор сигнала <= rejectвремя inertialвыражениеafterвеличиназадержки;

Оператор присваивания значения сигналу <= включает в себя как определение нового значения сигнала (выражение), так и определение момента времени, в который сигнал примет это новое значение (after величиназадержки). Префиксы transport и inertial используются для представления моделей транспортной и инерциальной задержек. Для оператора присвоения значения сигналу без пункта after (первая форма оператора) изменение сигнала будет иметь место после бесконечно малой величины времени, называемой δ-задежкой, но не мгновенно. Из всех операторов присваивания только этот оператор является синтезируемым. |

||

|

Последнее изменение этой страницы: 2018-04-12; просмотров: 416. stydopedya.ru не претендует на авторское право материалов, которые вылажены, но предоставляет бесплатный доступ к ним. В случае нарушения авторского права или персональных данных напишите сюда... |