Студопедия КАТЕГОРИИ: АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция |

АППАРАТНЫЕ СРЕДСТВА ВСТРОЕННЫХ СИСТЕМ 5 страница

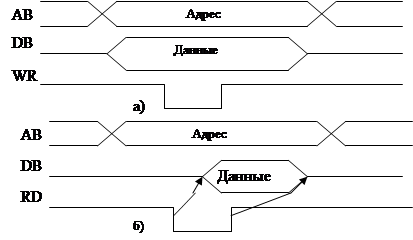

Рис.22. Циклы записи (а) и чтения (б) магистрали

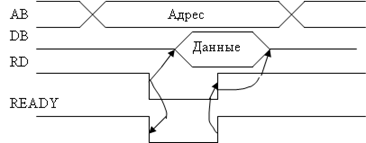

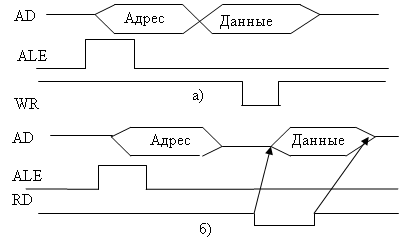

Рис.23. Цикл чтения с подтверждением обмена Рассмотрим простую магистраль со следующим набором сигналов управления в манере Motorola: STB – строб операции на магистрали; W/R – тип операции запись/чтение; ACK – подтверждение операции. На рис.24. приведена временная диаграмма цикла чтения в манере Motorola. По сигналу ACK CPU осуществляет прием данных с шины и завершает цикл магистрали.

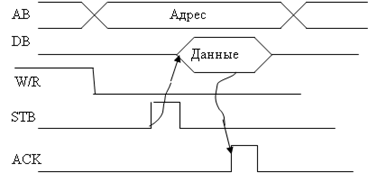

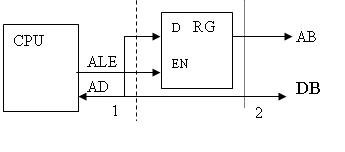

Рис.24. Циклы чтения с подтверждением обмена в манере Motorola. 1.7.2. Двухшинная магистраль В CPU с целью сокращения ширины магистрали вводят совмещенную шину адреса/данных (AD), по которой передаются как адреса, так и данные. Этап передачи адресной информации отделен по времени от этапа передачи данных и стробируется специальным сигналом ALE (Address Latch Enable), который включен в состав CB. На рис.25 представлена временная диаграмма работы такой магистрали.

Рис.25. Циклы записи (а) и чтения (б) двухшинной магистрали

Каждый модуль с двухшинной магистралью содержит локальный адресный регистр для запоминания адресной информации по сигналу ALE. Для фиксации адресной информации может быть использован и один общий регистр, в результате MPS с двумя шинами преобразуется в MPS с тремя шинами, как показано на рис.26.

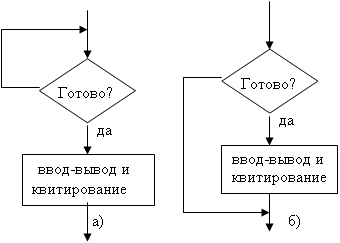

Рис.26. Преобразование магистрали: 1- двухшинная, 2-трехщинная магистраль

1.8. Базовые устройства ввода-вывода встроенных систем Подсистема ввода-вывода ответственна за связь с устройствами ввода-вывода I/O. Каждое I/O в общем случае состоит из двух частей: одна из них называется контроллером, а другая представляет собой само I/O.  С точки зрения программиста подсистему ввода-вывода можно представить или в виде отдельного пространства ввода-вывода (изолированное пространство ввода-вывода) со своими командами для доступа к нему или в виде определенной части адресного пространства памяти (совмещенное пространство ввода-вывода). В любом случае пространство ввода-вывода организовано в виде набора n-разрядных ячеек – портов (n=8,16,32) и линейно упорядочено. Между CPU и I/O происходит обмен информацией двух типов: служебной и собственно данных. Служебная информация от CPU инициирует действия, связанные с обменом данных, и представляется с помощью управляющих слов CW (Control Word). Служебные сообщения от I/O, информирующие CPU о его текущем состоянии, называются словами состояния SW (Status Word). В отличие от них данные передаются с помощью слов данных DW (Data Word). Объем служебной информации, которой обмениваются I/O и CPU , а также ее интерпретация зависят от типа I/O. Для наиболее простых устройств, служебная информация не нужна, а для других – управляющая информация и данные о состоянии УВВ могут иметь значительный объем. Размер пространства доступа (совокупность портов) в общем случае не зависит от объема информации, которой обмениваются I/O и CPU . Распространена практика последовательной передачи массива информации через один и тот же порт. Это связано не только с экономией пространства ввода-вывода, но и с минимизацией ширины физического интерфейса I/O, а также с его стандартизацией. Существует соглашения об обмене информацией между I/O и CPU , называемые протоколами обмена. Эти протоколы являются основой для разработки драйверов (набор подпрограмм) I/O, организующих обмен данными. В тех случаях, когда процедуры обмена информацией с I/O инициируются и выполняются непосредственно программой, реализуемой CPU, говорят о программно-управляемом обмене. Программно-управляемый обмен не является единственным типом обмена. Но судя по аппаратным затратам, это наиболее эффективный тип обмена, поэтому он находит самое широкое применение в MPS. В наиболее простом виде процесс программно-управляемого ввода-вывода выполняется независимо от состояния I/O. Такой вид обмена назван прямым или безусловным. Процессы прямого ввода-вывода в чистом виде возможны только при условии, что I/O всегда готовы к обмену. К тому же они являются составными элементами более сложных процессов программно-управляемого обмена, к числу которых относится условный ввод-вывод. Существует два типа условного ввод-вывод: с занятием цикла (рис.27,а) и совмещенный (рис.27,б). В первом случае MPS «зависает» в цикле ожидания готовности, тратя на это все процессорное время. Во втором случае, если I/O не готово к обмену, CPU возвращается к основной задаче без выполнения операции ввода-вывода. Однако он может снова проверить готовность УВВ к обмену и при удачном исходе выполнить его. После завершения операции обмена сигнал готовности I/O должен быть снят и выставлен заново только при новой готовности к обмену. С этой целью I/O следует проинформировать об окончании операции, для чего используется включенный в одно из управляющих слов CW сигнал подтверждения. Протокол обмена служебной информации такого типа называется квитированием. Он обеспечивает надежную асинхронную передачу данных со скоростями, определяемыми I/O.

Рис.27. Процедуры программно-управляемого обмена: б – условного с занятием цикла: в – условного совмещенного

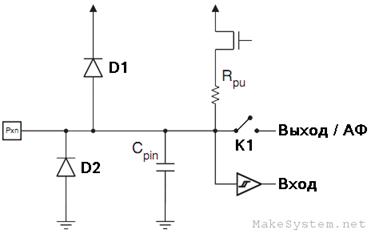

1.8.1. Порты ввода-вывода общего назначения Порты ввода-вывода общего назначения (GPIO) - это группы выводов (чаще по 8 линий на порт) через которые μC получает сигналы (будь то аналоговые или цифровые) от внешних устройств (для их последующей обработки): управляет или обменивается данными с внешними устройствами, сигнализирует о проделанной работе и т.д. Режим общего назначения означает запись/чтение двоичных значений на линии порта в отличии от разнообразных альтернативные функции (АФ) каждого вывода. На рис.28 в качестве примера приведена упрощенная электрическая схема одного вывода порта популярного микроконтроллера AVR.

Рис.28. Электрическая схема вывода линии порта AVR микроконтроллера

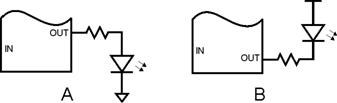

Диоды D1 и D2, предназначены для защиты вывода от напряжений, превышающих напряжение питания (электростатика - ESD и т.п.), а емкость Cpin - это паразитная емкость вывода. Rpu – встроенный подтягивающий (pull up) резистор, который может быть отключен от плюса источника питания полевым транзистором, что предаст линии порта свойство входа с открытым коллектором. Срабатывание ключа К1подключает к выводу порта Pxn двоичный источник или альтернативную функцию. Входной сигнал оценивает пороговый элемент с гистерезисом. Итак, любой вывод μC может быть настроен как на вход, так и на выход, причем читать состояние вывода Pxn можно в любой момент, даже, когда вывод настроен как выход или АФ. Каждый GPIO имеет регистры данных и конфигурации (управления). Через эти регистры осуществляется доступ по чтению ко входам, доступ по записи к выходам, а также позволяют настраивать индивидуальный вывод как вход или выход, подключать встроенные подтягивающие резисторы (pull up/pull down), входной гистерезис, задавать выходную нагрузочную способность и т.д. Конфигурация выводов GPIO как вход или выход обычно выполняется через регистр, который называют регистром направления (DDR - Data Direction Register). Запись 1 в соответствующий бит DDR конфигурирует линию порта как выход, а 0 – как вход. Наряду с величиной выходного напряжения GPIO важным является вытекающий ток при выходе равном «1» и втекающий ток при выходе равном «0». Если выход GPIO управляет входом другого цифрового устройства эти токи обычно очень маленькие (микроамперы), но когда управляет светодиодом (LED), биполярным транзистором (BJT) или реле токи становятся значительными (миллиамперы). Выходной ток GPIO для различных μC распределен в диапазоне 2 – 20 mA . Рассмотрим подключения различных элементов к GPIO [13]. На рис. 29а показано подключение LED к выходу GPIO, возбуждаемое высоким уровнем сигнала (ток протекает через LED, когда выход имеет высокий уровень напряжения), а на рис. 29в - подключение, возбуждаемое низким уровнем сигнала (ток протекает через LED, когда выход имеет низкий уровень напряжения).

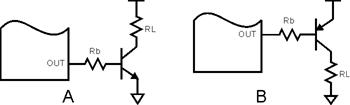

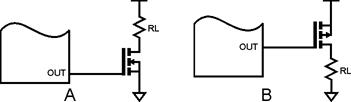

Рис. 29. Подключение светодиода к выходу GPIO Формула для вычисления значения сопротивления: R = (Vсс – Vled)/Iled,где Vled и Iled - падение напряжения на LED и ток свечения LED соответственно. На рис. 30 а и в показано подключение p-n-p BJT и n-p-n BJT к выходу GPIO по схеме с общим коллектором соответственно. Подключение на рис. 30а возбуждается высоким уровнем сигнала, при котором ток протекает через нагрузку RL , когда выход имеет высокий уровень напряжения. Подключение на рис. 30в, возбуждается низким уровнем сигнала, при котором ток протекает через нагрузку RL , когда выход имеет низкий уровень напряжения.

Рис. 30. Подключение биполярного транзистора к выходу GPIO

На рис. 31 а и в показано подключение N-канального/P-канального MOSFET к выходу GPIO возбуждаемое высоким/низким уровнем сигнала соответственно.

Рис. 31. Подключение MOSFET транзистора к выходу GPIO

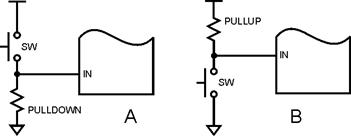

На рис. 32а показано подключение переключателя входу GPIO с подтягивающем к земле резистором. Входной сигнал является возбуждаемым высоким уровнем. Это означает, что вход принимает напряжение высокого уровня, когда переключатель замыкает контакты. На рис. 32в показано подключение переключателя входу GPIO с подтягивающем к питанию резистором. Входной сигнал является возбуждаемым низким уровнем. Это означает, что вход принимает напряжение низкого уровня, когда переключатель замыкает контакты.

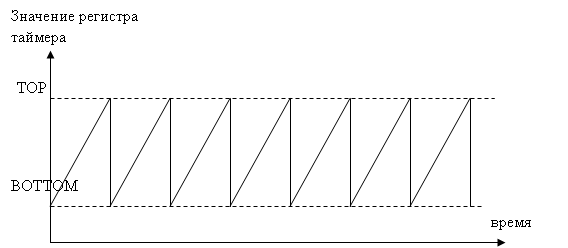

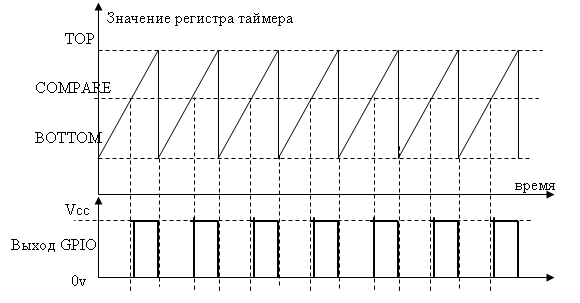

Рис. 32. Подключение переключателя SW к входу GPIO 1.7.2. Таймер-счетчик Почти каждый μC имеет в своем составе несколько (иногда очень много) таймеров-счетчиков (для краткости будем говорить таймер, Т/С), занимающих по полезности для встроенных систем второе место после GPIO. Название таймера отражает тот факт, что это устройство может быть сконфигурировано для подсчета регулярных тактовых импульсов (работает как таймер) или нерегулярных импульсов, выражающих некоторые события (работает как счетчик событий). Обычно таймер содержит предварительный делитель частоты (prescaler), N-разрядный регистр таймера-счетчика (N = 8, 16 или 32), один или более N-разрядный регистр захвата (capture) и один или более N-разрядный регистр сравнения (compare). Так же могут быть регистры управления и статуса для управления и наблюдения за таймером-счетчиком. Предварительный делитель частоты получает базовую тактовую частоту (это может быть тактовая частота CPU или более высокая или более низкая частота) и делит ее на некоторую величину перед подачей в таймер в соответствии с конфигурацией регистра предварительного делителя частоты. Величины предварительного делителя частоты могут иметь несколько фиксированных значений или значений в диапазоне 1 - 2^P, где P – разрядность предварительного делителя частоты. Назначение предварительного делителя частоты – обеспечить таймер нужной частотой для получения требуемой разрешающей способности по времени или максимального периода переполнения таймера. Регистр таймера – это обычно N-разрядный счетчик, работающий на увеличение с возможностями записи или чтения текущего значения, остановкой и сбросом. Регистр захвата – это регистр, который может автоматически загружаться текущим значением таймера при наступлении некоторого события (обычно изменение значения на некотором входе GPIO). Регистр захвата таким образом используется для получения «моментального снимка» таймера в момент появления события. Событие захвата может генерировать же прерывание. Регистр захвата может также использоваться для измерения интервала между двумя импульсами, определения времени импульса или паузы и определения времени между двумя различными входными сигналами. Регистры сравнения (иногда называют совпадения) сохраняют величину, с которой постоянно автоматически сравнивается текущее значение таймера. Регистр сравнения используется для фиксации события, когда величина в таймере совпадает с величиной регистра сравнения. Если таймер-счетчик сконфигурирован как таймер, использование регистра сравнения дает возможность генерировать события (выход GPIO изменяется, и/или возникает прерывание, и/или сбрасывается таймер) в известное и точное время. Если таймер-счетчик сконфигурирован как счетчик, регистр сравнения генерирует события при достижении счетчика заданной величины. 1.8.3. Импульсно-кодовая модуляция. Современные μC имеет в своем составе аппаратные средства, позволяющие формировать сигналы импульсно-кодовой модуляции (PWM - Pulse Width Modulation). Такие сигналы широко используются для управления различными устройствами, например, изменение скорости вращения двигателей постоянного тока, поворот на требуемый угол шагового двигателя, изменение яркости свечения ламп или LED (диммеры). PWM – это формирование последовательности импульсов прямоугольной формы с постоянным периодом и изменяемой величиной длительности импульсов. Такой сигнал характеризуется коэффициентом заполнения (duty cycle) равным отношению длительности импульса к периоду сигнала в процентах. С изменением коэффициента заполнения меняется среднее значение сигнала PWM и это можно рассматривать как вариант цифро-аналогового преобразования, где цифра это дискретные значения длительности импульса, а аналог – среднее значение напряжения. Часто реализация функции формирования сигнала PWM ложится на рассмотренные выше таймеры-счетчики μC. Пусть имеется два числа, называемые «нижнее» (BOTTOM) и большее по величине – «верхнее» (TOP). Пусть таймер стартует со значения BOTTOM, затем под действием тактовой частоты он достигает значения TOP и все начинается сначала, как на рис. 33. Получаем сигнал пилообразной формы. Запишем в регистры сравнения таймера значение COMPARE. Если текущее значение «пилы» меньше чем COMPARE значение выхода GPIO остается низким, иначе высоким, как на рис.34. Сформировался сигнал с коэффициентом заполнения 50%.

Рис. 33. Сигнал пилообразной формы таймера-счетчика

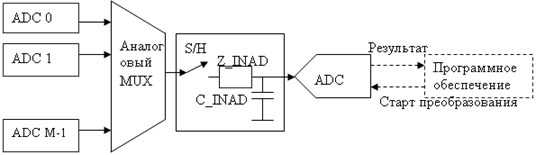

1.8.4. Многоканальный аналого-цифровой преобразователь Как правило, μC, используемые во встроенных системах, имеет в своем составе многоканальный аналого-цифровой преобразователь (АЦП или ADC). Такой ADC преобразует аналоговый сигнал, поступающий с одного из М входов GPIO, в N-разрядный двоичный код. На рис. 35 приведена упрощенная структурная схема многоканального ADC . Через Аналоговый MUX (мультиплексор) один и аналоговых входов ADCi подключается к схеме выборки/хранения (S/H), выходное значение которой преобразуется ADC в двоичный код. Преобразование запускается по команде программного обеспечения, возвращающего затем полученный результат.

Рис. 34. Сигнал пилообразной формы, формируемый таймером-счетчиком

Компонент S/H схеме выполняет захват (ключ замкнут конденсатор C_INAD через резистор Z_INAD заряжается до величины входного значения) и хранение величины входного напряжения на время выполнения преобразования (ключ разомкнут и конденсатор C_INAD не имеет возможности быстро разрядится). На время захвата влияет выходное значение источника сигнала: чем оно выше, тем больше времени необходимое для захвата.

Рис.35. Схема многоканального аналого-цифрового преобразователя

Существует большое количество методов преобразования. Базовый принцип, используемый в них, основан на использовании компаратора для определения может или нет, тот или иной бит входить в результат преобразования со значением 1. К наиболее используемым методам относятся: сравнения с пилообразным сигналом, последовательного приближения (или с поразрядным уравновешиванием) и параллельное прямое преобразования (Flash ADC). В первом методе цифро-аналоговый преобразователь (ЦАП или DAC) увеличивает напряжение на своем выходе согласно последовательному увеличению значения двоичного N-разрядного счетчика, подключенного к его входу. Как только компаратор зафиксирует совпадение выходного значения DAC и аналогового входа, двоичный счетчик останавливается, сохраняя свое значение как результат преобразования. Этот метод грешен переменным временем преобразования, и оно тем больше чем больше величина входного аналогового сигнала. Второй метод в среднем быстрее первого, время преобразования постоянно и равно N-тактам. В каждом такте преобразования решается вопрос, какое значение должен принять очередной i-разряд N-разрядного регистра результата на основании сравнения значения выхода DAC, к входу которого подключен регистр результата, и аналогового входа. Вначале преобразования наиболее старший значащий бит регистра последовательного приближения устанавливается в 1, остальные в 0. Это цифровое значение затем преобразуется DAC в аналоговую величину, соответствующую половине максимального входного значения. Если измеряемая входная величина превосходит величину DAC наиболее старший значащий бит регистра последовательного приближения остается в 1, иначе сбрасывается в 0. Этот процесс повторяется со следующим битом. Он останется в 1,если входная величина находится во второй или четвертой четверти диапазона. И так для всех остальных бит. Третий метод самый быстрый, но требует своего компаратора для каждого уровня квантования, т.е. 2^N-1 компараторов (например, при N=10 необходимо 1023 компаратора). Схема кодирования посредством таблицы истинности преобразует значения выходов компараторов в N-разрядный двоичный код. Поэтому обычно N=8, но это отрицательно сказывается на точности. ADC различных микроконтроллеров могут различаться такими свойствами, как: – разрешающая способность (разрядность, может быть переменной); – значением интегральной нелинейности: – абсолютная погрешность; – время преобразования (может быть переменным); – производительность (может быть переменной); – простой /дифференциальный аналоговый вход, количество входов; – наличие входного усилителя с переменным коэффициентом усиления; – допустимый диапазон изменения входного сигнала: – набор опорных напряжений; – режимы преобразования (однократный режим, режим с автозапуском, режим свободного хода); – прерывание по окончанию преобразования; – наличие механизмов шумоподавления.

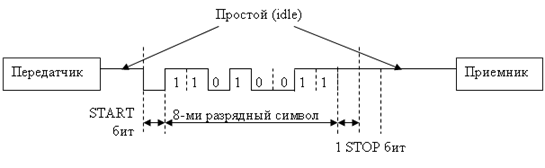

1.9. Базовые последовательные интерфейсы ввода-вывода встроенных систем Последовательная передача и прием данных означает передачу и прием по одной линии только одного бита за раз. Это уменьшает до минимума количество проводников необходимое для передачи данных в отличие от параллельной передачи, кода прием и передача выполняется одновременно по нескольким линиям – по биту на линию. Последовательный интерфейс организует последовательную передачу и прием между CPU и I/O. Различные последовательные интерфейсы тем как биты данных передаются и принимаются. Схема последовательной передачи называется симплексной, если поток данных передается и затем принимается только в одном направлении. Схема последовательной передачи называется полудуплексной, если поток может передаваться и приниматься в одном из двух направлений, только в одном направлении в каждый момент времени. Схема последовательной передачи называется дуплексной, если поток может передаваться и приниматься в одном из двух направлений одновременно. Последовательная передача, выполняемая как непрерывный поток с регулярными временными интервалами, определяемыми тактовой частотой CPU, называется синхронной передачей, а с нерегулярными временными интервалами – асинхронной передачей. . 1.9.1. Асинхронный старт-стопный интерфейс Устройство, реализующее стартстопную передачу данных, называют UART (Universal Asynchronous Receiver Transmitter). Передатчик разделяет порцию данных на символы (от 4до 8 бит или от 5 до 9 бит на символ). Каждый из символов инкапсулируется в кадр для раздельной передачи. Перед отправкой в линию каждый символ дополняется битом START в начале символа и битом/битами STOP (может бать 1, 1.5 и более бит) в конце символа. На рис. 36 приведена временная диаграмма старт-стопной передачи данных.

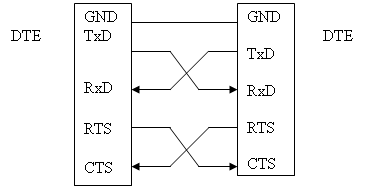

Рис. 36 Временная диаграмма старт-стопной передачи данных При настройке UART назначаются: – число STOP-битов (регулирует минимальный интервал между соседними символами, обычно выбирают равным значению 1 или 2, реже 1,5 битовых интервала); – число бит данных (5…8); – наличие или отсутствие проверочного разряда P (дополнение до четности или нечетности); – скорость передачи V бит/сек . Приемник на уровне символа синхронизируется переходом линии из состояния простой (1) в 0 (START-бит). Зная длительность битового интервала T=1/V и формат символа, приемник запускает тактовый генератор и последовательно считывает передаваемые биты, анализируя линию связи посередине битового интервала. Синхронизация на уровне бит, основана на стабильности работы и точности задания частоты передающего и приемного генераторов на коротком интервале приема символа. Асинхронность передачи вытекает из того, что приемник не знает в какой момент времени поступит очередной символ. Отсутствует единая для всего потока данных синхронизация, т.е. она имеет локальный характер – устанавливается заново всякий раз при обнаружении приемником начала очередного старт-бита. Через UART к встроенной системе обычно подключаются микросхемы модемов различных беспроводных коммуникационных технологий, GPS-приемники. Это связано с историей возникновения UART как интерфейса для передачи данных между компонентами телекоммуникационного оборудованием DTE (Data Terminal Equipment - оконечное оборудование данных или компьютер) и DCE (data communication equipment - оборудование передачи данных или модем) и являющегося элементом стандарта RS-232. В этом стандарте вход данных UART называн RxD, а выход TxD и ведены многочисленные служебные сигналы. Сейчас из них используется лишь следующие сигналы. RTS (Request To Send – запрос на передачу данных) и CTS (Clear To Stnd – готовность к передаче данных). Их первоначальное назначение (для отображения запроса и готовности передачи данных от DTE к DCE) в настоящее время зачастую игнорируется – эти сигналы могут альтернативно трактоваться как равноправные признаки готовности устройств DTE и DCE к приему данных от устройства-партнера. В асинхронном режиме сигналы RTS и CTS обслуживают оба направления передачи данных, что выходит за рамки стандарта и отражает некий “стандарт де-факто”. Поэтому наименования сигналов не соответствуют (и даже противоречат) их назначению. Выходной сигнал RTS теперь рассматривается как готовность DTE принять данные RxD от такого же устройства DTE. Аналогично входной сигнал CTS теперь рассматривается как разрешение на передачу данных для DTE. На рис.37. приведена схема соединения двух DTE (нуль-модемное соединение). Логика работы такова: передача данных в ту или иную сторону возможна только при условии, что приемник готов эти данные принять. Если обнаружена неготовность приемника, то источник данных приостанавливает работу, ждет появления готовности , возобновляет передачу и т.д. Это – так называемое аппаратное управление потоком данных (hardware flow control) Современные микроконтроллеры могут содержать несколько UART. Это позволяет достаточно просто реализовывать во встроенных системах коммуникационные функции.

Рис.37. Схема соединения двух DTE

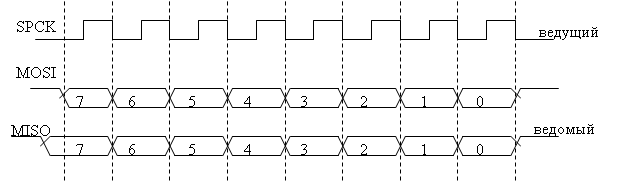

1.9.2. Последовательный интерфейс SPI SPI (Serial Peripheral Interface) – последовательный синхронный интерфейс предназначенный для связи CPU с компонентами MPS, расположенных в пределах печатной платы, по принципу ведущий-ведомый (Master - Slave), как показано на рис.38. Через SPI обеспечивается связь с такими компонентами встроенных систем как: – датчики (температуры, давления, ADC, сенсорный экран); – управляющие устройства (аудио кодеки, цифровые потенциометры, DAC); – flash и EEPROM; – MMC и SD карты. SPI основан на взаимодействии двух сдвиговых регистров, соединенных в кольцо. Перед началом передачи данные передающих параллельных регистров переписываются в соответствующие сдвиговые регистры. По окончании передачи данные из сдвиговых регистров переписываются в параллельные регистры. На рис.39 приведена временная диаграмма работы интерфейса. Под действием тактовых импульсов генератора ведущего данные из сдвигового регистра ведущего перемещаются в сдвиговый регистр ведомого.

Рис.38. Взаимодействие через интерфейс SPI

Рис.39. Временная диаграмма работы SPI

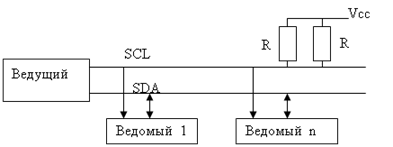

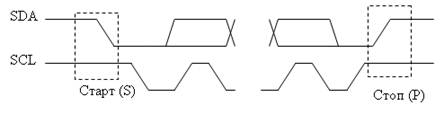

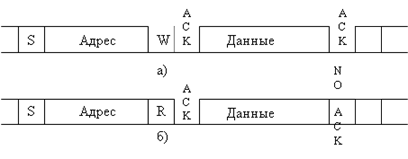

1.9.3. Интерфейс I2C Также как и SPI I2C (Inter Integrated Circuit) или TWI (Two-wire Interface – двухпроводный интерфейс) – последовательный синхронный интерфейс предназначенный для связи CPU с компонентами MPS, расположенных в пределах печатной платы, по принципу ведущий-ведомый. I2C находит применение в устройствах, предусматривающих простоту разработки и низкую себестоимость изготовления при относительно неплохой скорости работы. Через него обеспечивается связь с такими компонентами встроенных систем как: – модули NVRAM; – низкоскоростные ADC/DAC; – регулировка контрастности, насыщенности и цветового баланса мониторов; – регулировка звука в динамиках; – управление светодиодами, в том числе в мобильных телефонах; – чтение информации с датчиков мониторинга и диагностики оборудования, например, CPU или скорость вращения вентилятора охлаждения; – чтение информации с часов реального времени (кварцевых генераторов); – управление включением/выключением питания системных компонент; – информационный обмен между микроконтроллерами; Интерфейс I2C является байт-ориентированным со скоростью передачи до 2 Мбит/сек. На рис. 40 приведена схема взаимодействие через интерфейс I2C. Каждая передача кадра начинается со стартовой позиции S и заканчивается стоповой P, как показано на рис. 41. На рис.42 приведены временные диаграммы операций записи а) и чтения б). Первый байт кадра состоит из 7-битного адреса ведомого и бита R/W типа операции. Значение следующего бита (ACK) =0 выставляет ведомый, распознавший свой адрес. При записи ведущий в ответ выставляет байт данных (старшими разрядами вперед). Следующим битом (ACK)=0 ведомый подтверждает принятый байт. В случае операции чтения бит R/W=1 и вслед за ACK ведомый выставляет на линию SDA байт данных, который следующим битом подтверждает ведущий.

Рис. 40. Взаимодействие через интерфейс I2C

Рис. 41. Условия начала и конца кадра интерфейса I2C

Рис. 42. I2C: а) операция записи, б) операция чтения

1.9.4. Шина USB 1.9.4.1. Введение в USB Последовательная шина USB (Universal Serial Bus) является промышленным стандартом и разработана для подключения среднескоростных и низкоскоростных периферийных устройств и обеспечивает: подключение устройств под напряжением, автоматическое распознавание немедленно после подключения, питание маломощных устройств с самой шины, полудуплексный способ обмена [14]. Например, для USB 2.0 полная скорость передачи данных составляет 0,5—12 Мбит/сек (аудио-, видеоустройства), низкая – 10—1500 Кбит/ сек (клавиатуры, мыши, джойстики) и высокая – 25 —480 Мбит/с (видеоустройства, устройства хранения информации). Максимальная длина кабеля для полной скорости передачи – 3м, а для низкой – 5м. Максимальное количество подключаемых устройств – 127. |

|||||||

|

Последнее изменение этой страницы: 2018-04-12; просмотров: 397. stydopedya.ru не претендует на авторское право материалов, которые вылажены, но предоставляет бесплатный доступ к ним. В случае нарушения авторского права или персональных данных напишите сюда... |