Студопедия КАТЕГОРИИ: АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция |

АППАРАТНЫЕ СРЕДСТВА ВСТРОЕННЫХ СИСТЕМ 2 страницаCPU выполняет каждую команду за несколько шагов: 1. Вызывает следующую команду из памяти и переносит ее в регистр команд. 2. Меняет содержимое счетчика команд, который теперь указывает на следующую команду. 3. Определяет тип выбранной команды. 4. Если команда использует слово из памяти, определяет, где находится это слово. 5. Передает слово, если это необходимо, в регистр CPU. 6. Выполняет команду. 7. Переходит к шагу 1 для выполнения следующей команды. Такую последовательность шагов называют выборка-декодирование-исполнение.

1.2. Элементы архитектуры процессоров встроенных систем Под архитектурой CPU понимают функциональные возможности CPU, используемые для представления программ и данных, а также для управления процессом вычислений. Согласно [2] архитектура процессора определяется следующими элементами: 1. Множество команд. Множество команд в общем случае содержит группу команд передачи данных, группу команд целочисленной арифметики, группу команд арифметики с плавающей точкой, группу логических команд, группу команд управления последовательностью выборки, группу специальных команд. Множество команд определяет также форматы кодирования команд, способы адресации данных. 2. Программная модель. Программная модель определяет множество регистров и соглашение о памяти, включающее детали нумерации бит и байт и как данные (целые или в форме с плавающей запятой) хранятся в памяти. 3. Модель памяти. Модель памяти определяет размер адресного пространства и разбиение адресного пространства на блоки (сегменты) и страницы, порядок байт, когерентность памяти и различные виды ее защиты.  4. Модель прерываний. Модель прерываний определяет полное множество прерываний и условий, которые генерируют прерывания. Модель прерываний специфицирует характеристики прерываний, такие как определенные или неопределенные, синхронные или асинхронные, маскируемые или не маскируемые. Модель прерываний определяет вектора прерываний и множество регистров, которые задействуются при прерываниях. Модель прерываний также обеспечивает адресное пространство для реализации специфических прерываний. 5. Модель управления памятью. Модель управления памятью определяет ее разбиение, конфигурирование и защиту. Модель управления памятью также специфицирует выполнение трансляции адресов (преобразование логического адреса в физический или действительный), логическое, виртуальное и физическое адресное пространство, специфические управляющие команды и другие характеристики. 6. Модель хранения времени. Модель хранения времени определяет средства, позволяющие устанавливать время суток, а также ресурсы и механизмы, необходимые для поддержки исключений, зависящих от времени.

1.2.1. Множество команд Команда состоит из кода операции и некоторой дополнительной информации, например, откуда поступают операнды и куда должны отправляться результаты - это формат команды. Через код операции передается информация о выполняемых командой действиях. Механизм определения, где находятся операнды (их адреса), называют адресацией. В команде может присутствовать ноль, один, два или три адреса. В одних процессорах все команды имеют одинаковую длину; в других команды могут быть разной длины. Если все команды одной длины, то это упрощает декодирование, но часто требует большего пространства, поскольку все команды должны бать такой же длины, как самая длинная. Множество команд процессора часто называют системой команд. Это множество можно разбить на несколько подмножеств, содержащих однотипные команды: команды пересылки данных, арифметические и логические команды, команды ветвления и команды управления процессором. Разработка кодов операций является важной частью архитектуры. Однако значительное число битов программы используется для того, чтобы определить, откуда нужно брать операнды, а не для того, чтобы узнать, какие операции нужно выполнить. Самый простой способ определения операнда – включить в адресную часть команды сам операнд, а не адрес операнда или другую информацию, описывающую, где находится операнд. Такой операнд называют непосредственным операндом, а адресацию - непосредственной адресацией. Этим способом можно работать только с константами, зато не требуется обращения к памяти для чтения операнда. Следующий способ определения операнда – просто дать его полный адрес в команде. Такой способ называют прямой адресацией. Этот способ можно использовать только для доступа к переменным, адреса которых известны заранее. Регистровая адресация сходна с прямой адресацией, только вместо адреса ячейки MM указывается адрес регистра. Этот способ адресации является самым распространенным. При косвенной регистровой адресации определяемый операнд берется из памяти или отправляется в память, но адрес не зафиксирован жестко в команде, как при прямой адресации. Вместо этого адрес содержится в регистре и его называют указателем. Преимущество косвенной адресации состоит в том, что можно обращаться к памяти, не имея в команде полного адреса. Индексная адресация предполагает, что адрес памяти является суммой указателя и небольшого смещения в самой команде. Относительная индексная адресация предполагает, что адрес памяти вычисляется путем суммирования значения двух регистров и смещения.

1.2.2. Программная модель 1.2.2.1. Регистры Все CPU содержат набор регистров, обеспечивающий быстрый доступ к часто используемым данным, избегая обращения к ММ. Другими словами регистры – это небольшая сверхоперативная память с минимальным временем доступа. Регистры можно разделить на адресные регистры (АР или AR - Address Register), регистры данных (РД или DR – Data Register ), регистры общего назначения (РОН или GPR – General Purpose Register) и специальные регистры (СР или DR – Dedicated Register). Адресные регистры содержат адреса ММ. Регистры данных содержат промежуточные результаты вычислений и могут специализироваться на хранении различных типов данных (целых чисел или в формате с плавающей запятой). Регистры общего назначения содержат как адресную информацию, так и данные. В одних CPU РОН полностью симметричны и взаимозаменяемы, а в других - могут быть специализированы. Специальные регистры включают счетчик команд и другие регистры с особой функцией (регистры специальных функций). Некоторые СР доступны только в особом режиме работы CPU – привилегированном или супервизорном. Эти регистры используются только операционной системой (ОС) – специальной программой, управляющей выполнением пользовательских программ. Есть один специальный регистр, который представляет собой привилегированно-пользовательский гибрид. Это флажковый регистр или PSW (Program State Word – слово состояния программы). PSW содержит различные биты, которые нужны для работы CPU. Самые важные биты - это коды условий. Они устанавливаются в каждом цикле с участием АЛУ и отражают состояние результата выполненной операции. Биты кода условий включают: N – результат отрицательный (Negative); Z – результат равен 0 (Zero); C – перенос из самого левого бита (Cary out); V – результат вызвал переполнение (oVerflow); AC – перенос из третьего бита (Auxiliary cary – служебный перенос); P – результат четный (Parity). Коды условий используются в командах условного перехода. Другие поля PSW указывают режим CPU (пользовательский или привилегированный), трассовый бит (используется для отладки), уровень приоритета процессора, а также статус разрешения прерываний. Указатель стека (SP – Stack Pointer) содержит адрес вершины стека. Стек - это память магазинного типа с дисциплиной обслуживания LIFO, организованная в MM и содержащая данные и/или адреса возврата. Стек может содержать некоторую структуру данных, местоположение которой определяется двумя указателями SP и LV, где LV – нижняя граница расположения данных в стеке. Такую структуру называют фреймом (кадром) стека. В некоторых процессорах только часть РОН «видны» программе в любой момент времени. Эта особенность, называемая регистровыми окнами. Она предназначена для повышения эффективности вызова подпрограмм. Регистровые окна имитируют стек. То есть существует несколько наборов регистров, точно также как и несколько фреймов в стеке. Специальный регистр CWP (Current Window Pointer – указатель текущего окна) содержит номер регистрового окна, доступного программе. Команда вызова подпрограммы такого процессора скрывает старый набор регистров и путем изменения CWP предоставляет новый набор, который может использовать вызванная подпрограмма. Однако некоторые регистры могут перекрываться, что обеспечивает эффективный способ передачи параметров между подпрограммами.

1.2.2.2. Типы данных Процессоры поддерживают различные типы данных на уровне системы команд. Типы данных можно разделить на две категории: числовые и нечисловые. Среди числовых типов данных главными являются целые числа различной длины (8,16,32 или 64 бита). Некоторые процессоры поддерживают целые числа и со знаком и без знака. Знаковый бит является старшим битом слова, а отрицательные числа представляются в дополнительном коде. Нечисловые типы данных используются для представления символьной информации. Наиболее распространенными символьными кодами являются ASCII (7-битовый символ) и UNICODE (16-битоаые символы). На уровне команд часто имеются особые команды, предназначенные для операций с цепочками символов. Эти цепочки иногда разграничиваются специальными символами в конце. Вместо этого для определения конца цепочки может использоваться поле длины цепочки. Команды могут выполнять копирование, поиск, редактирование цепочек и другие действия.

1.2.3. Модели памяти 1.2.3.1. Адресное пространство Процессор взаимодействует с памятью, разделенной на ячейки с последовательными адресами. Наиболее распространенный размер ячейки 8 бит или байт. Байты обычно группируются в 4-байтовые или 8-байтовые слова. Некоторые процессоры требуют, чтобы слова были выровнены в своих естественных границах. Так, например, 4-байтовое слово может начинаться с адреса 0,4,8 и т.д., но не с адреса 1 или 2. Точно так же слово из 8 байтов может начинаться с адреса 0,8 или 16, но не с адреса 4 или 6. Выравнивание адресов требуется довольно часто, поскольку память работает более эффективно. Возможность считывать слова с произвольными адресами требует усложнения процессора и увеличивает времени доступа к памяти.

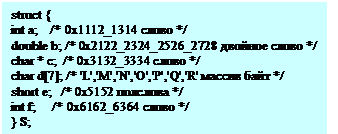

1.2.3.2. Порядок байт Порядок байт важен для размещения в памяти числовых типов данных. Порядок, называемый обратным (big-endian), подразумевает, что старший значащий байт числа размещается по младшему адресу памяти. Порядок, называемый прямым (little-endian), подразумевает, что старший значащий байт числа размещается по старшему адресу памяти. В качестве примера рассмотрим отображение структуры данных S, представленной на Си для 32-разрядного процессора:

В случае порядка big-endian в памяти будут следующие значения: содержимое 11 12 13 14 (x) (x) (x) (x) адрес 00 01 02 03 04 05 06 07 содержимое 21 22 23 24 25 26 27 28 адрес 08 09 0A 0B 0C 0D 0E 0F содержимое 31 32 33 34 ‘L’ ‘M’ ‘N’ ‘O’ адрес 10 11 12 13 14 15 16 17 содержимое ‘P’ ‘Q’ ‘R’ (x) 51 52 (x) (x) адрес 18 19 1A 1B 1C 1D 1E 1F содержимое 61 62 63 64 (x) (x) (x) (x) адрес 20 21 22 23 24 25 26 27 В случае порядка little-endian в памяти будут следующие значения: содержимое 14 13 12 11 (x) (x) (x) (x) адрес 00 01 02 03 04 05 06 07 содержимое 28 27 26 25 24 23 22 21 адрес 08 09 0A 0B 0C 0D 0E 0F содержимое 34 33 32 31 ‘L’ ‘M’ ‘N’ ‘O’ адрес 10 11 12 13 14 15 16 17 содержимое ‘P’ ‘Q’ ‘R’ (x) 52 51 (x) (x) адрес 18 19 1A 1B 1C 1D 1E 1F содержимое 64 63 62 61 (x) (x) (x) (x) адрес 20 21 22 23 24 25 26 27

1. 2.3.3. Когерентность памяти Еще один аспект модели памяти – семантика памяти. Естественно ожидать, что команда чтения из памяти (Load), которая встречается после команды записи в память (Store) и которая обращается к тому же адресу, возвратит только что сохранное значение, т.е. действия с памятью согласованы (когерентны). Однако в процессорах с параллельным выполнением команд (конвейерные процессоры) преобразования переупорядочиваются. Таким образом, существует реальная опасность, что память не будет действовать так, как ожидалось. Ситуация осложняется в случае с мультипроцессором, когда каждый процессор посылает разделяемой памяти поток запросов на чтение и запись, которые тоже могут быть пере упорядочены. Первый подход к обеспечению когерентности памяти состоит в том, что процессор все запросы к памяти упорядочивает таким образом, чтобы каждый из них завершался до того, как начнется следующий. Это вредит производительности, но дает простейшую семантику памяти (все операции выполняются в строгом программном порядке). При втором подходе упорядоченное обращение к памяти может быть достигнуто с помощью команды Sync, которая блокирует запуск всех новых операций памяти до тех пор, пока предыдущие операции не будут завершены. Это сильно затрудняет работу разработчикам компиляторов. Концепция выполнение инструкций по порядку. 1. Считывание инструкции. 2. Если все операнды инструкции доступны, то она передаётся на выполнение соответствующему исполнительному модулю, иначе процессор останавливается, ожидая готовности операндов. 3. Инструкция выполняется в соответствующем модуле. 4. Модуль записывает результат обратно в регистровый файл. Концепция выполнение не по порядку. 1. Считывание инструкции. 2. Помещение инструкции в очередь. 3. Инструкция находится в очереди до тех пор, пока её операнды не станут доступны. Таким образом, инструкция может покинуть очередь прежде, чем инструкция попавшая туда раньше. 4. Выбранная из очереди инструкция выполняется в соответствующем модуле. 5. Результат помещается в очередь. 6. Только после того, как все инструкции, которые были в очереди впереди данной, выполнятся, её результат помещается в регистровый файл. Данная парадигма применяется при разработке суперскалярных процессоров, позволяя повысить процент загрузки исполнительных модулей, а, следовательно, и их производительность.

1. 2.3.4. Защита памяти Защита памяти предусматривает механизмы ограничения доступа к памяти по записи или чтению со стороны программ. Защита связана с разбиением памяти на блоки, страницы или сегменты. Для этих объектов может быть разрешено только чтение, только запись, запись и чтение со стороны программы пользователя или супервизора. Вариант защиты задается в дескрипторных таблицах сопоставленных этим разбиениям. Нарушения требований защиты вызывают особое поведение процессора для их преодоления.

1. 2. 4. Модель прерываний Прерывания – это изменения в потоке управления, вызванные какими-либо событиями. Эти события могут быть внешними по отношению к процессору (инициируются устройствами ввода-вывода) - асинхронные прерывания или вызваны результатами выполнения команд – синхронные прерывания (системные прерывания, исключения или ловушки). Прерывание останавливает работу программы и передает управление не содержащейся в явном виде в программе подпрограмме обработки прерывания (ISR – Interrupt Serves Routine или interrupt handler – обработчик прерывания) для выполнения особых действий. Адрес первой команды ISR определяется вектором прерывания, сопоставленным тому или иному прерыванию. После завершения ISR управление передается прерванной программе. В случае асинхронного прерывания программа должна продолжить процесс в том же самом состоянии, в котором находилась, когда произошло прерывание. Соответствующую ISR называют прозрачной. Более общим является понятие исключение (exception) - необычная, непредусмотренная или ошибочная ситуация, которая может возникнуть при выполнении программы и изменить её нормальное функционирование. Наиболее распространенные условия, которые могут вызвать исключения, это переполнение и исчезновение значащих разрядов при операциях с плавающей запятой, переполнение при операциях с целыми числами, нарушения защиты памяти, неопределяемый код операций, переполнение стека, обращение к несуществующим или нечетным адресам MM, деление на 0. К исключениям относят также и прерывания. Физический интерфейс простой системы прерываний может быть представлен единственной линией IRQ (Interrupt Request – запрос прерывания). Высокий уровень напряжения на линии IRQ, например, воспринимается как запрос на прерывание. На линию IRQ могут быть мультиплексированы запросы от нескольких источников. Однако в этом случае после принятия общего запроса к обслуживанию возникает задача идентификации источника, выставившего запрос, и передачи управления на соответствующую подпрограмму ISR. Эта задача решается только программным методом с помощью специальной процедуры, называемой полингом (polling). Функция полинга состоит в последовательном опросе состояния всех устройств (чтение регистров состояния) для выявления готовности к обслуживанию. Для увеличения числа одновременно обслуживаемых источников прерываний в систему вводится несколько линий с фиксированными векторами прерываний. Такую систему называют радиальной. Часть радиальных линий могут быть внутренними для приема исключений процессора. В зависимости от числа запросов, одновременно находящихся на обслуживании, различают одно- и многоуровневые системы прерываний. В одноуровневой системе в каждый момент времени допускается лишь один запрос. Обработка всех других запросов откладывается до окончания текущего обслуживания блокировкой всех остальных. Если несколько устройств одновременно запросили обслуживание, система прерываний выбирает одно из них на основании приоритета, отражающего важность и срочность его обслуживания. Как наиболее естественная, выделяется линейно упорядоченная фиксированная система приоритетов. Повышение гибкости системы приоритетов связано с их динамическим изменением по заданному алгоритму. Однако в каждый момент времени все приоритеты строго упорядочены, что обеспечивает однозначный выбор одного из них. Одной из систем с динамически изменяемыми приоритетами является циклическая система. В ней после каждого очередного обслуживания запроса происходит циклический сдвиг приоритетов с присвоением нижнего только что обработанному запросу. Это приводит к равномерному распределению приоритетов. Многоуровневая система прерываний разрешает многократное (по числу уровней) прерывание одних ISR другими. Для этого каждому уровню ставится в соответствие некоторое подмножество запросов из их общего числа и строго упорядоченный приоритет. Подпрограммы ISR некоторого уровня могут быть прерваны лишь запросами более высокого уровня. Приоритеты запросов сравниваются с приоритетом процессора и, если он ниже, прерывают его работу. Для разрешения конфликтов внутри группы запросов одного уровня существует вторичная система приоритетов.

1.2. 5.Модель управления памятью Виртуальная память - это способ выполнения программ, размер которых превышает размер доступной физической памяти. Части программ (оверлеи) хранятся во вторичной памяти и пересылаются в MM по мере надобности. Пересылка осуществляется автоматически операционной системой и невидима для программы. Виртуальная память основана на разделении понятий адресного пространства и адресов памяти (физические адреса). Виртуальное адресное пространство – это множество адресов, к которым может обращаться программа данного CPU, а реальные адреса MM MPS – физическим адресным пространством. Виртуальное адресное пространство CPU намного больше его адресного пространства, определяемого разрядностью его адресного регистра.

1.2.5.1. Страничная организация памяти Пусть адресное пространство CPU равно 65536 байт, а физическое адресное пространство MPS содержит ячейки с 0 по 4095. Можно было бы настроить CPU MPS так, чтобы при обращении к адресу 4096 должно использоваться слово из памяти 0, а при обращении к адресу 4097 – слово из памяти с адресом 1, при обращении к адресу 8191 – слово из памяти с адресом 4095. Другими словами, определено отображение из адресного пространства в действительные адреса памяти – механизм трансляции адресов. Что произойдет, если CPU обратится к адресу 8192. В CPU без виртуальной памяти произойдет исключение по несуществующему адресу физической памяти. В CPU с виртуальной памятью будет иметь место следующая последовательность шагов: 1. Байты из MM будут отправлены во вторичную память. 2. Байты с 8192 по 12287 будут загружены из вторичной памяти в MM. 3. Отображение адресов изменится: теперь адреса с 8192 по 12287 соответствуют ячейкам физической памяти с 0 по 4095. 4. Выполнение программы продолжится, как ни в чем не бывало. Такая технология автоматического отображения называется страничной организацией памяти, а части программы, которые считываются из вторичной памяти, страницами. Страница – набор соседних байтов фиксированной длины, не имеющих непосредственной связи с логической структурой программы. Виртуальное адресное пространство разбивается на ряд страниц равного размера, обычно от 512 до 64 Кбайт, хотя иногда встречается 4 Мбайт. Размер страницы всегда должен быть степенью двойки. Физическое адресное пространство тоже разбивается на части равного размера таким образом, чтобы каждая такая часть MM вмещала ровно одну страницу. Эти части MM называют страничными кадрами. Рассмотрим для примера, как можно 32-разрядный логический адрес (пусть виртуальная память тоже 32 разряда, а размер страницы 4 Кбайт) отобразить на физический адрес MM объемом 32 Кбайт. В CPU это отображение выполняет MMU. Преобразование 32-битного логического адреса в 15-битный адрес MM (8 страничных кадров) выполняется следующим образом. Узел MMU разделяет логический адрес на 20-битный номер виртуальной страницы и 12-битовое смещение внутри страницы. Номер виртуальной страницы используется в качестве индекса в таблице страниц для нахождения нужной страницы. На рис.5 номер виртуальной страницы равен 5, поэтому из таблицы выбирается элемент 5 с номером страничного кадра 6 . Сначала MMU проверяет, находится ли нужная страница в текущий момент в MM, читая бит присутствия в данном элементе таблицы страниц. В примере этот бит равен 1, т.е. страница в памяти.

Рис.5. Формирования адреса MM

При обращении к адресу страницы, которой нет в памяти, происходит исключение из-за отсутствия страницы. В случае такой ошибки операционная система должна считать нужную страницу из вторичной памяти, ввести новый адрес физической памяти в таблицу страниц, а затем повторить команду, которая вызвала исключение. Такой метод работы с виртуальной памятью называется вызовом страницы по требованию. Для каждой программы распределение памяти уникально и при переключении с одной программы на другую меняется, поэтому в системах с разделением времени такой подход не годится. Другой подход основан на наблюдении, что большинство команд обращаются к адресному пространству не равномерно. Обычно большинство обращений относится к небольшому числу страниц. При обращении к памяти можно вызвать команду, вызвать данные или сохранить данные. В каждый момент существует набор страниц, которые использовались при последних m обращениях. Этот набор называют рабочим множеством. Поскольку рабочее множество меняется очень медленно, можно опираясь на последнее перед остановкой программы рабочее множество, предсказать, какие страницы понадобятся при новом запуске программы. Эти страницы можно загрузить заранее перед очередным запуском программы. При обращении программы к странице, которая отсутствует в памяти ее нужно вызвать из вторичной памяти. Однако, чтобы освободить для не место, нужно во вторичную память отправить какую-нибудь страницу. По одному из алгоритмов удаляется та страница, которая использовалась наиболее давно, поскольку вероятность того, что она будет в текущем рабочем множестве, очень мала. Этот алгоритм называется LRU (Last Recently Used – наиболее давно использовавшиеся элементы). Иногда LRU приводит к патологическим ситуациям (например программа, цикл которой простирается на несколько страниц). Другой алгоритм – FIFO (First-in First-out – первым поступил, первым выводится) удаляет ту страницу, которая раньше всех загружалась, независимо от того, когда в последний раз производилось обращение к этой странице. С каждым страничным кадром связан отдельный счетчик. Изначально все счетчики установлены на 0. После ошибки из-за отсутствия страниц счетчик каждой страницы, находящейся в памяти, увеличивается на 1, а счетчик только что вызванной страницы принимает значение 0. Когда нужно выбрать страницу для удаления, выбирается страница с самым большим значением счетчика. Если размер рабочего множества больше, чем число допустимых страничных кадров, ни один алгоритм не дает хороших результатов, и ошибки из-за отсутствия страниц будут происходить часто. Если программа постоянно вызывает подобные ошибки, то говорят, что наблюдается пробуксовка (thrashing). Если страница, которую нужно удалить не менялась, с тех пор как ее считали, то необязательно ее записывать обратно во вторичную память, поскольку точная копия уже существует. В MMU содержится бит для каждой страницы, который равен 0 при загрузке страницы и принимает значение 1, когда изменяются данные в этой странице. По этому биту ОС определяет необходимость перезаписи страницы.

1.2.5.2. Сегментация памяти Страничная организация памяти представляет одномерную виртуальную память, в которой виртуальные адреса идут один за другим от 0 до максимального адреса. Удобнее использовать два или несколько виртуальных адресных пространств. Например, компилятор может иметь несколько таблиц, которые создаются в процессе компиляции: 1. Таблица символов, которая содержит имена и атрибуты переменных. 2. Исходный текст, сохраняемый для листинга. 3. Таблица, содержащая все использующиеся целочисленные константы и константы с плавающей запятой. 4. Дерево, содержащее синтаксический анализ программы. 5. Стек, используемый для вызова процедур в компиляторе. Каждая из первых четырех таблиц постоянно растет в процессе компиляции. Последняя таблица растет и уменьшается непредсказуемо. В одномерной памяти эти таблицы пришлось бы разместить в виртуальном адресном пространстве в виде смежных областей. Что произойдет, если программа содержит очень большое число переменных? Адресное пространство, предназначенное для таблицы символов, может переполниться, даже если в других таблицах много свободного места. Компилятор может забирать свободное пространство у одних таблиц и передавать его другим таблицам, но это похоже на управление оверлеями вручную. Нужно освободить программиста от расширения и сокращения таблиц, подобно тому, как виртуальная память исключает необходимость следить за разбиением программы на оверлеи. Для этого нужно создать много абсолютно независимых адресных пространств, которые называют сегментами. Каждый сегмент состоит из линейной последовательности адресов от 0 до какого-либо максимума. Разные сегменты могут иметь разную длину. Длина сегмента может меняться во время выполнения программы. Так как каждый сегмент основывает отдельное адресное пространство, разные сегменты могут изменяться независимо друг от друга. Если процедура занимает отдельный сегмент n и впоследствии изменяется и перекомпилируется, то другие процедуры менять не нужно, т.к. начальный адрес процедуры не изменился. Сегментация облегчает разделение общих процедур или данных между несколькими программами. Эти процедуры или данные размещают в одном сегменте, т.е. нет необходимости иметь копии этих объектов в каждой программе. Разные сегменты могут иметь разные виды защиты. Например, сегмент с процедурой можно определить “только для выполнения”, запретив тем самым считывание и запись в него. Для массива с плавающей запятой разрешается только чтение и запись, но не выполнение и т.д. Такая защита часто помогает обнаружить ошибки в программе. Защита имеет смысл только в сегментированной памяти и не имеет смысла в одномерной памяти. Поскольку каждый сегмент включает в себя объект только одного типа, он может использовать защиту, подходящую для этого типа. Сегментация реализуется разделением сегмента на страницы и вызова их по требованию. В этом случае одни страницы сегмента могут находиться в MM, а другие – во вторичной памяти. Чтобы разбить сегмент на страницы, для каждого сегмента создается своя таблица страниц. |

||

|

Последнее изменение этой страницы: 2018-04-12; просмотров: 379. stydopedya.ru не претендует на авторское право материалов, которые вылажены, но предоставляет бесплатный доступ к ним. В случае нарушения авторского права или персональных данных напишите сюда... |