Студопедия КАТЕГОРИИ: АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция |

Арифметико-логического устройства⇐ ПредыдущаяСтр 17 из 17 В состав многих серий микросхем входят модули арифметико-логических устройств (АЛУ), где над входными величинами выполняются арифметические и логические операции, а также блок ускоренного переноса для этого АЛУ. Примером таких блоков служат микросхемы К155ИМЗ, К155ИП4, К1500ИП181, К1500ИП179. Условное обозначение микросхем АЛУ приведено на рис. 4.22 а.

Рис. 7.9. Микросхемы АЛУ. На вход Р0подается внешний перенос. На выходах F0¸F3 формируется выходное слово, Р0является выходным переносом. Выходы G и Н позволяют получать функцию генерации и передачи переноса для групп, которые могут быть использованы для образования переноса в быстродействующих сумматорах. Результаты сравнения кодов А и В на равенство можно получить на выходе К.

Рис. 7.10. Схема соединения микросхем АЛУ Для получения многоразрядного сумматора с цепным переносом достаточно соединить микросхему, как это показано на рис.7.10, где показаны только входы P0и выходы Pn. Для получения быстродействующего сумматора с последовательно-параллельным переносом необходимо использовать блок ускоренного переноса GRP, условное

Рис. 7.11. Сумматор с групповым преносом обозначение которого приведено на рис. 7.11. Тогда структура 16 разрядного параллельно-параллельного сумматора имеет сладующий вид (рис.7.11) АЛУ служит для выполнения арифметических операций сложения и вычитания, а также логических операций над oneрандами А и В. Разрядность операндов равна четырем, и в процессе обработки они подаются на соответствующие входы А0-АЗ и В0-ВЗ. Входы S0, S1, S2, S3 являются входами режима работы. Табл. 7. 3.

Вход М задает характер выполняемых операций. Если M=1, то в зависимости от комбинаций сигналов Si выполняется любая из 16 логических операций. При М=0, то в схеме выполняются арифметические операции. Перечень операций, выполняемых АЛУ К155ИПЗ, приводится в табл. 7.3.  30. Дешифратор, шифратор. Шифраторы Шифратор преобразует сигнал, поданный только на один входной провод, в параллельный двоичный код на выходах шифратора. Шифратор также называют кодером (CD). Подача сигнала на один из входов шифратора приводит к появлению на выходах двоичного кода, соответствующего номеру возбужденного входа. В отечественных схемах шифраторы обозначаются буквами ИВ, например К555ИВ1. Шифратор называется полным, если он имеет 2пвходов ип выходов. Примером может служить шифратор на рис.1, который преобразует номер возбужденного входа в двоичное число. На все входы такого шифратора, кроме одного, подаются нули, а на выбранный ход поступает единица. На выходах шифратор получаем само число в двоичном параллельном коде.

Рис.1 Часто шифраторы используются для преобразования десятичных чисел в двоичную систему счисления. Входов при этом требуется только 10, а выходов п=4. Здесь число входов меньше2п. Шифраторы, у которых число входов меньше2п, называют неполными шифраторами. Например, десятичный шифратор на рис.2, при возбуждении одного из 10 входов формирует на выходах двоичный код номера возбужденной входной линии. Так, при подаче сигнала на входх9на выходах появится код 1001. Выходы такого шифратора обозначаются весами соответствующих разрядов.

Рис.2 Для реализации шифратора рис.2 удобно использовать наборы из логических схем ИЛИ, но сначала следует составить таблицу истинности. Таблица истинности десятичного шифратора

Этой таблице соответствует схема на элементах ИЛИ, показанная на рис.3.

Рис. 3 В ТТЛ микросхемах используются шифраторы 8 - 3(ИВ1, ИВ2), 10 - 4 (ИВЗ). Помимо информационных входов, шифраторы содержат дополнительные, обеспечивающие разрешение ввода и вывода. Дополнительные входы обеспечивают синхронный режим работы, а также позволяют проводить наращивание шифраторов. Дешифраторы Дешифратор преобразует код, поступающий на его входы, в сигнал только на одном из его выходов, т.е. двоичные дешифраторы преобразуют двоичный код в код «1 из N». Активным всегда является только один выход дешифратора, причем номер этого выхода однозначно определяется входным кодом. На принципиальных схемах в условном обозначении дешифраторов ставятся буквы DC (от английскогоDecoder) (рис.4). Входы дешифраторов обозначаются двоичными весами 1-2-4-8. В отечественных микросхемах маркировка дешифраторов содержит две буквы ИД, например, К555ИД4, 564ИД5.

Рис.4 В стандартные серии микросхем входят дешифраторы на 4 выхода (2 разряда входного кода), на 8 выходов (3 разряда входного кода), на 16 выходов (4 разряда входного кода), двоично-десятичный дешифратор (ИД6). Они обозначаются 2-4, 3-8, 4-16, 4-10. Имеются дешифраторы управления различного типа светоизлучающими индикаторами. Дешифраторы при относительно малом числе элементов и несложной внутренней структуре имеют большое число внешних выходных выводов. Поэтому не изготавливают дешифраторов с более, чем 4 информационными входами. Увеличение числа выходов осуществляется путем наращивания разрядности (рис. 5).

Рис. 5 Выходы дешифратора первой ступени подключают к стробирующим входам С разрешения/запрета работы дешифраторов второй ступени. Из дешифраторов второй ступени активным будет только один выход только одного из дешифраторов. При использовании на второй ступени дешифраторов 3-8 получаем устройство с 24 выходами. Преобразователи кодов На основе каскадного включения дешифратора и шифратора (рис.6) можно строить различные схемы: преобразования кодов: формирователи произвольных логических функций, преобразователи из одной системы счисления в другую, схемы управления различными индикаторными устройствами и т. д. Для реализации нужного закона преобразования необходимо соответствующим образом подобрать соединения выходов дешифратора со входами шифратора.

Рис.6 На функциональных схемах преобразователи кодов обозначаются X/Y. Пример обозначения преобразователя с пятиразрядным входным и шестиразрядным выходным кодами представлен на рис.7. ВходЕО является входом разрешения выхода.

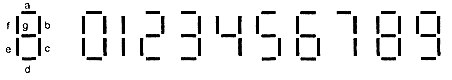

Рис.7 Часто используемым преобразователем кодов является преобразователь двоично-десятичного кода в код семисегментного индикатора. Рассмотрим пример управления семисегментным светодиодным либо жидкокристаллическим индикатором (рис.8).

Рис.8 Такие индикаторы при различных комбинациях светящихся элементов высвечивают цифры от 0 до 9. Для цифры 0 необходимо погасить сегмент g, а остальные должны светится. Для цифры 1 — светятся сегментыb и с; сегментыa, d, e, /,g погашены и т. д. Сегмент будет гореть, если на него будет подано напряжение логического нуля. Сегмент будет погашен, если на него будет подано напряжение логической единицы. Это соответствует подключению общего для всех сегментов электрода к напряжению питания. Запишем таблицу истинности для данного преобразования кодов. Таблица преобразования десятичного кода в семисегментный

Такой преобразователь легко синтезировать с использованием каскадно включенных четырехвходового дешифратора и шифратора кодов с семью выходами. Дешифратор преобразует двоичный код в номер выбранного проводника (одного из десяти), а шифратор по номеру входа вырабатывает код управления сегментами. |

||

|

Последнее изменение этой страницы: 2018-05-10; просмотров: 467. stydopedya.ru не претендует на авторское право материалов, которые вылажены, но предоставляет бесплатный доступ к ним. В случае нарушения авторского права или персональных данных напишите сюда... |