Студопедия КАТЕГОРИИ: АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция |

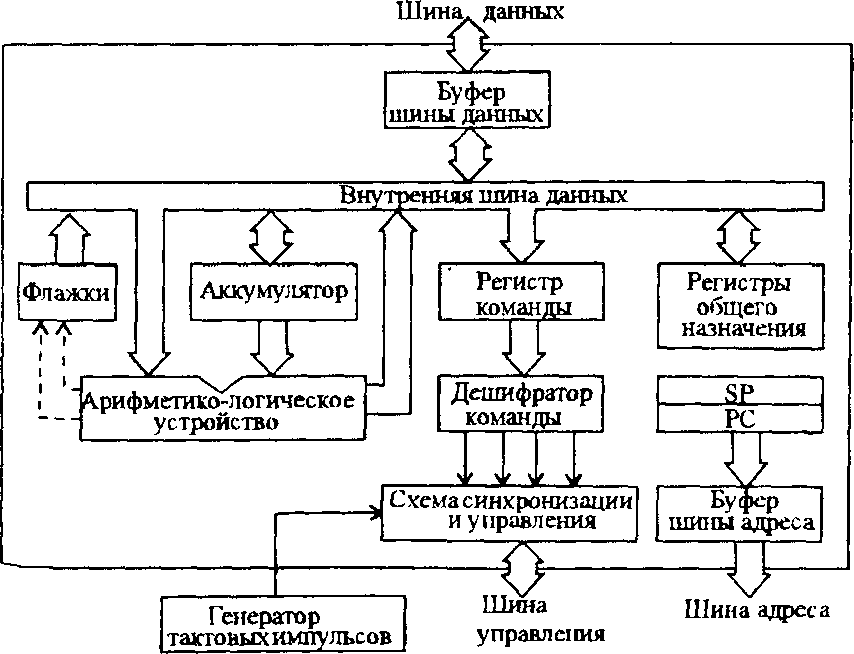

ВНУТРЕННЯЯ АРХИТЕКТУРА МИКРОПРОЦЕССОРОВМикропроцессором называется программно-управляемое устрой- ство на одной или нескольких ИС, осуществляющее обработку цифровой информации и управляющее этим процессом. МП может принимать, дешифрировать и выполнять команды, представленные в двоичном коде Типичная внутренняя организация МП приведена на рис. 7 2. Основными внутренними компонентами МП являются арифметико-логическое устройство (АЛУ), реализующее множество арифметических и логических функций МП, узел синхронизации и управления,воспринимающий и генерирующий внешние управляющие сигналы; набор регистров для временного хранения кодов команд, данных, адресов и информации о внутреннем состоянии МП. Содержимое некоторых из внутренних регистров МП может быть изменено программным путем, другая их часть недоступна программисту. Безусловно, общее число внутренних регистров МП разных семейств различно, как различны конкретные функции, выполняемые ими, и обозначения доступных программисту регистров. Тем не менее для всего многообразия внутренних регистров МП характерны следующие наиболее важные их виды. Регистр команды воспринимает код текущей команды с шины данных и осуществляет его хранение в течение всего времени ее исполнения. Регистр команды не доступен программисту. Для хранения данных и промежуточных результатов в МП используются программно доступные рабочие регистры. Если все рабочие регистры в составе МП позволяют непосредственно записывать в них результаты вычислений, выполненных АЛУ, их обычно называют регистрами общего назначения (РОН). Если в МП имеется всего лишь один такой специализированный регистр, его называют аккумулятором.

Рис. 7.2 Типичная внутренняя организация микропроцессора

Регистры для хранения адресов (указательные регистры) также программно доступны. К указательным регистрам относятся программный счетчик (другое наименование — указатель команды), а также регистры — указатели стека. Программный счетчик (PC) обеспечивает хранение двоичного кода адреса ячейки памяти, где помещена команда, которую предстоит выполнить процессору вслед за исполняемой им в данный момент командой. Новый цикл выбора команды МП всегда начинается с того, что на его шине адреса появляется содержимое PC, и очередная команда по этому адресу переписывается с шины данных в регистр команд, после чего она поступает на дешифратор команды. Выходы дешифратора подключены к узлу синхронизации и управления, определяющему требуемое для выполнения этой команды направление передач данных и реагирующему на внешние сигналы, поступающие по шине управления от других устройств. В процессе исполнения команды содержимое PC автоматически увеличивается; таким образом, в любой момент времени его содержимое представляет собой адрес очередной ячейки памяти, где может храниться либо следующая команда, либо дополнительные данные, привлекаемые МП для исполнения данной команды. Регистр — указатель стека ( SP ) используется для хранения адреса последней использованной ячейки стека ( области памяти, размер которой изменяется в процессе обработки). Работа стека организована по принципу «последним пришел — первым вышел". При записи данных в стек содержимое регистра SP автоматически уменьшается, и по этому адресу данные заносятся в память. При удалении данных из стека они переписываются из ячейки, адрес которой хранится в SP, после чего его содержимое автоматически увеличивается. Таким образом этот регистр всегда следит за положением вершины стека (наиболее удаленной от начала стека ячейки памяти). Информация об особенностях результата последней операции, выполненной АЛУ ( информация о внутреннем состоянии МП ), хранится в регистре флажков ( другие его названия — регистр состояния, регистр кода условия ). В МП-технике так обычно называют простой набор триггеров, состояния которых зависят от результатов операции АЛУ (строго говоря, простой набор отдельных триггеров нельзя называть регистром, но применительно к МП это не вызывает особых недоразумений ). Каждый триггер в составе регистра состояния устанавливается (или сбрасывается) при какой-то своей особенности результата в АЛУ (например, триггер нуля Z, переполнения V, отрицательного результата N, переноса С и др.). Регистры состояния программно доступны, причем программист может установить (или сбросить) каждый триггер в отдельности или одновременно весь регистр. Рассмотренные выше основные компоненты в составе МП связаны между собой быстродействующей внутренней шиной данных, а его внешние шины отделены от нее буферными каскадами, повышающими нагрузочную способность внешних шин. Отметим, что разрядность МП определяется числом бит данных, которое обрабатывается в одной операции АЛУ, и всегда равна числу проводников внешней шины данных. Объем адресуемой памяти МП зависит от числа проводников внешней адресной шины. Нетрудно убедиться в том, что с помощью адресной шины из N проводников МП может передать 2N различных двоичных адресов ячеек памяти. Всякому внешнему устройству ввода — вывода также присваивается определенный адрес, что позволяет МП осуществлять операции ввода — вывода подобно обращению к обычной ячейке памяти. Все операции в МП инициируются импульсами синхронизации от внешнего (реже встроенного) генератора тактовых импульсов, стабилизированного кварцевым резонатором. По значению частоты следования импульсов синхронизации в первом приближении можно судить о быстродействии МП. При прочих равных условиях оно тем больше, чем выше частота синхронизации. Первые образцы МП работали при частотах тактового генератора 2 — 4 мГц, для современных МП типичны значения частоты порядка 60 — 200 мГц и выше. 8-разрядные МП ( например, такие широко распространенные МП, как Intel 8080 и разработанный примерно в то же время не менее популярный МП МС6800 фирмы "Motorola"; отечественный КР580ВМ80А; более совершенные Intel 8085, MCS6502, Z80, МС6809 и другие) выпускаются в виде ИС с 40 контактами при двухстороннем расположении выводов. Их шина адреса содержит 16 проводников, поэтому они непосредственно могут адресоваться к 65536 ячейкам (64 кбайт) памяти. Все эти микропроцессоры при одинаковой внутренней архитектуре, как на рис. 7.2, различаются некоторыми конструктивными особенностями, функциями и количеством программно доступных внутренних регистров и, как следствие этого, наборами используемых команд. Например, МП Intel 8085 отличается от своего предшественника (Intel 8080) наличием встроенного генератора тактовых импульсов, а также мультиплексированием (использованием одних и тех же выводов) шины данных с половиной шины адреса. Разработанный на основе семейства Intel 8080/8085 более совершенный МП Z80 может выполнять все программы, записанные в машинных кодах МП Intel 8085. Обратное же достигается не всегда, так как МП Z80 имеет больше программно доступных внутренних регистров, поэтому не все его команды могут быть исполнены МП Intel 8085. Как правило, все последующие расширения набора команд МП одного семейства выполняются совместимыми на уровне машинных кодов, чтобы для последующих разработок можно было использовать все наработанное ранее программное обеспечение (совместимость снизу вверх). 8-разрядные МП, в основном, предназначены для создания на их основе микроконтроллеров — относительно несложных МС, широко применяемых в промышленности и в быту в качестве различных систем управления, воспринимающих сигналы ( например, контактных ) датчиков и выдающих исполнительным механизмам несколько управляющих сигналов ( типа включить / выключить). 16-разрядные МП обычно имеют 64-контактный корпус также с двухрядным расположением выводов. По сравнению с 8-разрядными основные преимущества этих МП заключаются в расширении набора команд, более быстром их исполнении и увеличенном объеме адресуемой памяти (обычно 1 Мбайт и более). Общепризнанным лидером на рынке 16-разрядных микропроцессоров считается фирма "Intel”. Популярные 16-разрядные МП (например, открывшие эру ПЭВМ МП семейства Intel 8086 / 8088 и более мощные 80186, 80286; отечественный МП КМ1810ВМ86 и другие) представляли собой не просто усовершенствование раннее описанных МП (Intel 8080 / 8085), а содержали некоторые принципиальные решения в области разработки новых конфигураций центральных и специализированных микропроцессоров, позволяющих значительно повысить их быстродействие. Увеличение быстродействия в 16-разрядных МП достигается путем улучшения организации процесса вычислений и применения дополнительных аппаратных средств. Среди архитектурных особенностей 16-разрядных МП отметим несомненную находку, связанную с применением для более быстрого исполнения команд принципа конвейеризации. Так называют специальную организацию работы МП, при которой каждая очередная команда заносится в регистр команд не из памяти, а выбирается из очереди команд. Для этого перед регистром команды дополнительно включается сверхбыстродействующий блок памяти, в который предварительно из памяти переписываются несколько очередных команд (очередь команд). Длина очереди составляет 6 байт (для МП 8086) и 4 байта (для МП 8088). Такой подход позволяет существенно повысить скорость выполнения программы за счет сокращения простоев быстродействующего процессора в промежутках времени, когда производится относительно более медленное обращение к памяти. К дополнительным аппаратным средствам относят разработанный фирмой "Intel” специализированный процессор 8087 (более совершенный его вариант i80287) для ускоренного выполнения арифметических операций (с большими числами). Он подключается к шинам адреса/данных, а также к некоторым линиям шины управления и действует как вспомогательный процессор (арифметический сопроцессор). Сопроцессор 8087 контролирует командный поток, и в случае обнаружения специально зарезервированного кода команды он выполняет, а основной МП игнорирует ее. Сопроцессор может с повышенной точностью выполнять все арифметические операции и вычислять значения таких сложных математических функций, как логарифмические, тригонометрические и обратные тригонометрические функции; возведение в степень; извлечение корня и др. Следует особо подчеркнуть, что сопроцессор не может работать изолированно от центрального МП, но вместе они образуют мощный тандем, обеспечивающий в задачах численной обработки в 10 — 50 раз более высокую производительность. Отметим также, что и в 16-разрядных МП в целях экономии числа внешних выводов НС часто применяется описанное ранее мультиплексирование шин данных и адреса. 32-разрядные МП имеют от 60 до нескольких сотен контактов (МП Pentium —- 296, PentiumPro — 387 контактов ), расположенных либо по всем четырем сторонам корпуса, либо в узлах прямоугольной сетки, условно нанесенной на его поверхность ( матричное размещение выводов). Как правило, шина адреса таких МП также состоит из 32 проводников, поэтому современные 32-разрядные МП обладают весьма большим диапазоном адресации памяти (4 Гбайт). Об их исключительно высокой производительности можно судить, хотя бы по типичным значениям частоты тактового генератора 100; 133; 166 и даже 200 мГц (вместо 10 мГц для лучших образцов 16-разрядных МП). При разработке 32- ра зрядных МП описанные выше тенденции по дальнейшему совершенствованию организации вычислительного процесса получили свое дальнейшее развитие и привели к использованию в них так называемой кэш-памяти и других дополнительных средсгв управления памятью. Кэш-памятью называют сверхбыстродействующую память для хранения в ней наиболее часто адресуемых команд и данных. Дело в том, что для большинства используемых программ характерна тенденция более частого обращения к одним и тем же адресам памяти, и содержимое по этим адресам ( вместе с самими адресами) заносится в кэшпамять, которая либо встраивается в сам МП, либо помещается между МП и основной памятью. При выполнении программы кэш-память определяет, не совпадает ли запрашиваемый МП адрес с ее содержимым. В случае совпадения (удачного "попадания") команда считывается из быстродействующей кэш-памяти без обращения к относительно медленной основной памяти. При достаточно высоком проценте удачных попаданий достигается заметное увеличение быстродействия всей системы. Очевидно, чем больше кэш-память, тем больше и удачных попаданий (объем кэш-памяти современных МП может достигать сотен кбайт ). Дополнительные средства управления памятью обеспечивают эффективное распределение областей памяти между различными программами (и их данными), а также их защиту от наложения друг на друга. Обычно они встраиваются в сам МП или выполняются в виде отдельных ИС. К наиболее популярным 32-разрядным МП относятся уже упоминавшийся ранее МП Intel 80386 и его последующие модификации (i80386DX; более дешевый i80386SX; экономичный i80386SL), Intel 80486 и его модификации, IntelPentium и описанные ранее все его модификации вплоть до PentiumPro; Motorola MC68020; NS32032 фирмы "NationalSemiconductor"; Z80000 фирмы "Zilog" и др. Все 32-разряд- ные МП могут работать с сопроцессорами ( например, использовать указанный ранее Intel 80287 или более совершенный арифметический сопроцессор 80387), а микропроцессоры i486 ( кроме i486SX ) даже имеют встроенный арифметический сопроцессор Относительно недавно семейство специализированных микропроцессоров пополнилось еще одним новым видом — графическим сопроцессором, предназначенным для широкого применения в видеомониторах (дисплеях ) ПЭВМ, издательских системах, а также системах компьютерного моделирования и обработки изображений. Графические сопроцессоры оптимизированы на выполнение операций, связанных, например, с получением перемещающихся изображений и трехмерной графикой. Естественно, что такие графические операции они выполняют намного быстрее основного МП. Основной МП посылает графическому сопроцессор) специальные команды или даже подпрограммы, которые тот выполняет, работая с ним параллельно, что существенно увеличивает быстродействие всей системы. Одним из первых графических сопроцессоров была ИС 182786. предназначенная для работы с 32-разрядным МП i80386. Наиболее популярным графическим сопроцессором, используемым в современных IBM-совместимых компьютерах, является И С TMS34020 фирмы TexasInstruments. Она имеет в своем составе 32-раз- рядное АЛУ, тридцать один 32-разрядный регистр, сумматор, локальную память и кэш-память команд емкостью 512 байт. Конвейерный принцип обработки команд позволяет совместить в сопроцессоре обращения к локальной памяти, необходимые вычисления и выполнение графических команд. ИС TMS34020 работает с тактовой частотой 40 МГц. При работе с интенсивными вычислениями при цифровой обработке изображений, трехмерной графикой и т.п. в ней предусмотрена возможность подключения до четырех дополнительных арифметических графических сопроцессоров TMS34082. При подключении арифметического сопроцессора TMS34082 производительность ИС TMS34020 увеличивается примерно в 4 раза.

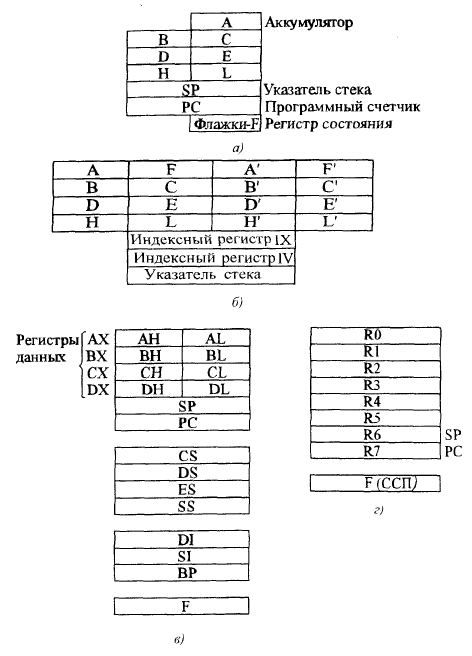

Вопрос 7.3. Чем определяется разрядность МП ? Варианты ответа. 7.3.1. Числом проводников его внешней шины данных. 7.3.2. Числом проводников его внешней шины адреса. 7.3.3. Числом проводников его внешней шины управления. Вопрос 7.4. Чем определяется предельно возможный объем памяти, к которой может адресоваться МП ? Варианты ответа: 7.4.1. Числом ячеек памяти ЗУ. 7.4.2. Сложностью программ, которые МП должен выполнять. 7.4.3. Разрядностью его шины данных. 7.4.4. Разрядностью его шины адреса. Вопрос 7.5. Каково назначение рабочих регистров МП ? Варианты ответа: 7.5.1. Рабочие регистры служат для расширения памяти МС . 7.5.2. Рабочие регистры хранят коды команд, которые должен выполнять МП. 7.5.3. Рабочие регистры хранят адреса команд, которые должен выполнять МП. 7.5.4. Рабочие регистры содержат элементы данных, обрабатываемые МП. 7.3 БАЗОВЫЕ КОМАНДЫ МИКРОПРОЦЕССОРОВ До сих пор в основном говорилось об аппаратных средствах МС. Для эффективного применения МС не менее важна и роль соответствующего программного обеспечения — совокупности управляющих и вычислительных программ, а также средств автоматизации этапов их подготовки и опиадки Для полного представления о возможностях любого МП, кроме внутренней архитектуры, необходимо также изучить его систему команд. Машинная команда преоставляет собой некоторый двоичный код. Указывающий микропроцессору. какую операцию он оогжен выполнить, где хранятся привлекаемые Оля этой операции данные и кудадолжен быть помещен ее результат.Для различных семейств МП конкретные машинные коды команд могут различаться, полный же их набор часто называют системой команд (современные МП могут иметь д0нескольких сотен команд). Поскольку МП способен воспринимать только длинные цепочки битов, работать с которыми утомительно, для удобства используют более компактную запись команд в виде кода с основанием 8 или 16. Чаще всего ( например, для МП семейства Intel ) применяют 16 - ричный код позволяющий для каждого байта записывать всего лишь две 16-ричные цифры. 16-ричное кодирование имеет очевидное преимущество перед двоичным, однако для сложных и длинных программ и оно неудобно Написание, чтение и отладка программ еще более упрощается при использовании записи команд в мнемокоде, когда каждой команде присваивается определенный набор букв, напоминающий действие этой команды ( например, мнемоника MOV*[10] соответствует команде пересылки данных ). Такие машинно-ориентированные языки программирования МП называют ассемблерами (для разных семейств МП могут быть свои ассемблеры) При помощи специальной программы цепочка команд затем автоматически переводится в двоичные коды, причем этот процесс очень напоминает обычный перевод со словарем иностранного текста. Безусловно, набор команд конкретного МП всегда отражает индивидуальные особенности его архитектуры, тем не менее для всех МП можно выделить базовый набор команд, состав и число которых необходимы и достаточны для написания программы любой сложности. При изучении системы команд любого МП удобно группировать их по некоторым специфическим признакам. Например, в зависимости от выполняемых функций все команды базового набора могут быть отнесены к одной из следующих групп: команды передачи данных (из памяти в регистр и наоборот, пересылка из регистра в регистр ); арифметические и логические команды (сложение и вычитание, для более совершенных МП — умножение и деление, сравнение, сдвиг разрядов влево или вправо, логические операции И, ИЛИ, НЕ и др.), команды переходов из одной точки программы в другую (в том числе, так называемые, условные переходы по результатам предыдущей операции и т.п ), команды управления (работой МП; вводом — выводом, работа со стеком и др) Другой способ разделить команды на группы — по количеству различных данных, используемых командой для выполнения ее действия. Любое необходимое для некоторой операции данное в общем случае называют операндом, различая при этом такие понятия, как операнд-источник и операнд-приемник. Операндом-источником называют используемое в операции данное, значение которого в процессе выполнения операции не изменяется. Если некоторый операнд необходим для данной операции и его значение изменяется в процессе ее выполнения, его называют операндом-приемником. В зависимости от числа привлекаемых операндов все команды МП могут быть отнесены к трем основным типам —безадресные, одноадресные и двухадресные команды. Безадресные команды выполняют свои действия без ссылок на операнды. Сопоставляя эту классификацию с предыдущей, приходим к выводу, что к безадресным командам относится часть команд управления работой МП (например, такие команды, как HLT-останов или прекращение МП всех операций; WAIT — когда МП ожидает завершения другим устройством более медленной операции и т.п.). Одноадресным командам для выполнения своих действий требуется всего один операнд-приемник. К ним относятся, например, команды очистки содержимого программно доступных регистров (с мнемоникой CLC), увеличения (инкремента) или уменьшения (декремента) на единицу содержимого РОН (используются при организации циклов выполнения однотипных действий) и др. Наконец, двухадресные команды для выполнения своих действий требуют двух операндов, один из которых после операции будет содержать ее результат (операнд-приемник), а другой (операнд-источник) и после операции будет хранить свое содержимое неизменным. Напомним, что в некоторых МП в качестве приемника может быть использован только один рабочий регистр ( аккумулятор), а в качестве источника —любой другой рабочий регистр. Другим ограничением, вводимым из соображений уменьшения длины команды, является обязательное использование в двухадресных командах как минимум ссылки хотя бы на один регистр (запрещены операции с содержимым двух ячеек памяти). В самом общем случае, все команды пересылки, арифметических и, частично, логических операций должны быть отнесены к двухадресным командам. Любая одноадресная и двухадресная команда должна указывать МП, где помещены необходимые для ее исполнения операнды. Используемые Для этого приемы часто называют способами адресацгш Названия отдельных способов адресации для МП различных семейств могут несколько отличаться, но их смысл в общих чертах всегда сводится к следующему. Сам операнд или его адрес может непосредственно следовать за кодом команды, операнд или его адрес может быть содержимым одного из рабочих регистров. Наконец, в очередной ячейке после ячейки с кодом команды может содержаться некоторое число (смещение), которое еле. дует прибавить к содержимому одного из указываемых рабочих регистров, чтобы получить адрес операнда. Указанное сложение внутри МП реализовано аппаратно и выполняется автоматически. Аппаратные средства современных МП также поддерживают несколько эффективных способов адресации, ориентированных на работу с цепочками данных, размещенных в соседних ячейках памяти. Например, при автоинкрементном способе адресации операнд выбирается по адресу в одном из регистров, после чего его содержимое автоматически увеличивается (инкрементируется) так, что к следующему обращению в нем содержится адрес следующей ячейки данных. При автодекрементном способе до операции содержимое адресуемого регистра автоматически уменьшается (декрементируется) и операнд извлекается по этому адресу *[11]. Любой микропроцессор может быть представлен своей программной (регистровой) моделью, показывающей ресурсы МП, которыми программист может распоряжаться при разработке программ. Для сравнения на рис. 7.3 показаны программные модели четырех различных семейств МП. двух семейств 8-разрядных МП Intel 8080/8085 (МП КР580ВМ80А) и Z80, а также двух семейств 16-разрядных МП Intel 8086/8088 (МП KM18WBM86) и отечественного семейства К1801 (МП типов К1801ВМ1; К1801ВМ1Г: К1801ВМ2 ). Какже указывалось ранее, первые три из показанных на рис. 7 3 моделей МП совместимы снизу вверх, в то время как МП семейства К1801 имеют совсем другую систему команд. МП этого семейства были разработаны для решения инженерно-технических и экономических задач, для применения в системах управления технологическими процессами, в системах связи и контрольно-измерительной аппаратуре. В частности, на их основе разработан ряд получивших весьма широкое распространение отечественных микроконтроллеров и управляющих систем семейства «Электроника».

Рис. 7.3. Программные модели некоторых микропроцессоров а — МП Intel 8080/8085 (КР580ВМ80А). б — МП Z80, в — МП Intel 8086/8088 (КМ1810ВМ86), г — МП семейства К1801 Как следует из рассмотрения рис. 7.3,а, 8-разрядные МП семейства Intel 8080 / 8085 (КР580ВМ80А), помимо аккумулятора А, содержат шесть 8-битных рабочих регистров, обозначаемых буквами В, С, DЕ И и L.8-битный регистр флажков F, а также два 16-разрядных указательных регистра PC и SP Назначение и принцип работы всех этих регистров полностью соответствует приведенному ранее классическому описанию с тем лишь небольшим дополнением, что в некоторых командах возможно объединение 8-битных регистров в регистровые пары ВС, DE и HL, используемые для работы с 16-разрядными словами или для хранения 16-битных адресов данных. По сравнению с МП семейства Intel 8080/8085, МП Z80 имеет вдвое большее число рабочих регистров, два регистра состояний (F и F') и два дополнительных 16-битных индексных регистра (IX и IY ) для адресации данных. Внутренние рабочие регистры А, В, С,D,Е, Н, L и регистр флажков F в программной модели МП Z80 (см. рис.7 3,6) аналогичны соответствующим регистрам МП Intel 8080/8085. Использование второго точно такого же набора регистров А’, В’, С’,D’,Е’, Н’, L’ и F') позволяет программисту значительно реже обращаться к памяти, из-за чего, в конечном счете, и достигается более высокое быстродействие MTIZ80. Все 14 внутренних регистров МП Intel 8086/8088 ( КМ1810ВМ86 ) выполнены 16-разрядными ( см. рис. 7.3, в ), из них 4 рабочих регистра (АХ, ВХ, СХи DX) допускают независимое обращение к своим младшим (AL, BL, CL и DL) и старшим (АН, ВН, СНи DH)байтам. Совместимость снизу — вверх с более ранними8-разрядными МП достигается на уровне машинных кодов при условии, что роль аккумулятора 8-разрядного МП выполняет младшая часть ALрегистра АХ,а вместо регистровых пар ВС, DEи HLиспользуются соответственно регистры ВХ, СХи DX.В остальных же командах 16-разрддного МП все его рабочие регистры работают как регистры общего назначения (РОН) Набор указательных регистров в 16-разрядных МП семейства Intel расширен до 9 регистров Помимо описанных ранее счетчика команд PC и указателя стека SP, используемого для хранения адреса вершины стека, программная модель (см рис 7.3, в) включает в себя четыре дополнительных регистра CS, DS, ESи SS,обеспечивающие работу с объемом памяти до 1 Мбайт, два индексных регистра S1и D1для работы с цепочками данных и еще один дополнительный указательный регистр ВР,с помощью которого легко организуется простой доступ к любым данным в пределах стека. МП аппаратно поддерживает большинство из описанных выше способов адресации, поскольку индексные и указательные регистры, подобно обычным РОН, могут участвовать в арифметических и логических операциях Программная модель МП семейства К1801 (см. рис. 7.3, г), помимо регистра состояния ( называемого словом состояния процессора — ССПсодержит 8 РОН (их обозначения R0 — R7), каждый из которых может использоваться как для выполнения арифметических и логических команд, так и для операций с адресами. Некоторые из указанных РОН также выполняют специальные функции, например, регистр R7 выполняет роль указателя команд, aR6 используется в командах, связанных с операциями со стеком. В огличие от описанных ранее семейств, МП семейства К1801 отличаются более развитой и весьма гибкой системой команд. Они поддерживают все (в том числе и самые сложные — косвенные) способы адресации, а также допускают в одной команде непосредственные операции между двумя ячейками памяти. МП К1801ВМ1 позволяет адресоваться к 64 кбайт памяти, а вдвое более производительный МП К1801ВМ2 допускает расширение адресного пространства до 128 кбайт. Последняя разработка МП этого семейства (К1801ВМЗ) отличается еще более высокой производительностью, обеспечивает возможность подключения арифметического сопроцессора и позволяет работать с объемом памяти до 4 Мбайт. Таким образом, при сохранении своих индивидуальных особенностей в процессе дальнейшего совершенствования МП различных семейств происходит взаимный обмен удачными идеями и архитектурными решениями. Полное описание всех выполняемых команд обычно приводится в специальных руководствах по применению конкретного МП и включает в себя двоичный код (формат) команд, его компактную запись восьмеричным или шестнадцатеричным кодом, мнемонику команд и описание их действия с необходимыми пояснениями и примерами. Особую часть описания команды составляет указание о ее влиянии на признаки состояния процессора, сведения о которых необходимы программисту Для управления ходом выполнения вычислительного процесса при помощи, так называемых, команд ветвления. В составе этого типа команд имеются команды безусловных и условных ветвлений, обращения к подпрограммам и команды прерываний. Безусловное ветвление применяется в том случае, когда очередная исполняемая команда программы по каким-либо причинам размещена в другой области памяти. Команды условных ветвлений позволяют изменить порядок вычислений в зависимости от ранее полученного результата. Как правило, при выполнении таких команд МП автоматически анализирует состояния одного из битов регистра флажков, которое тот приобрел в результате предающих операций. При выполнении проверяемого условия содержимое бистра PC изменяется, указывая на адрес ячейки памяти, где содержится выполняемое по этому условию продолжение программы В про. тивном случае выполняется следующая команда основной части программы. Примерами таких команд являются ветвление по нулю, ветвление при достижении отрицательного (или положительного) результата и другие подобные им команды. В случае необходимости программист может предварительно воспользоваться специальной командой проверки (например, состояния одного из рабочих регистров), единственное действие которой состоит в установке битов флажков по результатам анализа содержимого указываемого регистра, а затем применить требуемую команду ветвления. В виде подпрограмм обычно оформляются наиболее часто используемые секции программы. Это могут быть вычисления значений каких- либо функций, а также любые последовательности операций, обращение к которым в основной программе проводится несколько раз. Такой механизм позволяет более эффективно использовать память, так как вместо многократного размещения одной и той же последовательности команд в нескольких участках основной программы он позволяет один раз записать ее, например, в конце основной программы. При этом в нужных местах основной программы применяется команда обращения к подпрограмме (общая мнемоника таких команд — CALL), адресная часть которой указывает МП место размещения требуемой подпрограммы. В процессе выполнения подпрограммы (это, конечно, зависит от ее сложности) МП может использовать все (или почти все) его рабочие регистры, поэтому для продолжения вычислений после возврата из подпрограммы их старое содержимое (а также содержимое регистра флажков) должно быть сохранено. Для возврата к основной программе также следует запомнить и адрес следующей команды (содержимое регистра PC) за командой обращения к подпрограмме (адрес возврата). Как правило, при обращении к подпрограмме вся необходимая для возврата к основной программе информация записывается в стеке. В некоторых МП (например, МС6800) такое сохранение выполняется автоматически, в других — организуется программно в тексте подпрограммы. В конце подпрограммы прежнее содержимое рабочих регистров восстанавливается, и по команде возврата из подпрограммы записанный в стеке адрес возврата заносится в регистр PC Иногда возникает необходимость заставить МП автоматически выполнить одну из набора специальных программ, когда в программе или в вычислительной системе возникают некоторые определенные условия Такие действия называют прерыванием, а выполняемую при этом программу — процедурой прерывания. Различают внутреннее и внешне прерывания Внутреннее прерывание исполняемой программы вызывается состоянием самого МП, а внешнее — специальным сигналом, подаваемым в МП от обслуживаемого им внешнего устройства. Например, необходимость внутреннего прерывания возникает, когда в исполняемой МП программе имеет место попытка деления на нуль (ошибка в вычислениях) или когда МП выявляет, что поступивший в регистр команды двоичный код не соответствует ни одной из его команд (ошибка в программе). Внешние прерывания чаще всего используют при организации обслуживания МП нескольких параллельно работающих внешних устройств. Процедура прерывания во многом подобна переходу к подпрограмме с той лишь разницей, что каждая из исполняемых в ней специальных программ не связывается с какой-либо конкретной программой, а располагается по фиксированному адресу. Существуют различные вариантыреализации процедур прерывания, но чаще всего при выполнении усло- вия для прерывания МП завершает текущую команду, заносит содержимое регистра флажков и указателя PC в стек, а затем обращается к вектору прерывания (зарезервированной для каждого вида прерывания ячейке памяти, где записано новое содержимое регистра состояния и адрес программы, выполняемой им в этом случае). Одним из примеров внешних прерываний является, так называемый, сброс, генерируемый при включении МП или при нажатии кнопки RESET на лицевой панели ПЭВМ. В этом случае МП всегда начинает выполнение программы начальной установки с некоторого фиксированного начального адреса. Обычно двоичный код этого адреса состоит из нулей во всех его битах. Возврат из прерывания осуществляется аналогично выходу из подпрограммы. Вопрос 7.6. При выполнении некоторой двухадресной команды один из рабочих регистров МП использовался в качестве регистра-источника. Каким будет его содержимое после выполнения следующих нескольких команд, если ни в одной из них к нему не было обращения ? Варианты ответа: 7.6.1 (7.7.1). Содержимым регистра будет результат, который в нем был до исполнения указанной двухадресной команды. 7.6.2 (7.7.2). Содержимым регистра будет результат исполнения указанной двухадресной команды. 7.6.3 (7.7.3). Содержимым регистра будет результат исполнения следующей команды после указанной двухадресной команды. 7.6.4 (7.7.4). Содержимым регистра будет результат исполнения последней из указанных нескольких команд. Вопрос 7.7. Среди указанных выше вариантов ответа выберите правильный ответ, если в условиях вопроса 7.6 речь будет идти о регистре приемнике Вопрос 7.8. При обращении к подпрограмме содержимое всех регистров МП в некотором порядке поочередно записывается в стек. Каким должен быть порядок восстановления их содержимого из стека при выходе из подпрограммы с тем, чтобы можно было сразу продолжить основную программу (без дополнительных пересылок типа регистр — регистр)? Варианты ответа: 7.8.1. Порядок может быть любым. 7.8.2. Должен быть сохранен прежний порядок. 7.8.3. Порядок должен быть обратным прежнему. 7.3. ЗАПОМИНАЮЩИЕ УСТРОЙСТВА Современные цифровые электронные устройства (ЦЭУ) и, в частности, МС и ПЭВМ обычно используют три вида памяти: постоянную, оперативную и внешнюю. Постоянная память обеспечивает хранение информации, которая не должна изменяться в ЦЭУ в ходе выполнения программ, в оперативной памяти хранится переменная информация, допускающая изменение своего содержимого в ходе вычислительных операций. Первые два вида памяти реализуют при помощи различного рода запоминающих устройств. В бытовой технике, например, в телевизорах пятого поколения или в радиоприемниках с цифровой настройкой ЗУ применяются для хранения значении параметров, определяющих режимы их работы (частот каналов настройки, установленных уровней громкости, яркости, контрастности и т.п.). В современной цифровой технике широко используются различные виды запоминающих устройств (ЗУ), от отдельных триггеров и наборов регистров до специальных модулей памяти. Внешняя память предназначена для долговременного хранения больших массивов информации на оптических или магнитных носителях. Используемые для этих целей ЦЭУ обычно называют накопителями, соответственно на цифровых компакт-дисках, на гибких (флоппи) или постоянных магнитных дисках (сокращенно НГМДиПМД). ЗУ современных ЦЭУ предназначены для записи, хранения и выдачи цифровых данных и программ, для доступа к которым используется опя- санный ранее адресный принцип. Согласно этому принципу каждоя ячейке памяти присваивается определенный номер (ее адрес ), значение которого в том или ином виде указывается при каждом обращении кней Как правило, минимальной адресуемой единицей памяти являетсябайт, а обращение к машинному слову производится по адресу его младшего байта. По виду доступа к хранимой информации различают ЗУ с последовательным и произвольным доступом (выборкой). Последовательный доступ предполагает обращение к ячейкам памяти только в порядке нарастания или убывания их адресов. ЗУ с произвольной выборкой позволяют при записи или считывании обращаться к ячейкам в их составе в любом произвольном порядке. По типу используемых режимов работы различают постоянные и оперативные ЗУ. Постоянные ЗУ (ПЗУ) в основном используют только режимы хранения и считывания хранимой информации. ЗУ этого типа обладают тем преимуществом, что они могут сохранять информацию и при отключенном питании. Это свойство получило название энергонезависимости. Все ИС ПЗУ по способу занесения в них информации (программированию) делятся на масочные (ROM — ReadOnlyMemory), программируемые изготовителем; однократно программируемые (PROM — ProgrammableROM) и многократно программируемые (реп- рограммируемые) пользователем (EPROM — ErasablePROM). Последние, в свою очередь подразделяются на стираемые электрически и с помощью ультрафиолетового облучения. Для однократной записи в процессе производства ИС масочного типа используют специальные маски, задающие способ соединения отдельных элементов памяти на общем полупроводниковом кристалле, из-за чего они и получили свое название. В отличие от них в каждый запоминающий элемент ИС типа PROM включают специальные плавкие перемычки, которые при записи индивидуальной программы пользователя могут быть в определенных местах разрушены, обеспечивая возможность однократного их программирования. Наконец, репрограммируемые ИС допускают их многократное программирование после предварительного стирания ранее хранимой в них информации. В некоторых из них предусмотрена возможность электрического стирания, в других — стирание информации осуществляют интенсивным ультрафиолетовым облучением в течение нескольких секунд поверхности кристалла ИС. В 1989 г фирма "Inter анонсировала новую технологию флэш-памяти (flash), позволяющую создавать энергонезависимые ИС EPROM с электрическим стиранием, отличающиеся высокой скоростью доступа и быстрым стиранием записанной информации. Новые изделия флэш-памяти построены на основе так называемых МНОП-транзисторов (с комбинированной нитридно-оксидной изоляцией затвора). В МНОП-транзисторе, в отличие от обычного транзистора, между металлическим затвором и пленкой двуокиси кремния, изолирующей затвор от канала, помещается тонкий слой нитрида кремния. Сохранить информацию после отключения источника питания позволяет эффект накопления зарядов вблизи поверхности раздела слоев нитрида и двуокиси кремния. Пленка двуокиси кремния предотвращает перенос этих зарядов в отсутствие напряжения затвора при отключенном питании. Разработанная по флэш-технологии ИС 28F008SA представляет собой энергонезависимую СБИС EPROM емкостью 1 МБайт с временем обращения 85 не и электрическим стиранием записанной информации. Каждая ячейка памяти в ее составе выдерживает не менее 100 000 циклов записи/стирания и при отключенном питании обеспечивает время хранения записанной в ней информации не менее 10 лет. 20-мегабайтный полупроводниковый диск, изготовленный на основе ИС 28F008SA, характеризуется средней наработкой на отказ в 33,3 млн. ч, что в 333 раза превышает показатели аналогичного ПМД. В оперативных ЗУ (ОЗУ), наряду с хранением и считыванием, основной рабочей операцией также является и операция записи. Для ЗУ этого типа характерны повышенные требования к быстродействию, поэтому их обычно выполняют в виде полупроводниковых ИС на основе биполярных или МОП-транзисторов. Чаще всего в ОЗУ используют микросхемы статической и динамической памяти с произвольной выборкой, на структурных схемах их сокращенно обозначают RAM (RandomAccessMemory). ИС ОЗУ статического типа (SRAM — StaticRAM) выполняют на статических триггерах Такие ОЗУ характеризуются весьма высоким быстродействием и используются в наиболее «узких» участках системы, например, в качестве сверхоперативной памяти для кратковременного хранения промежуточных результатов, многочисленных буферных регистров для согласования скоростных характеристик различных устройств, кэш-памяти ит.п Для снижения себестоимости хранения единицы информации чаще всего применяют простейшие схемы RS-триггера на двух инверторах.

Рис 7.4 Схемы элемента динамичесуой памяти

В ИС ОЗУ динамического типа (DRAM) хранение одного бита информации осуществляется в виде заряда конденсатора, специально сформированного внутри МОП-структуры. На рис. 7.4 приведена схема элемента динамической памяти, которая, благодаря своей простоте и малому числу элементов, получила наибольшее распространение при построении современных динамических ЗУ большой емкости. При высоком уровне сигнала на адресной шине АЛ МОП-транзистор VT с индуцированным каналом открывается, и запоминающий конденсатор CQ подключается к разрядной шине РЛ, к которой в зависимости от режима работы ЗУ подключается либо вход усилителя считывания, либо выход усилителя записи. На рис. 7.4 запоминающий конденсатор показан в виде отдельного элемента, но реально его функции выполняет емкость закрытого р — «-перехода, значение которой обычно не превосходит 0,1 — 0,2 пФ. Поскольку ток утечки такого перехода имеет порядок 0,1 нА, динамический элемент памяти требует периодического (через 1 — 2 мс) восстановления (регенерации) записанного в нем состояния, иначе из-за разряда конденсатора Элементы динамической памяти для ПЭВМ конструктивно выполняются либо в виде отдельных ИС, либо в виде модулей памяти, представляющих собой стеклотекстолитовые платы с печатным монтажом и установленными на них ИС в корпусах с двухрядным расположением выводов. До недавнего времени наиболее распространенными были модули с байтовой организацией памяти емкостью 256 Кбайт; 1; 4 и 16 Мбайт. В современных модулях памяти могут использоваться ИС емкостью до 64 Мбайт. Микросхемы памяти представляют собой изделия высочайшего технологического уровня. Типичное значение времени выборки современных ИС Динамической памяти составляет 70 — 50 не. Они выпускаются рядом таких всемирно известных фирм, как '’Samsung". “Toshiba", "Motorola", ’’TexasInstruments", "Siemens" и др. Кстати, первой фирмой, выпустившей 256 -мегабайтную ИС динамической памяти, стала корейская Компания Samsung. В настоящее время усилия многих фирм — производителей памяти направлены на поиск новых схемотехнических решений, позволяющих еще больше увеличить быстродействие динамической памяти. Одним из таких решений является размещение на одном кристалле вместе с относительно медленной (35 — 40 нс), но большой по объему, динамической памятью небольшого количества быстродействующих (12 — 15 нс) ячеек памяти статического типа, выполняющих роль своеобразной кэш-памяти. Например, на одном кристалле могут находиться 4 Мбайта DRAM и всего 16 кбайт SRAM. Подобные ИС (SDRAM) уже производят фирмы "Mitsubishi", "Samsung" и "Ramtron". Как в статических, так и в динамических ЗУ для сохранения информации обязательно наличие напряжения источника питания, так как в случае даже его кратковременного (на десятки миллисекунд) отключения записанная информация теряется. До недавнего времени для устранения этого недостатка применялось резервное питание такого типа ЗУ от специально встроенных батарей или малогабаритных аккумуляторов. В схемах энергонезависимых ЗУ, позволяющих при отключенном питании в течение довольно длительного времени (до нескольких тысяч часов) сохранять записанную информацию, применяют описанные выше МНОП -транзисторы. Отечественные микросхемы ЗУ после номера серии имеют первой букву Р (для всей группы схем ЗУ), вторая буква указывает тип ЗУ. В качестве этой буквы могут быть; для ПЗУ (масочного типа) — буква Е, для однократно программируемых ПЗУ — Т, для многократно программируемых ПЗУ (энергонезависимых ОЗУ) — Р, для ПЗУ с ультрафиолетовым стиранием — Ф, для прочих ЗУ — П. Несмотря на многообразие структурных схем и технологий изготовления, все ИС ЗУ, как правило, имеют значения уровней входных и выходных сигналов, характерные для ТТЛ-схем. Вопрос 7.9.Каково принципиальное отличие ОЗУ от многократно программируемого ПЗУ? Варианты ответа: 7.9.1. ОЗУ отличаются от многократно программируемых ПЗУ меньшим временем выборки. 7.9.2. ОЗУ по сравнению с многократно программируемыми ПЗУ имеют больший объем памяти. 7.9.3. ОЗУ предназначены для хранения данных, изменяющихся в процессе исполнения программы. 7.9.4. ОЗУ допускают произвольную выборку. Вопрос 7.10. Сравните максимально возможные объемы адресуемой памяти 8- и 16-разрядного МП, если и тот и другой используй 16-разрядную шину адреса ? Варианты ответа: 7.10.1. У 8-разрядного по сравнению с 16-разрядным МП максимально возможный объем адресуемой памяти меньше. 7.10.2. У 16-разрядного по сравнению с 8-разрядным МП максимально возможный объем адресуемой памяти вдвое больше. 7.10.3. Их максимально возможные объемы адресуемой памяти одинаковы. 7.4. УСТРОЙСТВА ВВОДА /ВЫВОДА И ДРУГИЕ ВСПОМОГАТЕЛЬНЫЕ ИНТЕГРАЛЬНЫЕ СХЕМЫ Любое внешнее устройство, совершающее по отношению к МП операции ввода/вывода, можно назвать периферийным. Микросхемы ввода/вывода применяются для подключения МС к разнообразным периферийным устройствам (внешней памяти, дисплею, принтеру и другим), линиям связи с датчиками, приборами, исполнительными механизмами, индикаторами и т.п. Чаще всего микросхемы ввода/вывода приспосабливаются под сигналы каждого конкретного МП и рассматриваются производителями МП как вспомогательные аппаратные средства. Существует два основных способа организации ввода/вывода. Первый из них называют вводом/выводом, отраженным на память, и обычно используют при программировании операций ввода/вывода, когда в МП отсутствуют специальные команды для работы с внешними устройствами (как, например, в МП семейств К1801; Motorola МС6800; MC68020 и др.). Смысл его заключается в том, что внешние устройства (ВУ) считаются как бы наложенными на память МП, тогда процедура ввода/вывода по своей сути мало отличается от обращения к ячейке памяти (ввод рассматривается как считывание данных из ячейки с адресом устройства ввода, а вывод — как запись данных в ячейку с адресом устройства вывода). Большинство периферийных устройств работают много медленнее МП, поэтому в простейшем случае для них отводят пару адресов один из адресов назначают триггеру состояния внешнего устройства, а Другой — его буферному регистру данных. Тогда в программе обращения, допустим, к устройству вывода (принтеру) предусматривают, что МП проверяет его готовность (например, установлен ли старший бит реестра состояния принтера) и в случае его готовности к приему информации пересылает двоичный код данных по адресу буферного регистра. Недостатком такого подхода является уменьшение адресного пространства МП, так как занятые внешними устройствами адреса не могут быть пользованы для других ячеек памяти. При втором способе, применяемом, например, в МП семейства Intel, предполагается, что в операциях ввода/вывода могут участвовать только порты ввода/вывода, представляющие собой специальные схемы сопр^ жения, включающие в себя один или несколько регистров ввода/вывода и позволяющие подключить В У к внешним шинам МП. Каждому порту назначается свой уникальный номер (адрес порта), который указывается в команде ввода или вывода (с мнемоникой соответственно IN или OUT) и в виде двоичного кода передается микропроцессором по адресной шине. При таком способе ввода/вывода адресные пространства основной памяти и портов ввода/вывода не пересекаются. Номер порта отделяется от точно такого же по значению адреса ячейки памяти соответствующим сигналом, который МП при каждом обращении к порту выдает на шине управления. Тем самым одни и те же адреса могут быть использованы для обращения как к ячейкам памяти, так и к ВУ. Известны три основных метода управления вводом/выводом. Один из них — программный ввод/вывод был описан выше. Он обеспечивает полное управление ситуацией, но оказывается менее гибким и довольно медленным. Очевидным недостатком этого метода также является тот факт, что, пока МП занят обслуживанием одного из ВУ, запросы других внешних устройств просто игнорируются. Более приспособленным к обслуживанию нескольких ВУ (и, конечно, более сложным) оказывается такой метод управления, когда по запросу ВУ допускается прерывание обычной работы МП. Получив от внешнего устройства запрос на прерывание, МП приостанавливает выполнение текущей программы (сохранив в стеке все необходимые параметры и адрес возврата), а затем выполняет предусмотренную программой прерывания процедуру обслуживания данной ситуации, как это было описано ранее в § 7.3. Для упорядочивания обслуживания многих ВУ каждому из них назначается определенный уровень приоритета в обслуживании. При этом, как правило, наивысшим приоритетом пользуются самые быстродействующие ВУ. Наиболее эффективным, но, пожалуй, и самым сложным считается метод управления вводом/выводом, получивший название прямого доступа в память (ПДП), когда процедура ввода/вывода выполняется самим ВУ вообще без участия МП. При этом ВУ должно быть снабжено дополнительными аппаратными средствами, которые самостоятельно обеспечивают соответствующую адресацию к ячейкам памяти, а МП в эти моменты времени отключается от шин адреса и данных. Как правило, при этом МП продолжает выполнение команд текущей программы, не требующих обращения к ЗУ. По количеству одновременно передаваемых бит данных различают параллельный и последовательный ввод/вывод. Ранее уже отмечалось, что минимально адресуемой единицей данных в современных МП считается байт. Это означает, что при одном обращении к ВУ или ячейке памяти МП считывает или передает не менее 8 бит. При параллельном вводе/выводе за один цикл обращения к ВУ одновременно передаются всебит (естественно, для этого к ВУ, помимо общего провода, должны, как минимум, подходить еще 8 проводов). Последовательный ввод/вывод позволяет передать байт данных поочередно бит за битом всего по двум проводам. В соответствии с этим и порты называют последовательными, когда в них информационные биты передаются последовательно один за другим, и параллельными, когда несколько бит данных передаются одновременно. Подключение к ПЭВМ таких стандартных периферийных устройств, как принтер, клавиатура, манипулятор типа "мышь”, игровые джойстики и другие, всегда производится через специальные устройства сопряжения или адаптеры. Совокупность линий связи, устройств сопряжения, программных и вспомогательных аппаратных средств, обеспечивающую обмен данными между МП и ВУ, обычно называют интерфейсом. Так, для подключения принтера в IBM-совместимых ПЭВМ обычно используются параллельные порты, часто их называют принтер-портом. Каждый принтер-порт в адресном пространстве имеет три адреса. Первый адрес соответствует регистру данных, посылаемых от МП к принтеру. Физически чтение данных производится через специальный буфер данных. Следующий на единицу больший адрес применяется для чтения через буфер содержимого регистра состояния принтера (ошибка печати, наличие или отсутствие бумаги), который характеризует состояние принтера и процесса передачи данных. Третий порт используется для чтения состояния регистра управления принтером (начальная установка принтера, подтверждение его готовности и т.п. ). Ранние разработки параллельного интерфейса были выполнены на нескольких TTJI-микросхемах. На них выполнялось декодирование адреса, промежуточное хранение данных и формирование требуемых сигналов управления. По этой причине для стандартных параллельных интерфейсов требуется, чтобы все электрические сигналы имели ТТЛ- уровни (+5 В и 0 В). Затем широкое распространение получили ИС параллельного ввода/вывода, в которых практически все функции отдельных ТТЛ-схем были объединены в одной СБИС, выполненной по –МОПили КМОП технологии (например, отечественная ИС КР580ВВ55А; зарубежные 6820; 8255; более совершенная 82С11 и другие), тем не менее, все они по-прежнему обеспечивают ТТЛ-уровни сигналов. Известны непрограммируемые и программируемые варианты таких ИС. Программируемые ИС параллельного ввода/вывода (РIO - ProgramInput / Output) Допускают программное задание режимов работы (все порты работают только на ввод или только на вывод, часть портов используется для ввода, остальные для вывода). Современные ПЭВМ, как правило, могут работать с тремя параллельными портами, которые имеют название (логические имена) LPT1, LPT2 и LPT3. Заметим, что эффективная скорость передачи данных при использовании матричных принтеров не превышает 150, в лучшем случае 300 кбайг/с. Это слишком небольшая скорость для новых моделей печатающих устройств, поэтому в последнее время появилось несколько модификаций скоростных интерфейсов, обеспечивающих скорость передачи до 2 — 5 Мбайт/с. При передаче данных ТТЛ-уровнями максимальная длина кабеля связи в стандартном параллельном интерфейсе не должна превышать 2— 3 м. Увеличение длины кабеля до 10 м возможно только при использовании специальных усилителей, поэтому для работы с более удаленными принтерами лучше всего использовать последовательный интерфейс. Стандартный последовательный интерфейс вначале разрабатывался для связи центральной ЭВМ с многочисленными удаленными терминалами, но его простота и богатые возможности обеспечили ему более широкое применение. Основным его преимуществом является возможность передачи данных на большие расстояния, как правило, не менее 30 м. В современных МС последовательный интерфейс используется для большинства периферийных устройств, таких, как клавиатура, удаленный принтер, внешний модем (устройство для межкомпьютерного обмена по линиям телефонной связи) и др. В адресном пространстве стандартный последовательный адаптер занимает 8 последовательных портов. Для увеличения помехоустойчивости в нем по линии связи электрические сигналы передаются с болеевысокими уровнями (уровень логического нуля соответствует "+ 12 В”, логической единице — и—12 В"), но все ИС последовательного ввода/вывода обеспечивают ТТЛ-совместимые уровни электрических сигналов. Основу последовательного интерфейса составляют СБИС универсального асинхронного приемопередатчика (UART — UniversalAsynchronousReceiver/ Transmitter). При передаче они принимают с шины данных МП параллельный код с TTJl-уровнем, преобразуют его в последовательный код, а затем с более высоким уровнем передают его по линии связи, дополняя в начале и в конце посылки необходимые служебные биты (старта, останова и контроля) При приеме же, наоборот , они принимают последовательность битов с высоким уровнем, опус* кают служебные символы, преобразуют последовательный код данных в параллельный и выдают его с TTJI-уровнем на шину данных МП. В более ранних моделях IBM — совместимых ПЭВМ для этих целей применялись такие ИС, как отечественная ИС КР580ВВ51А и зарубежные 8250- 8256; 16450 и ее улучшенная версия 16550. В настоящее время все чаще используют ее последнюю модификацию UART 16550А, которая дополнительно к описанным ранее возможностям может использовать несколько каналов прямого доступа в память. IBM — совместимые компьютеры могут использоваться до четырех последовательных портов, имеющих логические имена СОМ1, COM2, COM3 и COM4. Типичное значение скорости последовательной передачи данных — 9600 бит/с, но при специальном программировании можно достигнуть скорости обмена до 115200 бит/с. В современных ПЭВМ обычно на одной плате конструктивно выполняется сразу несколько адаптеров (например, последовательного и параллельного портов, приводов гибких и жестких дисков и т.п.), обычно ее называют многофункциональной платой ввода/вывода. В некоторых моделях ПЭВМ, разработанных в последние годы, для связи с клавиатурой, лазерным принтером и другими ВУ все чаще стал использоваться беспроводной последовательный интерфейс. Его принцип действия точно такой же, как у лазерных проигрывателей компакт-дисков и т.п.). На передающей стороне такого интерфейса устанавливается инфракрасный светодиод, преобразующий электрические сигналы в световые импульсы, которые затем воспринимаются фотодиодом на приемной стороне и преобразуются им опять в электрические сигналы. Такая связь обеспечивает дополнительные удобства в эксплуатации и отличается относительно невысокой ценой и малым потреблением энергии. Обычно ее используют для передачи информации на расстояния порядка 1 м. При этом довольно легко достигаются скорости передачи от 9600 до 115200 бит/с (последнее расширение этого стандарта предусматривает увеличение скорости передачи данных до 4,0 Мбит/с). Для создания полноценной МС, помимо рассмотренных ранее вспомогательных ИС, могут понадобиться и другие, такие, как тактовый генератор, таймер и различные контроллеры. Ранее уже говорилось о том, что некоторые МП выпускаются с встроенной схемой генератора тактовых импульсов, к внешним выводам которого достаточно лишь подключить кварц. В подавляющем большинстве случаев для синхронизации работы внутренних элементов МП требуются так называемые двухфазные импульсные сигналы, представляющие собой сдвинутые во времени друг относительно друга две неперекрывающиеся последовательности такто- *bix импульсов одинаковой частоты. Такие сигналы упрощают формирование различного рода стробирующих импульсов в промежутке между Двумя тактовыми импульсами. Для МП без встроенного генератора выпускают специальные ИС, например, генераторы тактовых сигналовКР580ГФ24 и i8284, генераторы двухфазной синхронизации МС6870 МС6871, МС6875 и др. Отметим, что в пределах одного семейства МП могут выпускаться модификации, рассчитанные на разные тактовые частоты. Очевидно, что медленные МП не могут использоваться на более высоких частотах. Для многих быстродействующих МП также существу, ет ограничение и на нижнее значение тактовой частоты. Это связано с тем, что применяемая в них динамическая память постоянно требует хотя бы одной регенерации в течение определенного отрезка времени превышение которого может привести к потере информации. Еще один тип генератора импульсов может потребоваться для получения в МС отсчетов реального времени. Обычно для этого используют свой "часовой" кварц и различного рода ИС таймеров, на основе которых выполняются схемы часов реального времени. ИС программируемого таймера (К580ВИ53) имеется и в составе отечественного МП комплекта серии К580. Среди зарубежных таймеров известны КМОП-таймер 555 (например, ICM7555IPA), в IBM-совместимых ПЭВМ раньше таймер выполняли на микросхеме i8254, а сейчас в большинстве случае применяют часы реального времени MCI46818А. Ранее речь уже шла о микроконтроллерах (относительно несложных специализированных МС для различных систем управления ). Для применения в составе любых более сложных МС разработано много ИС различных контроллеров*[12], но здесь остановимся только на двух известных их видах — контроллеры прерываний и прямого доступа в память. Как известно, в любой фиксированный момент времени МП может обслуживать только одно событие, а при обслуживании многих ВУ используется прерывание по их приоритету Не исключена такая ситуация, что в некоторый момент времени одновременно поступят запросы на прерывание от нескольких ВУ или ИС ввода/вывода. ИС контроллера прерываний помогает основному МП в этой нелегкой задаче, устанавливая каждому из всех ВУ определенный уровень важности (приоритета). В первых компьютерах семейства IBM для этих целей использовалась ИС i8259 (отечественный аналог КР580ВН59), которая имела восемь входов для приема сигналов прерывания, но путем каскадного соединения таких же ИС допускала увеличение их числа до 64. Среди других контроллеров прерываний отметим также ИС МС8507 фирмы "Motorola” Контроллеры прямого доступа в память (DMA — DirectMemory’ Access) помогают В У генерировать адреса ячеек памяти и обеспечивают занесение в них данных без участия МП. Известно достаточно много ИС контроллеров ПДП, среди наиболее популярных из них — разработки фирмы "Intel" i8237, i8257 и более совершенная ИС i82258, DMA28016, отечественная ИС КР580ВТ57 и др. В IBM-совместимых компьютерах для этой дели довольно долго использовалась четырехканальная НСi8237, один из каналов которой использовался для регенерации динамической памяти, два других — для управления передачей данных от дисководов гибкого и жесткого дисков, и только один канал был доступен для дополнительного оборудования. Последующие модели ПЭВМ этого семейства уже имели семь каналов ПДП, что достигалось каскадным включением двух ИС i8237. В современных разработках описанные выше вспомогательные ИС и контроллеры, как правило, уже не используются. а все их функции реализованы в одной СБИС, обеспечивающей со своими предшественниками полную программную совместимость. В качестве примера можно привести СБИС периферийного контроллера 82С206. Функционально она заменяет два контроллера прерываний типа i8259, два контроллера ПДП типа i8237, таймер типа 18254, часы реального времени и дополнительные 100 Байт КМОП ОЗУ статического типа. Вопрос 7.11.Каково принципиальное отличие параллельного и последовательного ввода/вывода 7 Варианты ответа: 7.11.1. Они различаются длиной и числом жил кабеля связи. 7.11 2. Они различаются используемым оборудованием и типами применяемых ИС . 7.11 3. При параллельном методе информация передается и принимается одновременно байтами, а при последовательном поочередно битами. Вопрос 7.12.Чем объяснить использование в стандартных интерфейсах более одного порта ? Варианты ответа' 7.12.1. Большим объемом передаваемой информации. 7.12.2 Стремлением ускорить темпы передачи информации. 7.12.3. Необходимостью обеспечить функции управления процессом передачи данных и контроля состояния внешнего устройства Вопрос 7.13. В каких из следующих случаев целесообразно применение метода ввода/вывода с прерыванием ? Варианты ответа: 7 13.1 МП обслуживает одно внешнее устройство 7.13.2 МП обслуживает одно устройство ввода и одно устройство вывода

ЗАКЛЮЧЕНИЕ

Сферы применения микропроцессоров безграничны, а мир микропроцессорной техники неисчерпаем хотя бы потому, что с каждым годом появляются все более совершенные ее представители, для эффективного использования которых требуется изучение принципов построения совре^ менных аппаратных и программных средств. Прогресс в области разработки новейших аппаратных средств во многом обязан последним достижениям в технологии изготовления ИС, что позволило более чем в 4 раза (с 1,5 до 0,35 мкм) снизить технологические нормы для линейных размеров КМОП-транзисторов, обеспечив фантастическую плотность их размещения на одном кристалле. Одновременно это позволило существенно увеличить тактовые частоты. В настоящее время уже выпускаются МП, работающие на внешней тактовой частоте 200 мГц, а в недалеком будущем представляются вполне реальными тактовые частоты до 500 мГц. |

|||

|

Последнее изменение этой страницы: 2018-05-10; просмотров: 460. stydopedya.ru не претендует на авторское право материалов, которые вылажены, но предоставляет бесплатный доступ к ним. В случае нарушения авторского права или персональных данных напишите сюда... |

хранимая в нем информация постепенно разрушится. Это является, пожалуй, одним из основных недостатков динамической памяти, в то время как по критерию, учитывающему емкость памяти, стоимость и энергопотребление, этот тип памяти во многих случаях оказывается предпочтительнее статической. Некоторые МП (например, Z80) содержат встроенную схему регенерации памяти динамических ЗУ. В большинстве случаев современные ИС динамической памяти имеют встроенные средства регенерации, что уменьшает загрузку МП.

хранимая в нем информация постепенно разрушится. Это является, пожалуй, одним из основных недостатков динамической памяти, в то время как по критерию, учитывающему емкость памяти, стоимость и энергопотребление, этот тип памяти во многих случаях оказывается предпочтительнее статической. Некоторые МП (например, Z80) содержат встроенную схему регенерации памяти динамических ЗУ. В большинстве случаев современные ИС динамической памяти имеют встроенные средства регенерации, что уменьшает загрузку МП.