Студопедия КАТЕГОРИИ: АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция |

ТИПОВЫЕ КОМБИНАЦИОННЫЕ ЦИФРОВЫЕ УСТРОЙСТВАВсе известные и вновь создаваемые ЦЭУ любой сложности выполняют преобразование совокупности цифровых входных сигналов Л' в выходные сигналы Yи могут быть отнесены к одному из двух основных классов: комбинационные и последовательностные ЦЭУ. Комбинационными называют ЦЭУ, состояние п выходов которого в любой момент времени полностью определяется совокупностью логических сигналов, присутствующих на т его информационных входах Среди комбинационных ЦЭУ, получивших разнообразное применение в информационно-измерительной и вычислительной технике, известны такие устройства, как дешифраторы и шифраторы, мультиплексоры и демультиплексоры, арифметические и арифметико-логические устройства (АЛУ) и др. Выходное состояние последовательностного ЦЭУ (конечного автомата) в данный момент времени определяется не только логическими сигналами на его входах, но еще зависит и от порядка (последовательности) их поступления в предыдущие моменты времени. Иными словами, конечные автоматы должны обязательно содержать элементы памяти, отражающие всю предысторию поступления логических сигналов и выполненные, например, на триггерах, в то время как комбинационные ЦЭУ могут быть целиком построены только на логических элементах. Рассмотрим наиболее распространенные типы комбинационных ЦЭУ, которые выпускаются в интегральном исполнении и широко Используются в современной цифровой технике. Дешифратором (декодером) называют комбинационное ЦЭУ, пред- Означенное для распознавания различных кодовых комбинаций сигналов на его входах В простейшем случае каждой кодовой комбинации на в*одах соответствует активный уровень сигнала только на одном из входов дешифратора. Такой дешифратор может применяться, например для управления работой нескольких исполнительных механизмов. Тогда для включения одного из них на входы дешифратора достаточно подать присвоенный этому механизму цифровой код.  В более общем случае каждой определенной комбинации на т входах дешифратора соответствует «-элементный код на его выходах. Такие дешифраторы иногда называют преобразователями кодов. Они широко используются в вычислительной технике, а также в приборах с цифровой индикацией, например, для управления индикаторами на светоизлучающих диодах. Поскольку десятичные цифры (от 0 до 9) представляются 4-разрядным двоичным кодом, а стилизованные изображения всех десятичных цифр в известных типах светодиодных индикаторов чаще всего составляют из семи светящихся сегментов, такой дешифратор должен иметь 4 входа, 7 выходов и распознавать только первые десять из 16 возможных входных кодовых комбинаций. Условное обозначение микросхем дешифраторов на корпусе ИС после номера ее серии имеет первой букву И (для всех цифровых устройств), а второй — букву Д. На, рис.6.20,а представлена схема подключения ТТЛ-дешифратора К514ИД1 для управления семисегментным цифровым индикатором на светодиодах с объединенными катодными выводами. Дешифратор работает обычным образом при высоком уровне сигнала на входе Е Сигнал низкого уровня на этом входе независимо от информации на входах D0 — D3 переводит все выходы дешифратора в состояние логического нуля, в результате чего все светодиоды гаснут. Шифратором (кодером) называют комбинационное ЦЭУ, преобразующее активные уровни сигналов на его входах в соответствующий код на выходах Из этого определения следует, что шифратор выполняет преобразование, обратное тому, которое делается дешифратором. В простейшем случае шифратор сопоставляет активному уровню на одном из входов n-элементный двоичный выходной код, поэтому количество его выходов всегда меньше, чем входов. Так, шифраторcn-выходами может иметь максимальное количество входов, равное т=2п. Рис 6.20. Дешифраторы и шифраторы: а — схема подключения ТТЛ-дешиф- рагора К514ИД1;б — ТТЛШ-шифратор КМ555ИВ1 В самом общем случае допускается, что на несколько входов шифратора могут одновременно поступать активные уровни, поэтому схему шифратора дополняют так называемым арбитром приоритетов, назначение которого распределить уровни приоритетов по номерам входов. Шифраторы, допускающие такой режим, называют приорит е т н ы м и. Чаще всего в приоритетных шифраторах наивысшим уровнем приоритета обладает вход с наибольшим номером. В условном обозначении на корпусе шифратора после номера серии микросхемы записывают буквы ИВ. Например, КМ555ИВ1 (рис.6.20,б) представляет собой приоритетный шифратор с инверсными информационными входами D0 — D7 и тремя инверсными выходами Y0 - Y2. В этом шифраторе наивысшим уровнем приоритета обладает вход D7. Шифратор имеет инверсный вход E1 запрета его работы, при низком уровне сигнала на этом входе шифратор не реагирует на информационные сигналы (обычно вход E1 используют для отключения шифратора в те моменты времени, когда происходит смена входной информации). Два дополнительных инверсных выхода Е0 и GS предназначены для построения на основе ИС КМ555ИВ1 более сложных схем многоразрядных шифраторов. На выходе Е0 (разрешения от выхода) появится низкий уровень напряжения, если на всех входах присутствуют высокие уровни. На групповом выходе GS будет низкий уровень, если хотя бы на одном из этих входов имеется низкий уровень. Как правило, построение схемы шифратора сопряжено с наличием значительного количества факультативных условий, соответствующих запрещенным кодовым комбинациям на его входах. Проиллюстрируем это на примере следующей задачи. Задача 6.12.Построить схему шифратора с тремя прямыми входами (x3x2x1), в котором единичному уровню на одном из входов на выходах(Y0Y1) сопоставляется двоичный код номера этого входа. Решение. В условиях задачи определены всего три состояния на входах, когда на каждом из них в отдельности присутствует высокий уровень. Остальные комбинации исключены, что соответствует факу льтативным условиям, помеченным в таблице истинности шифратора (рис.6.21,а) буквами Ф. По этой таблице запишем выражение булевых функций на двух выходах шифратора

где

Рис 6 21 К построению схемы шифратора: а — таблица истинности шифратора; 6 кар гы минимизации выходных функций

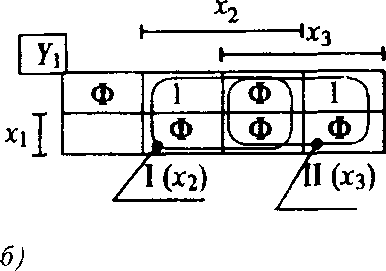

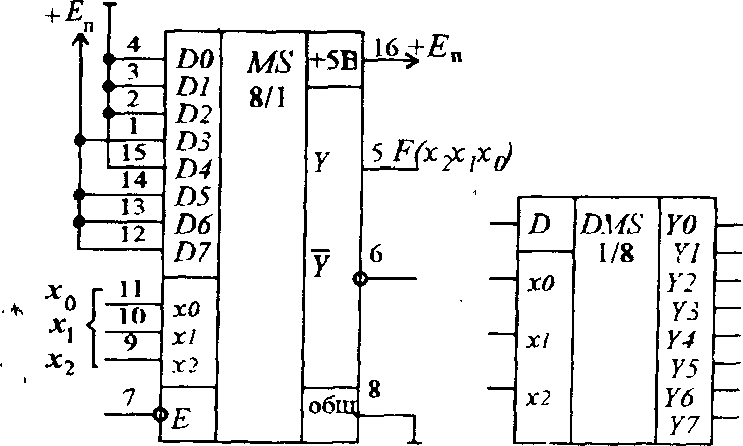

Нанесем все единичные и факультативные наборы на карты минимизации (рис.6.2 б), построенные для выходных функций Мультиплексором называют комбинационное ЦЭУ с одним выходом, несколькими информационными и управляющими входами, логическое состояние на выходе которого повторяет сигнал на одном из информационных входов в соответствии с заданным цифровым кодом на управляющих входах. Иными словами, мультиплексор коммутирует на свой выход сигнал входа, выбираемого при помощи цифрового кода на управляющих входах(режим выбора данных). Если цифровой код на управляющих входах поочередно принимает все возможные комбинации, состояние на выходе мультиплексора последовательно (с частотой смены управляющих кодов) повторяет состояние всех его информационных входов (режим мультиплексирования данных). Иногда говорят, что в этом режиме мультиплексор выполняет преобразование параллельного двоичного кода на информационных входах в последовательный код на его выходе. Условное обозначение микросхем мультиплексоров на корпусе после номера серии имеет буквы КП. Например, К555КП7 представляет собой ТТЛШ-мультиплексор, содержащий три управляющих и 8 информационных входов (мультиплексор 8/1), прямой и инверсный выходы, а также стробирующий вход Е, разрешающий работу мультиплексора при низком активном уровне сигнала на этом входе. Нетрудно записать выражение закона работы этого мультиплексора

Из рассмотрения этого выражения приходим к весьма важному выводу, что мультиплексор представляет собой универсальный прибор, с помощью которого можно довольно просто строить комбинационные ЦЭУ, реализующие произвольные булевы функции. Так, для реализации на основе мультиплексора 8/1 любой булевой функции трех переменных на информационные входы D0—D7 следует подать требуемые логические уровни, которые эта булева функция принимает соответственно на наборах с номерами 0—7, а его управляющие входы — использовать в,качестве информационных входов ЦЭУ. Включение мультиплексора 8/1 для реализации, например,булевой функции F(x2,x1 ,х0),таблица истинности которой ранее была приведена на рис.6.1, показано на рис.6.22,а.

Демультиплексором называют комбинационное ЦЭУ с несколькими выходами и управляющими входами, коммутирующие сигнал на единственном информационном входе на один из выходов в соответствии с цифровым кодом на управляющих входах. Таким образом, демультиплексор выполняет преобразование, обратное мультиплексированию. При циклическом переборе на управляющих входах всех возможных кодовых комбинаций демультиплексор выполняет преобразование последовательного двоичного кода на его информационном входе в параллельный код, который возникает на выходах по окончании полного цикла этого перебора. Изображение демультиплексора 1/8 стремя управляющими входамиF(x2,x1 ,х0),, информационным входом D и 8 выходами приведено на рис. 6.22,6. В качестве демультиплексоров чаще всего используются дешифраторы, имеющие вход разрешения Е. Для того чтобы такой дешифратор работал в режиме демультиплексора, управляющие сигналы демультиплексора подают на информационные входы дешифратора, а информационный сигнал — на вход разрешения Е. Вопрос 6.3. На входе Е1 шифратора КМ555ИВ1 установлен единичный уровень сигнала. Возможно ли появление активного уровня сигнала только на одном из его выходов Y0— Y2, если активный уровень сигнала подать только на один из информационных входов D0—D7? Варианты ответа: 6.3.1. Невозможно. 6.3.2. Возможно, но только в единственном варианте. 6.3.3. Возможно в двух вариантах. 6.3.4. Возможно в трех вариантах. 6.7. АРИФМЕТИЧЕСКИЕ И АРИФМЕТИКО-ЛОГИЧЕСКИЕ УСТРОЙСТВА К арифметическим относят комбинационные ЦЭУ, служащие для выполнения арифметических операций сложения,вычитания и умножения многоразрядных двоичных чисел. Сумматором называют комбинационное ЦЭУ, выполняющее арифметическую операцию сложения двух многоразрядных двоичных чисел, кодовые комбинации которых присутствуют на его информационных входах. Результат сложения отображается параллельным двоичным ко- дом на выходах сумматора. Поскольку сложение двух многоразрядных чисел всегда начинается с суммирования их младших разрядов, рассмот- рим простейшее ЦЭУ, выполняющее сложение двух одноразрядных чисел и называемое полусумматором. Ранее уже отмечалось, чторезультат такой операции за исключением возможного переноса в соседний более старший разряд описывается булевой функцией сложения по модулю 2. Поэтому полусумматор имеет два информационных входа (XjXq), куда поступает содержимое суммируемых разрядов, а также два выхода. Первый из них 5(XjX0) представляет младший разряд результата и описывается суммой по модулю 2, а второй — Р(ххх0) обеспечивает сигнал переноса. Таблица истинности полусумматора приведена на рис. 6.23,а. Для построения полусумматора используем элемент М2, на выходе которого получаем S(x}x0) =М2(х1х0), а также элемент И, на выходе которого будет сигнал переноса />(jc1jc0)=jc1jc0 (рис.6.23,б). Изображение полусумматора ка структурных схемах дано на рис. 6.23,в. Для получения результата сложения двух многоразрядных чисел в следующем (за младшим) разряде приходится суммировать уже три одноразрядных двоичных числа, так как помимо складываемых разрядов необходимо учитывать возможный перенос из младшего разряда. Простейшее ЦЭУ, позволяющее сложить три одноразрядных двоичных числа, называют полным сумматором. Изображение полного сумматора на структурных схемах приведено на рис. 6.24,а Подобно полусумматору он имеет два выхода S и Р, но в отличие от него — три входа, один из которых, например, х2 служит для учета сигнала переноса из младшего разряда. На рис. 6.24.б представлена таблица истинности полного сумматора, из рассмотрения столбца для которой получаем выражение

Сопоставляя это выражение с функцией М2, приходим к выводу, что Рис.6.23. Полусумматор; а — таблица истинности, б — схема; в —условное обозначение полусумматора

б) Рис.6.24. Полный сумматор: а — условное обозначение полного сумматора; б — таблица истинности; в — реализация на двух полусумматорах Далее по таблице (см.рис.6.24,б) для выхода

упрощая которое, а также учитывая, что

Заметим, что второе слагаемое в этом выражении представляет собой сигнал с выхода переноса полусумматора. В целом

а)

На основе полусумматора и нескольких полных сумматоров одноразрядных двоичных чисел строят схемы полных сумматоров двух многоразрядных чисел. Соединяя выходы переноса полусумматора и последующих полных сумматоров друг за другом, получаем схему многоразрядного полного сумматора с последовательным переносом. В этом сумматоре младшие разряды двух суммируемых двоичных чисел подаются на входы полусумматора, а остальные разряды — на входы соответственных полных сумматоров одноразрядных чисел. Результат сложения в параллельном двоичном коде снимается поразрядно со всех выходов S , а сигнал переноса в следующий более старший разряд — с выхода Р последнего полного сумматора. В качестве примера на рис. 6.25 представлены структурная схема и изображение полного сумматора с последовательным переносом для выполнения сложения двух четырехразрядных чисел

Вычитание двоичных чисел обычно заменяют операцией сложения уменьшаемого с вычитаемым, записанном в одном из специальных кодов.[4] Микросхемы полусумматоров после номера серии в своем условном обозначении имеют буквы ИЛ, а полных сумматоров—буквы ИМ. При этом выпускаются интегральные схемы как полных сумматоров одноразрядных чисел (например К555ИМ5, содержащая в одном корпусе два полных ТТЛШ —сумматора одноразрядных двоичных чисел), так и многоразрядные полные сумматоры (например, КМ555ИМ6 — четырехразрядный сумматор с ускоренным переносом),. Умножителем называют арифметическое устройство для вычисления произведения многоразрядных двоичных чисел. Операция умножения двух многоразрядных двоичных чисел чаще всего выполняется путем многократного сложения с весом поразрядно сдвинутых влево копий одного из сомножителей. В качестве указанных весовых коэффициентов, с которыми складываются соответствующие сдвинутые копии, используются биты (0 или 1) другого сомножителя. Таким образом, умножители могут быть построены на нескольких многоразрядных полных сумматорах, поэтому они также относятся к классу комбинационных ЦЭУ. Заметим, что при параллельном коде результата количество выходов умножителя должно быть не меньше суммы разрядов сомножителей. Изображая умножители на структурных схемах, их помечают буквами МР. Микро-схемы умножителей после номера серии обозначают буквами ИП (прочие цифровые устройства). Большую группу комбинационных ЦЭУ составляют арифметико-логические устройства (АЛУ), выполняющие ряд обычных и специальных арифметических и логических операций: прибавление и вычитание единицы, сравнение двоичных чисел и формирование по его результатам некоторых логических функций, выявление знака разности двоичных чисел, контроль соответствия суммы единиц двоичного кода четному (или нечетному) числу, преобразование кодов и т.д. Благодаря использованию последних достижений в микроэлектронике, АЛУ представляют собой весьма сложные комбинационные ЦЭУ, обладающие разнообразными и богатейшими функциональными возможностями. Они составляют основуаппаратных средств, с помощью которых выполняется большинство «машинных» команд в современной микропроцессорной вычислительной технике. На структурных схемах АЛУ обозначаются буквами ALU, а их микросхемы (подобно умножителям) обозначают буквами ИП. Например, К555ИПЗ представляет собой микросхему АЛУ, выполняющую 16 арифметических и 16 логических операций, выбор которых осуществляется различными комбинациями логических уровней на четырех управляющих входах ЕДО — ЕДЗ, а также на входе выбора режима работы М. При низком уровне сигнала на входе М микросхема выполняет арифметические, а при высоком — логические операции. 6.8. ПОСЛЕДОВАТЕЛЬНОСТНЫЕ ЦИФРОВЫЕ УСТРОЙСТВА Принципиальное отличие последовательностных ЦЭУ от комбинационных заключается в том, что при пассивных уровнях сигналов на входах комбинационные ЦЭУ всегда возвращаются в исходное состояние, в то время , как последовательностные находятся в режиме хранения предыдущего состояния. По этой причине в состав типовых последовательностных ЦЭУ, к которым относятся счетчики, регистры и запоминающие устройства, помимо обычных логических элементов, обязательно входят элементы памяти, выполненные, например, на триггерах. С нетчиками называют последовательностные ЦЭУ, обеспечивающие хранение двоичного кода числа и выполнение над ним микрооперации счета, которая заключается в изменении значения числа в счетчике на ± 1. Если при подаче активного уровня сигнала на информационный вход счетчика его содержимое увеличивается на единицу, счетчик называют суммирующим, а если уменьшается на единицу — вычитающим. Счетчик называют реверсивным, если он выполняет обе предыдущие операции. Счетчик называют синхронным, если состояния всех его выходов устанавливаются в определенные моменты времени, определяемые импульсами синхронизации. У асинхронных счетчиков состояния могут устанавливаться с некоторой задержкой относительно друг друга. Основной параметр счетчика — модуль счета Кс, определяющий Максимальное число сигналов, которое может быть сосчитано счетчиком. Как правило, в схемах счетчиков используют триггеры, поэтому счет количества поступивших сигналов в них ведется в двоичной системе счисления. Двоичный счетчик с n-разрядами способен подсчитать 2псигналов, отображая их количество двоичными числами в диапазоне от 0 до (2n-1). После сигнала с номером 2п такой счетчик возвращается в исходное состояние. Рис 6 26 Трехразрядный суммирующий двоичный счетчик а — таблица состоянии. б — временные диаграммы, поясняющие его работу, в — схема сумми- рующего счетчика, г — условное обозначение реверсивного счетчика на структурных схемах, д — работа реверсивного счетчика от одного источника счетных импульсов

Рассмотрим таблицу состояний (рис.6.26,а) трехразрядного суммирующего двоичного счетчика ( На рис.6 26,б приведены временные диаграммы, поясняющие работу асинхронного трехразрядного двоичного суммирующего счетчика, а на рис 6 26,в—его схема на асинхронных двухступенчатых JK-триггерах, включенных по схеме асинхронного T-триггера Для правильной работы этой схемы весьма существенно то, что переключение двухступенчатого JK -триггера происходит по окончании активного единичного уровня сигнала на его входе синхронизации С. Заметим, что частота следования импульсов на выходе триггера D0 — в 2 раза, на выходе D1 — в 4 раза, а на выходе D2 — в 8 раз ниже частоты следования импульсов на входе счетчика По этой причине суммирующие счетчики часто также применяются в качестве делителей частоты.Вход R, объединяющий входы асинхронного сброса всех триггеров, служит для предварительной установки разрядов счетчика в исходное нулевое состояние. Для увеличения количества разрядов счетчиков применяют их каскадное соединение друг за другом, для чего в схеме счетчика предусматривают специальный выход Р, с которого снимают сигнал переноса на информационный вход С1 следующего счетчика В схеме счетчика (см рис.626,в) для этой цели введен дополнительный логический элемент 4И, на один из входов которого поступают счетные импульсы, а три остальных подключены к выходам триггеров D0, D1 и D2 Поскольку после седьмого импульса все триггеры счетчика установлены, в момент прихода восьмого импульса на выходе Р(>7) этого элемента появится единичный уровень, который и используют в качестве сигнала переноса на вход С1 следующего счетчика

В худшем случае (после седьмого импульса) для установки оконча[5] тельного состояния всех разрядов счетчика (смрис.6.26.в) потребуется последовательное переключение всех его триггеров. Поскольку переключение каждого триггера всегда происходит с некоторой задержкой, этот процесс соответствует распространению сигнала переноса по линейке триггеров (подобно распространению сигнала переноса в схемах сумматоров). По этой причине счетчики, построенные по такому принципу, часто называют счетчиком с последовательным (сквозным) переносом. При большом числе разрядов счетчика указанная задержка может оказаться значительной, что и ограничивает его быстродействие. * В вычитающих счетчиках с приходом очередного импульса содержимое счетчика уменьшается на единицу. Обычно в исходном состоянии все триггеры устанавливают в единицу, что обеспечивается объединением их входов S асинхронной установки. Поскольку при этом на всех инверсных выходах триггеров будет состояние логического Реверсивные счетчики объединяют в себе описанные выше схемные решения для суммирующего и вычитающего счетчиков. Счетные импульсы для суммирования в них подаются на вход (+1), а для вычитания — на вход (-1). Эти же сигналы управляют и вспомогательными логическими элементами, обеспечивающими необходимую коммутацию цепей для работы счетчика в соответствующих режимах. Изображение трехразрядного реверсивного счетчика на структурных схемах приведено на рис 6.26,г. В этом счетчике на выходах PU (>7) и PD (<0) формируются сигналы переноса на соответствующие входы (±1) следующего такого же счетчика. Входы R и S служат для начальной установки всех триггеров счетчика соответственно в 0 или 1. В цифровых измерительных приборах часто возникает необходимость работы реверсивного счетчика от одного источника счетных импульсов, причем одна часть импульсов должна суммироваться, а другая — вычитаться В этом случае реверсивный счетчик подключают через дополнительное ЦЭУ (смрис.6.26,д) в виде RS-триггера и двух элементов 2Л переключающее режимы работы счетчика. При высоком уровне сигнала на входе разрешения суммирования (+E)RS -триггер устанавливается, и сигналы счета С0 поступают на вход (+1). С другой стороны, при высоком уровне сигнала на входе разрешения вычитания (-Е) RS -триггер сбрасывается, и реверсивный счетчик работает в режиме вычитания счетных импульсов С0. Помимо двоичных счетчиков, модуль счета которых равен степени двойки, на практике часто возникает потребность в счетчиках с произвольным модулем счета Кс. Для построения таких счетчиков обычно используют двоичный счетчик, модуль счета которого превышает требуемое значение Кс, и при помощи дополнительных устройств или цепей обратной связи исключают в нем лишние состояния, уменьшая их число до значения Кс. На рис.6.27,а приведена схема асинхронного суммирующего счетчика с модулем счета Кс= 5, которая отличается от схемы трехразрядного двоичного счетчика тем, что в нее введена цепь обратной связи через логический элемент DD1, обеспечивающая перевод триггера D0 в нулевое состояние после четвертого импульса, а также добавлен элемент DD2, сбрасывающий триггер D2 после пятого импульса. Сигнал с выхода этого элемента можно использовать в качестве сигнала переноса Р при каскадном соединении таких счетчиков. Логический элемент DD3 играет вспомогательную роль, обеспечивая по шине R асинхронную установку счетчика в нулевое исходное состояние. Двоично-десятичным (или просто десятичным) называют счетчик с модулем счета Кс=10. Состояния такого счетчика трактуются в виде двоично-десятичного кода первых десяти цифр (от 0 до 9). Многоразрядные десятичные числа в этом коде могут быть получены на выходах нескольких таких счетчиков, включенных каскадно. Схему двоично-десятичного счетчика можно построить, включив, например, перед счетчиком с модулем Кс=5 счетчик делитель частоты на 2 (Кс =2).В качестве такого делителя частоты на 2 можно использовать, например, триггер D0 из схемы (см.рис.6.26,в). Поскольку при каскадном соединении счетчиков их модули счета умножаются, получим счетчик с Кс = 10. Условное изображение асинхронного десятичного счетчика на структурных схемах приведено на рис.6.27,б Десятичные счетчики получили широкое распространение в измерительной технике и, в частности, в приборах с цифровой индикацией. Например, соединяя выходы двоично-десятичного счетчика с входами дешифратора К514ИД1, к выходам которого по схеме рис.6.20,а подключен светодиодный семисегментный индикатор, на табло этого индикатора можно Получать изображения десятичных цифр, соответствующих количеству Импульсов, подсчитанных счетчиком.

Рис.6.27 Асинхронные счетчики: a — структурная схема счетчика с модулем счета Кс =5; 6 — условное обозначение двоично-десятичного счетчика Микросхемы счетчиков после номера серии обозначают буквами ИЕ. В настоящее время выпускается довольно обширная их номенклатура от простейших, позволяющих вести счет только в одном направлении, до многоразрядных двоичных и десятичных, асинхронных и синхронных счетчиков. Помимо рассмотренных ранее режимов работы, современные микросхемы счетчиков обеспечивают предварительную запись в параллельном двоичном коде исходного состояниям которого зат ем начинается счет в ту или иную сторону (например ТТЛШ-счетчик К555ИЕ18), а также позволяют программным способом, задавая определенные логические уровни на управляющих входах, в широких пределах изменять модуль счета (коэффициент деления частоты следования входных импульсов, как например, в TTЛ-микросхеме К155ИЕ8). Существуют также микросхемы, объединяющие в себе десятичный счетчикс дешифратором для управления семисегментным цифровым индикатором, например, ИС К176ИЕЗ и К176ИЕ4. Регистрами называют последовательностные ЦЭУ, служащие для записи и хранения многоразрядных чисел, выполнения над ними поразрядных логических операций и вывода хранимой информации. Проще всего при помощи регистров выполняются такие поразрядные логические операции, как инверсия бит, сдвиги кода числа влево и вправо на заданное количество разрядов и некоторые другие. Поскольку триггер обеспечивает хранение одного бита информации, схемы регистров строят на основе цепочки триггеров, количество которых определяется числом разрядов двоичного числа. Ввод и вывод информации в регистрах может выполняться как в параллельном, так и в последовательном двоичном коде. Регистры с параллельным приемом и выдачей информации называют регистрами памяти, а с последовательным вводом и выводом —сдвигающими (сдвиговыми) регистрами. Регистр называют реверси в- н ы м, если поразрядный сдвиг двоичного кода в нем может выполняться в обе стороны. Однотипные регистры также могут различаться и некоторыми дополнительными возможностями, например, наличием как прямых, так и инверсных выходов, выводов наращивания разрядности, режима асинхронного или синхронного сброса хранимой информации и т.п. В регистрах памяти для хранения двоичной информации используют D-триггеры. На рис.6.28,а приведена схема трехразрядного регистра памяти, на примере этой схемы рассмотрим принцип реализации некоторых наиболее важных функций регистров памяти. Регистр выполнен на трех синхронных D-триггерах, асинхронные входы сброса которых подключены к шине очистки R. Активным единичным уровнем сигнала на этой шине производят очистку регистра (режим очистки). Далее по сигналу разрешения записи L информация на входных шинах данных в параллельном двоичном коде через переключающие ячейки (на элементах2 х 2И — ИЛИ) поступает на D-входы триггеров D0, D1 и D2. По окончании импульса синхронизации на входе С (т.е. к следующему такту) она появляется на выходах соответствующих триггеров (режим записи). После этого соответственная комбинация входных данных может быть снята, так как регистр выполняет их временное хранение. Отметим, что для записи входной информации в регистр не требуется его предварительной очистки, так как предыдущая информация, хранимая в нем, исчезает и заменяется новым содержанием. Для выполнения, например, такой поразрядной логической операции, как инверсия бит, необходимо подать активный единичный уровень сигнала на шину В инверсий бит. При этом коммутирующие ячейки на элементах 2 х 2И—ИЛИ подключают к D-входу каждого триггера его инверсный выход, обеспечивая его режим работы в качестве счетного триггераТогда при единичном уровне сигнала на входе синхронизации С состояние каждого из них (в режиме счетного триггера) меняется на инверсное Наконец, для чтения (вывода) информации из регистра памяти активны^ уровень сигнала подают на вход Е разрешения чтения, и содержимое регистра через блокирующие ячейки (на элементах 2И) также в параллельном коде выставляется на выходных шинах Отметим, что режим чтения не разрушает информации в регистре, она хранится в нем до очередного цикла записи новых данных.

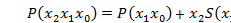

С режимами записи данных в регистры и чтения информации, хранимой в них, в той или иной мере связана большая группа «машинных» команд современных цифровых вычислительных машин, составляющая так называемые команды пересылки*[6]Как показывает опыт, из всех типов команд, выполняемых вычислительными машинами, примерно (60 — 80)% составляют команды пересылки данных, поэтому для регистров это наиболее часто используемый режим работы. Все триггерные ячейки регистра памяти, по существу, работают параллельно, в то время как в сдвигающих регистрах их, подобно схемам счетчиков, включают каскадно друг за другом. На рис.6.28,б приведена схема трехразрядного сдвигающего регистра, построенная наD-триггерах. Рассмотрим работу сдвигающего регистра на примере записи трехразрядного двоичного числа После записи числа в сдвигающий регистр (см.рис.6.28,б) сдвиг его еще на один разряд приводит к тому, что крайний справа бит выходит за пределы разрядности регистра. Соединяя выход Для изменения направления сдвига информации в регистре (см.рис.6.28,б) необходимо после записи в него числа соответствующим образом перекоммутировать D-входы триггеров так, чтобы на D-вход триггера D0 подавался сигнал с выхода Соединяя триггерные ячейки с коммугирующими, получим схему реверсивного регистра. Направлением сдвига информации в нем можно управлять, подавая активные уровни сигнала на вход разрешения сдвига влево VLили вход разрешения сдвига вправо VR,объединяющие соответствующие входы управления коммутирующих ячеек. Микросхемы регистров обозначают после номера серии двумя буквами ИР. Последние разработки ИС регистров, как правило, характеризуются совмещением функций рассмотренных типов регистров и представляют собой, так называемые универсальные (многорежимные) регистры, обеспечивающие, например, последовательный ввод, сдвиг в обе стороны, кольцевой сдвиг и параллельный вывод. Для уменьшения общего числа выводов в таких многорежимных регистрах входные и выходные шины часто объединяют. Регистры с такого рода объединением шин называют портами дан ных,в них одни и те же линии по специальным командам используются как для приема, так и для выдачи данных. Для реализации такой возможности в настоящее время широко используются элементы с третьим состоянием в виде микро-схем двунаправленных шинных усилителей (ДНШУ), представляющих собой два, включенных параллельно навстречу друг другу, управляемых повторителя (см.рис.6.28,в). При низком уровне сигнала на входе управления E0нижний повторитель DD2 переведен в третье состояние, а верхнему DD1 разрешена работа, что соответствует передаче данных в направлении с входа на выход. При высоком уровне этого сигнала работает повторитель DD2 и данные передаются в обратном направлении. Микросхемы ДНШУ обозначают буквами АП, например, К531АП4 имеет в своем составе восемь буферных повторителей, четыре из которых управляются высоким, а другие четыре—низким уровнем сигнала на их входах разрешения работы Е0. На рис.6.28,г представлена микросхема К564ИР6, представляющая собой восьмиразрядный универсальный двунаправленный КМОП-регистр из восьми триггерных ячеек и комбинационного управляющего устройства. Регистр обеспечивает режимы параллельного и последовательного ввода информации, ее сдвиг и хранение и может быть использован для преобразования как параллельных кодов в последовательную форму, так и последовательных кодов — в параллельный. Последовательный ввод информации в регистр осуществляется по входу Столько в синхронном режимепо положительному перепаду сигнала на входе синхронизации С при низком уровне сигнала на входе P/S управления режимами ввода. Работа триггерных ячеек в этом режиме организована таким образом, что при подаче очередного импульса синхронизации происходит сдвиг информации, хранимой в регистре, на один разряд вправо. Для сдвига информации влево необходимо выводы Параллельный ввод выполняется при высоком уровне сигнала на входе Р/S и в зависимости от уровня сигнала на входе управления А/S может осуществляться в асинхронном (при высоком уровне сигнала на этом входе) или синхронном режиме (при низком уровне на входе А/S ). Регистр может выполнять двунаправленную передачу данных от шин А к шинам В и наоборот, причем направление этой передачи определяется уровнем сигнала на входе А/В Так в режиме параллельного ввода при высоком уровне сигнала на входе А/В шины А служат входами, В — выходами, а при низком — шины В — входами, А — выходами. Сигналом на входе разрешения АЕ можно управлять соединением выводов А с линейкой триггеров регистра. При низком уровне сигнала на входе АЕ эта связь разрывается, что позволяет выводы А нескольких микросхем регистров объединять параллельно и поступающую информацию по этим общим шинам адресно распределять по нескольким аналогичным регистрам. Исключительно важная роль регистров объясняется тем, что практически любое ЦЭУ может быть выполнено на основе совокупности регистров, соединенных друг с другом с помощью соответствующих комбинационных схем управления. Вовсе не случайно, а именно по этой причине, все многообразие аппаратных средств, реализованных в составе больших интегральных схем (БИС микропроцессоров), используемых, например, для построения современных персональных ЭВМ, с точки зрения программистов в простейшем случае представляется в виде набора, так называемых, регистров общего назначения (сокращенно РОН). По сути дела РОН представляют собой многоразрядные универсальные регистры с весьма малым временем обращения. 6.9. УСТРОЙСТВА ДЛЯ ПРЕОБРАЗОВАНИЯ ФОРМЫ ПРЕДСТАВЛЕНИЯ ИНФОРМАЦИИ Поскольку информация на входах ЦЭУ обычно представляется в двоичном коде, а большинство исполнительных механизмов для автоматизированного управления технологическими процессами (исполнительные двигатели, электромагниты и т.п.), как правило, реагируют на непрерывно изменяющиеся уровни напряжения или тока, для преобразования информации из цифровой в аналоговую форму используют цифроаналоговые преобразователи (ЦАП). Помимо широкого промышленного применения ЦАП используются и в современной бытовой электронике, например, в системах высококачественного воспроизведения звука, записанного в цифровой форме на компакт-дисках (в лазерных СД-проигрывателях). В системах автоматизированного управления для получения информации о состоянии контролируемого промышленного оборудования применяют различного рода преобразователи (датчики) неэлектрических величин в электрические сигналы, которые чаще всего представляются в аналоговом виде. Для последующей обработки этой информации при помощи ЦЭУ такие сигналы предварительно должны быть преобразованы в цифровую форму. В самом общем случае преобразование аналог- цифра вы пол няют в два этапа. Вначале непрерывно изменяющийся сигнал заменяют его значениями в дискретные моменты времени, что называют дискретизацией во времени. Затем эти значения сигнала подают на вход аналого — цифровых преобразователей (АЦП), которые с некоторым шагом ΔU квантования по уровню представляют их цифровым эквивалентом в виде двоичного кода. Дискретизация во времени считается выполненной корректно, если возможно однозначное восстановление исходного аналогового сигнала. При этом исходный сигнал должен удовлетворять следующим двум условиям*[7]: частотный (спектральный) состав исходного сигнала должен быть ограничен некоторой верхней граничной частотойfв; частота дискретизации (следования отсчетов)/д должна быть больше или равна 2fв. Если широкополосный сигнал не удовлетворяет первому из этих условий, его пропускают через фильтр нижних частот с частотой среза fв. Дискретизацию во времени быстроизменяюшегося сигнала чаще всего выполняют, фиксируя его мгновенные значения в моменты времени, определяемые частотой fд следования импульсов выборки, в виде напряжения на запоминающем конденсаторе. Обычно выбирают частоту дискретизации Основными характеристиками ЦАП и АЦП являются быстродействие и погрешность преобразования, определяемая абсолютной погрешностью преобразования и относительной разрешающей способностью. Быстродействие ЦАП и АЦП характеризуется временем преобразования: для ЦАП это отрезок времени после поступления входного двоичного кода до установления его выходного аналогового сигнала; для АЦП — интервал времени от его пуска до момента получения выходного двоичного кода. Абсолютная погрешность преобразования равна половине шага квантования по уровню Цифроаналоговые преобразователи. ЦАП представляют собой устройства для создания аналогового выходного значения напряжения (или тока), соответствующего числовому эквиваленту двоичного цифрового кода на его входе. Зависимость выходного параметра ЦАП. например, напряжения на его выходе, от кодового эквивалента входного сигнала называют характеристикой преобразования. На рис.6.29,а представлена характеристика преобразования четырехразрядного ЦАП. Используя для значений двоичных чисел (р=2) формулу (6.1), получим общее выражение для характеристики преобразования n-разрядногоЦАП

откуда, в частности, для выходного напряжения четырехразрядного ЦАП запишем

Поскольку выходное напряжение ЦАП представляется в виде суммы отдельных слагаемых, которые в зависимости отзначений коэффициентов а0— «з могут входить (при единичном значении) или не входить (при нулевом значении соответствующего коэффициента) в окончательный результат, ЦАП может быть построен на основе аналогового сумматора и транзисторных ключей, обеспечивающих необходимую коммутацию напряжений (или токов). На рис.6.29,б представлена схема четырехразрядного ЦАП с характеристикой преобразования (6.8), построенная на основе сумматора на интегральном операционном усилителе (ОУ) и резистивной матрицы (набор резисторов)

В этой схеме транзисторные ключи

где ( Сопоставив (6.8) и (6.9), приходим к выводу, что при Недостатком схемы ЦАП (см. рис.6.29,б) является значительный разброс номиналов и весьма жесткие требования по точности подгонки значений сопротивлений резистивной матрицы. На рис.6.29,в представлена схема четырехразрядного ЦАП на основе так называемой (R — 2R) - резистивной матрицы, свободная от указанных недостатков. Резистивная (R — 2R)-матрица представляет собой цепь лестничной структуры, обладающая такими замечательными свойствами, что ее входное сопротивление не зависит от числа (R — 2R)-ячеек и всегда равно R, а токи резисторов 2R в соседних ячейках различаются в 2 раза. В схеме ЦАП на рис.6.29,в транзисторные ключи

где, как и ранее, а§ — в зависимости от состояния ключей (50 — S3) принимают значения I или 0. Для (R — 2R)-матрицы четырех ячеек (как на рис.6.29,в) имеем Схема ЦАП (см.рис.6.29,в) содержит две группы резисторов с номиналами R и 2R, что позволяет создавать интегральные схемы высокоточных ЦАП, так как в едином технологическом цикле нетрудно обеспечить одинаковые номиналы резисторов в пределах каждой из двух упомянутых групп. Более того, конкретное значение этого номинала не играет существенной роли,важно, чтобы сопротивления резисторов этих двух групп отличались в 2 раза. Микросхемы ЦАП после номера серии в обозначении первой имеют букву П (для всех преобразователей), а второй—букву А. На рис.6.29,г представлена ИС типа К572ПА1, представляющая собой выполненный на основе КМОП-технологии 10-разрядный ЦАП с временем преобразования не более 5 мкс. К сожалению, при разработке этой ИС технологически не удалось на одной подложке вместе с КМОП-ключами и (R—2R)-матрицей выполнить и схему ОУ, поэтому ЦАП К572ПА1 всегда дополняют внешней микросхемой ОУ, подключение которой также показано на рис.6.29 ,г. В заключение отметим, что ЦАП К572П А1 обеспечивает уникальную возможность выполнить операцию умножения аналоговой величины Uon на другую величину, задаваемую двоичным цифровым кодом на входах D0—D9, при этом результат умножения представляется также в аналоговом виде выходным напряжением ЦАП. По этой причине ЦАП К572ПА1 иногда называют умножающим. Аналогово-цифровые преобразователи. АЦП представляют собой устройство для сопоставления цифрового двоичного кода уровню аналогового сигнала на его входе. Характеристикой преобразования АЦП называют зависимость числового эквивалента двоичного кода на выходе АЦП от нормированного к напряжению шкалы входного аналогового сигнала В настоящее время наибольшее распространение получила классификация интегральных АЦП на основе рассмотрения характера развития в них процесса преобразования во времени. Согласно такому подходу все интегральные АЦП можно разбить надватипа: последовательного действия (развертывающего типа) и параллельного действия (параллельного типа)*[9] К АЦП развертывающего типа относят АЦП с последовательным счетом, с поразрядным уравновешиванием (последовательных приближений) и интегрирующие АЦП. Структурная схема АЦП последовательного счета представлена на рис.6.30,а. Постоянное (в течение времени действия импульса считывания, длительность которого выбирается чуть меньше периода дискретизации Общий недостаток АЦП с последовательным счетом — сравнительно невысокое быстродействие, из-за чего они чаще всего применяются в низкочастотных цифровых вольтметрах. Задача. 6.13. Определить верхнюю граничную частоту/в аналоговых сигналов, преобразуемых 10-разрядным АЦП последовательного счета, тактовая частота которого Решение Максимальное число N импульсов, подсчитанное двоичным счетчиком с n=10, составляет N=2n—1=1023. Тогда максимальная частота дискретизации преобразуемого сигнала будет |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2018-05-10; просмотров: 529. stydopedya.ru не претендует на авторское право материалов, которые вылажены, но предоставляет бесплатный доступ к ним. В случае нарушения авторского права или персональных данных напишите сюда... |

,

, — обозначены единичные слагаемые, соответствующие факультативным наборам.

— обозначены единичные слагаемые, соответствующие факультативным наборам.

,

,  в — схема шифратора

в — схема шифратора Содержимое в клетках с факультативными наборами доопределим таким образом, чтобы на картах минимизации получить максимальные размеры замкнутых областей при наименьшем количестве этих областей. Окончательно получаем минимизированные выражения, описывающие работу шифратора

Содержимое в клетках с факультативными наборами доопределим таким образом, чтобы на картах минимизации получить максимальные размеры замкнутых областей при наименьшем количестве этих областей. Окончательно получаем минимизированные выражения, описывающие работу шифратора  ,

,  Схема шифратора на элементах ИЛИ приведена на рис. 6.21,в.

Схема шифратора на элементах ИЛИ приведена на рис. 6.21,в. +

+

получится на выходе S полусумматора, если на один из его входов подать

получится на выходе S полусумматора, если на один из его входов подать  , а на второй – х2

, а на второй – х2

запишем выражение

запишем выражение ,

, окончательно получаем

окончательно получаем .

. . Сигналы

. Сигналы  и

и  . Реализация полного сумматора на двух полусумматорах и одном элементе ИЛИ показана на рис. 6.24.в

. Реализация полного сумматора на двух полусумматорах и одном элементе ИЛИ показана на рис. 6.24.в

), выполняющего микрооперацию суммирования (по обычным правилам) его предьщущего состояния с единицей Полагаем, что в исходном состоянии на всех выходах счетчика присутствуют нули. Как следует из этой таблицы, сигнал

), выполняющего микрооперацию суммирования (по обычным правилам) его предьщущего состояния с единицей Полагаем, что в исходном состоянии на всех выходах счетчика присутствуют нули. Как следует из этой таблицы, сигнал  на выходе младшего разряда счетчика изменяет свое состояние на инверсное всякий раз после поступления очередного подсчитываемого импульса на его вход Это означает, что такой сигнал может бьггь получен на выходе счетного триггера D0, на вход которого подаются счетные импульсы После прохождения первого счетного импульса на выходе Q0 этого триггера будет активное (единичное) состояние. Если к выходу D0подключить второй такой же счетный триггер D1,который также изменял бы свое состояние после прохождения активного уровня сигнала на его входе, с выхода триггера D1будет получен сигнал

на выходе младшего разряда счетчика изменяет свое состояние на инверсное всякий раз после поступления очередного подсчитываемого импульса на его вход Это означает, что такой сигнал может бьггь получен на выходе счетного триггера D0, на вход которого подаются счетные импульсы После прохождения первого счетного импульса на выходе Q0 этого триггера будет активное (единичное) состояние. Если к выходу D0подключить второй такой же счетный триггер D1,который также изменял бы свое состояние после прохождения активного уровня сигнала на его входе, с выхода триггера D1будет получен сигнал  , требуемые сигналы для переключения линейки триггеров вычитающего счетчика получаются, если счетный вход каждого следующего триггера подключить к инверсному выходу

, требуемые сигналы для переключения линейки триггеров вычитающего счетчика получаются, если счетный вход каждого следующего триггера подключить к инверсному выходу  предыдущего. Нетрудно убедиться в том, что состояния прямых выходов

предыдущего. Нетрудно убедиться в том, что состояния прямых выходов  всех счетных триггеров соответствуют последовательности двоичных состояний вычитающего счетчика.

всех счетных триггеров соответствуют последовательности двоичных состояний вычитающего счетчика. поступающего на его вход Dв последовательном коде младшими разрядами вперед. При первом импульсе на продвигающей шине С, объединяющей входы синхронизации всех триггеров, содержимое бита

поступающего на его вход Dв последовательном коде младшими разрядами вперед. При первом импульсе на продвигающей шине С, объединяющей входы синхронизации всех триггеров, содержимое бита  переписывается в триггер D0и появляется на его выходе

переписывается в триггер D0и появляется на его выходе  после этого импульса. При втором импульсе информация с выхода

после этого импульса. При втором импульсе информация с выхода  — в триггер D0. По окончании второго такта на выходе D0будет состояние

— в триггер D0. По окончании второго такта на выходе D0будет состояние  ,

,  ),причем на выходе Q2будет присутствовать младший разряд записанного числа. Очевидно во втором случае регистр одновременно будет выполнять преобразование последовательного кода в параллельный.

),причем на выходе Q2будет присутствовать младший разряд записанного числа. Очевидно во втором случае регистр одновременно будет выполнять преобразование последовательного кода в параллельный. .

. 8) соединить с выводами

8) соединить с выводами  , а на вход Р/S подать высокий уровень сигнала. При этом информационным будет вход .A8, а выходами В1-В8

, а на вход Р/S подать высокий уровень сигнала. При этом информационным будет вход .A8, а выходами В1-В8 . Неизменное (на отрезке времени между двумя импульсами выворки) напряжение затем подается на вход АЦП, который должен «успеть» закончить его преобразование в цифровую форму до поступления следующего импульса выборки. Заметим, что при достаточно быстродействующем АЦП и высокой частоте дискретизации, когда исходный аналоговый сигнал можетбыть непосредственно подан на вход АЦП, который в этом случае корректно выполняет как дискретизацию во времени, так и квантование по уровню.

. Неизменное (на отрезке времени между двумя импульсами выворки) напряжение затем подается на вход АЦП, который должен «успеть» закончить его преобразование в цифровую форму до поступления следующего импульса выборки. Заметим, что при достаточно быстродействующем АЦП и высокой частоте дискретизации, когда исходный аналоговый сигнал можетбыть непосредственно подан на вход АЦП, который в этом случае корректно выполняет как дискретизацию во времени, так и квантование по уровню. . При шаге квантования

. При шаге квантования  , связанным с

, связанным с  . Относительной разрешающей способностью

. Относительной разрешающей способностью  .

. ,

, . (6.8)

. (6.8)

с некоторого входа iравен

с некоторого входа iравен  выходное напряжение сумматора определяется суммой вида

выходное напряжение сумматора определяется суммой вида (6.9)

(6.9)

;

;  ;

;  выходное напряжение ЦАП с точностью до знака соответствует выражению характеристики преобразования (6.8).

выходное напряжение ЦАП с точностью до знака соответствует выражению характеристики преобразования (6.8). осуществляют коммутацию токов в резисторах 2R на соответствующие входы (

осуществляют коммутацию токов в резисторах 2R на соответствующие входы (  ) инвертирующего сумматора. Современные интегральные ОУ характеризуются малыми входными токами и весьма высоким усилением по напряжению. Пренебрегая малым входным током ОУ, приходим к заключению, что суммарный ток входов (

) инвертирующего сумматора. Современные интегральные ОУ характеризуются малыми входными токами и весьма высоким усилением по напряжению. Пренебрегая малым входным током ОУ, приходим к заключению, что суммарный ток входов (  . Далее, поскольку при конечном выходном напряжении разность потенциалов между входами ОУ с бесконено большим усилением стремится к нулю, для выходного напряжения ЦАП запищем

. Далее, поскольку при конечном выходном напряжении разность потенциалов между входами ОУ с бесконено большим усилением стремится к нулю, для выходного напряжения ЦАП запищем (6.10)

(6.10) , откуда следует

, откуда следует  . Сравнивая (6.10) и (6.8), приходим к выводу, что при

. Сравнивая (6.10) и (6.8), приходим к выводу, что при  и

и  * выходное напряжение ЦАП (см. рис.6.29,в) с точностью до знака соответствует характеристике преобразования (6.8).

* выходное напряжение ЦАП (см. рис.6.29,в) с точностью до знака соответствует характеристике преобразования (6.8). ) положительное напряжение

) положительное напряжение  кГц, а его верхняя граничная частота (по условию однозначности преобразования) составит

кГц, а его верхняя граничная частота (по условию однозначности преобразования) составит  кГц.

кГц.