Студопедия КАТЕГОРИИ: АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция |

ЭЛЕМЕНТЫ ТЕОРИИ БУЛЕВЫХ ФУНКЦИЙДля описания работы ЦЭУ используется математический аппарат алгебры логики, разработку которого связывают с известным английским математиком середины XIX в. Дж.Булем. Функцией алгебры логики(булевой функцией) п-переменных называют функцию F(xi), однозначно сопоставляющую каждому конкретному набору значений 0или 1 переменных (хn-1,... Х1,Х0) одно из двух возможных значений 0 или 1 самой, функции. Каждый конкретный набор значений переменных xi может рассматриваться в виде /^-битного двоичного кода, поэтому общее количество таких наборов т-2п. В свою очередь, совокупность значений функции F(xi), также можно представить w-битным двоичным кодом, откуда заключаем, что общее число различных булевых функций n-переменных равно 2т. В простейшем случае функция F(xt) может быть задана словесным описанием. Например, функция Любая булева функция п переменных может быть полностью задана таблично, если перечислить все возможные наборы переменных х, и указать соответствующие им значения функции

или

Рис.6.1. Таблица истинности некоторых булевых функций трех переменных Конечно, из этих двух вариантов задания функции F( Задание булевых функций таблицей истинности не всегда удобно, так как при больших п она становится слишком громоздкой и трудно обозримой. В этом смысле наиболее привлекателен аналитический способ задания булевых функций в виде так называемых структурных формул, показывающих какие логические операции необходимо выполнить над входящими в них переменными х чтобы получить качения данной функции. Для определения основных типов логических операций достаточно Рассмотреть булевы функции одной и двух переменных. При п=1 имеем всего 4 типа булевых функций, таблица истинности для которых приведена на рис.6.2. Заметим, что функция

Рис.6.2 Таблица истинности совокупности булевых функций одной переменной

Рис.6.3. Обозначения простейших логических элементов: а- повторитель ; б инвертор; в - элемент неравнозначности (сумматор по модулю 2); г - элемент И; д — элемент И—НЕ (Шеффера); е- элемент ИЛИ;ж - элемент ИЛИ НЕ (Пирса)

При п=2 получаем уже 16 различных булевых функций, таблица истинности которых приведена на рис.6.4. Среди булевых функций двух переменных встречаются уже знакомые нам функции генераторов 0

Рис.6.4. Булевы функции двух переменных

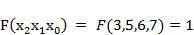

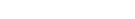

Заметим, что значения Оставшиеся восемь попарно инверсных булевых функций обладают таким замечательным свойством, что они принимают значение 1 (либо 0) на одном единственном наборе переменных и равны 0 (соответственно 1) на всех остальных наборах. Среди этих функций отметим функции Функцию Функцию При помощи операций инверсии (НЕ), конъюнкции (И) и дизъюнкции (ИЛИ) можно получить аналитическую запись произвольной булевой функции. Вначале покажем, что с помощью операций И, НЕ можно описать любую функцию, принимающую значение 1 на единственном наборе переменных, и равную 0 на всех остальных наборах. Запишем, например, выражение для функции Подобным образом с помощью операций ИЛИ, НЕ можно записать любую функцию, принимающую значение 0 на единственном наборе переменных и 1 — на всех остальных, например, Если данная функция равна 1 на нескольких наборах переменных, для каждого из этих наборов запишем соответствующую конъюнкцию, как это было показано выше, а затем все эти конъюнкции свяжем операцией дизъюнкции. Поскольку дизъюнкция равна 1, если хотя бы одно из слагаемых равно 1, получаем аналитическую запись данной функции, равной 1 на всех перечисленных наборах. Аналогично, если функция равна 0 на нескольких наборах, то, записав для каждого из них соответствующую дизъюнкцию, все эти дизъюнкции надо связать операцией конъюнкции. Конечно, из этих двух вариантов записи одной и той же данной функции всегда предпочитают более компактную запись с меньшим количеством входящих в нее членов (конъюнкций или дизъюнкций). Задача 6.2. Составить аналитическую запись булевой функции трех переменных Решение. В соответствии с формулой (6.2) эта булева функция равна 1 на наборах 3,5,6 и 7. Двоичные коды этих наборов

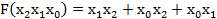

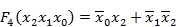

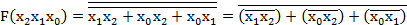

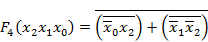

Задача 6.3*. Составить аналитическую запись булевых функций трех переменных F1(x2xix0), F2(x2xlx0), /г3(х2х1х0), F4(x2x{x0), таблица истинности которых представлена на рис.6.1. Ответ:

Задача 6.4.Получить аналитическое выражение булевой функции четырех переменных, принимающей значение 0 на наборах с номерами 2, 9, 15 и значение 1 — на остальных наборах. Ответ: УПРОЩЕНИЕ БУЛЕВЫХ ФУНКЦИЙ Аналитические выражения булевых функций, применяя алгебраические преобразования, как правило, приводят к более простому виду. Для характеристики сложности выражения булевой функции вводят понятие ранга. Рангом булевой функции (или ее отдельного члена) называют общее число входящих в ее выражение переменных (с инверсией или без нее). Смысл дальнейших алгебраических преобразований заключается в том, чтобы, используя соотношения булевой алгебры, получить выражение данной функции с минимальным количеством членов наименьшего ранга, так как для его реализации потребуется не только меньшее количество, но и более простые цифровые элементы (с наименьшим числом входов). Большинство правил алгебраических преобразований булевых функций совпадают с правилами обычной алгебры, но вместе с ними имеют место следующие специфические свойства введенных ранее логических операций: 1) 5)х+х = х 6) х + 1 = 17) Последнюю пару соотношений называют теоремой двойcтве-нности(де Моргана) и формулируют так: отрицание конъюнкции (дизъюнкции) равно дизъюнкции (конъюнкции) отрицаний входящих в неё членов. Путем многократного применения этой теоремы версию сложных булевых выражений обычно опускают до уровня инверсии отдельных переменных. Как правило, для упрощения булевых выражений используют приемы склеивания и поглощения. Всклеивании, как минимум, участвует пара, так называемых, соседнихчленов, представляющих собой члены одинакового ранга, содержащие общую часть Fи некоторую переменную л, которая в один из соседних членов входит с отрицанием, а в другой — без него. При объединении соседних членов операцией дизъюнкции или конъюнкции соответственно получаем

т.е. в любом случае за счет исключения переменной x ранг окончательного выражения уменьшается на единицу. В поглощении участвуют члены различного ранга, причем член меньшего ранга должен обязательно входить в качестве составной части в член более старшего ранга. Объединение таких членов операцией дизъюнкции или конъюнкции дает

т.е. происходит своеобразное «поглощение» члена старшего ранга членом F меньшего ранга. Задача 6.5. Упростить выражение булевой функции

Решение. Заметим, что в данном выражении последний член является соседним для трех остальных членов, поэтому его можно с ними склеить попарно. В соответствии со свойством номер 5 из (6.3) допишем еще два слагаемых вида

Количество слагаемых этого выражениям также их ранг на единицу меньше исходных значений. Задача 6.6. Записать упрощенное выражение булевой функции трех переменных, принимающих значение 0 на наборах с номером 1, 4, 5 и значение 1 — на всех остальных наборах. Ответ: Задача 6.7.* Упростить булевы функции трех переменных, выражения которых записаны в ответах задачи 6.3. 256 Ответ:

Задана 6.8. Привести выражение булевой функции трех переменных Решение. Применим к данной функции двойную инверсию, после чего для внутренней инверсии воспользуемся теоремой Моргана. Окончательно получаем выражение, содержащее только операции И— НЕ.

Задача 6.9.*Привести выражения булевых функций трех переменных, записанных в ответе к задаче 6.7, к виду, содержащему только операции И— НЕ. Ответ:

Стремление сделать процедуру минимизации более наглядной привело к поиску таких форм табличного задания булевых функций, чтобы соседние члены располагались рядом, образуя компактные области, выделение которых упрощало бы их склеивание. Удовлетворяющие этому условию таблицы получили название карт м и н и м и з а ц и и, их применение особенно эффективно при относительно небольшом числе аргументов (n< 5). На рис.6.5 представлены карты минимизации для булевых функций двух, трех и четырех аргументов, а также даны примеры их заполнения. Каждая клетка карты соответствует определенному набору переменных. Заметим, что для всех карт на рис. 6.5 клетка в левом верхнем углу соответствует набору 0, номера остальных наборов указаны на картах (смрис.6.5,а,б) Однако при некотором навыке этого можно не делать, Достаточно лишь пометить чертой строки и столбцы, сопоставленные переменным без инверсии (в данном наборе их значения равны 1). Очевид но, остальные строки и столбцы будут определяться их инверсиями, так как на соответствующих наборах значения этих переменных равны 0.

Рис.6.5. Карты минимизации булевых функций двух (а), трех (б) и четырех (в) аргументов

При заполнении карты для данной булевой функции, как правило, заносят 1 в клетки с наборами, на которых эта функция равна единице. Затем все клетки, содержащие единицы, охватываются совокупностью замкнутых прямоугольных областей с числом клеток в каждой, равным степени двойки. Указанные области могут пересекаться, причем одни и те же клетки могут входить в несколько различных областей. Также допускается сворачивание карты в цилиндр как по горизонтальной,так и по вертикальной осям с объединением противоположных граней. Мини- мизированное выражение булевой функции представляет собой дизъюнкцию членов, сопоставленных каждой из замкнутых областей. Поскольку выделение замкнутой области соответствует операции группового склеивания входящих в нее соседних членов, каждая такая область описывается конъюнкцией только тех аргументов, которые для всех членов в ее пределах имеют общие значения (только с инверсией, либо без нее). Например, для области I (рис.6.5,в) имеем минимизированную запись Задача 6.10.Записать минимизированное выражение булевой функции трех переменных, карта которой представлена на рис. 6.5,б. Решение. На карте рис. 6.5,б можно выделить две замкнутые области. Область 1 образуется из четырех единиц в клетках с номерами 2, 3, 7, 6 Для этой области общим значением будет

Задача 6.11. Получить минимизированное выражение булевой функции трех переменных Ответ:

6.4. ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ Двоичный логический элемент представляет собой электронную Цепь, выходное состояние которой описывается одной из основных булевых функций. Принципиально безразлично, какое из двух возможных входных и выходных состояний логического элемента принимается за 0,а какое — за 1, но чаще всего применяют положительную (прямую) логик у, при которой единица кодируется наличием (высоким уровнем) напряжения, а нуль — его отсутствием (низким уровнем). Выполненные на диодах и транзисторах в микроэлектронном исполнении двоичные логические элементы называют интегральными логическими элементами (ИЛЭ)и широко используют в качестве элементной базы для построения любых, даже самых сложных, современных ЦЭУ.

Рис.6.6. Схемы элементов диодной логики: а—трехвходовый элемент Иб — трехвходовый элемент ИЛИ Логические элементы классифицируют по типам электронных приборов, с помощью которых выполняются основные логические функции. В диодной логике (ДЛ ) для этих целей применяют диоды (рис.6.6). В схеме рис.6.6,а при низком уровне на любом из входов (x2xjx0) соответствующий диод отпирается, и на выходе также будет низкий уровень. Если на всех входах присутствует высокий уровень, все диоды будут закрыты, и на выходе также будет высокий уровень. Для положительной логики такое описание соответствует операции конъюнкции, поэтом) рис.6.6,а представляет схему трехвходового ДЛ-элемента И. Рассуждая аналогично, приходим к выводу, чго схема на рис. 6.6,6 реализует операцию дизъюнкции (ДЛ-элемент ИЛИ).

инвертор, чаще всего используют каскад на биполярном транзисторе, включенном по схеме с общим эмиттером. Объединение диодной логики с транзисторным инвертором позволило создать схемы диоднотранзисторной логики (ДТЛ- э л е м е н т ы), на основе которых строились первые ЦЭУ в интегральном исполнении. Однако при переходе к массовому выпуску цифровых микросхем на основе ДТЛ-элемен- тов выяснилось, что для получения высокого быстродействия входную диодную логику выгоднее заменить интегральныммного- эмиттерным транзистором. Так называют транзистор, у которого имеется обычный переход база — коллектор и несколько переходов база — эмиттер с электрически разделенными областями эмиттеров и общей областью базы. Построенные на его основе ИЛЭ стали называть элементами транзисторно — транзисторной логики (ТТЛ- элементы). На рис.6.7 приведена схема трехвходового ТТЛ-элемента И—НЕ. В этой схеме многоэмиттерный транзистор VT1выполняет логическую операцию И над входными сигналами, а транзистор VT2 обеспечивает инверсию выходного сигнала. При низком уровне напряжения на любом из входов При высоком уровне напряжения на всех трех входах ( До недавнего времени ТТЛ-элементы были ИЛЭ массового применения. Вместе с тем все более жесткие требования, предъявляемые к современным разработкам, постоянно ставили перед разработчиками все более сложные задачи и, в первую очередь, по поиску путей существенного повышения быстродействия, экономичности и надежности ИЛЭ. Было установлено, что быстродействие ТТЛ-элементов в значительной степени ограничивается из-за насыщенного режима работы транзистора VT2, а их надежность и экономичность во многом определяется схемой инвертора. В соответствии с этим постепенно складывалось и представление о ТТЛ-элементах, как об ИЛЭ среднего быстродействия и значительного потребления энергии источника питания, Довольно длительные поиски в области совершенствования технологии производства интегральных схем (ИС) и новых физических эффектов, используя которые можно было бы повысить быстродействие электронных приборов, увенчались успехом и привели к разработке так называемых ТТЛШ-элементов (транзисторно-транзисторная логика с использованием эффекта Шоттки). Смысл этого эффекта заключается в том, что при создании вблизи p-n-перехода области с избыточным количеством свободных носителей заряда (барьер Шоттки) существенно снижается время восстановления обратного сопротивления перехода при его переводе из открытого в закрытое состояние. ВАХ кремниевых диодов с барьером Шоттки отличаются почти втрое меньшим прямым падением напряжения (примерно 0,2 — 0,3 В вместо 0,6 — 0,7 В у обычных диодов). Особенно эффективным оказалось применять переходы с барьером Шоттки в качестве переходов база — коллектор интегральных транзисторов, что позволило избежать глубокого насыщения транзисторов и за счет этого существенно повысить их быстродействие.

Рис 68 Схема базового ТТЛШ-элемента ЗИ — НЕ

На рис.6.8 транзисторы VT3 и VT 4, включенные по схеме составного транзистора, играют роль управляемой коллекторной нагрузки основного транзистора VT5. Сложный инвертор работает таким образом, что при отпирании основного транзистора VТ5 составной транзистор VT3и VT4запирается и наоборот. Необходимые для управления выходными транзисторами противофазные сигналы снимаются с коллектора и эмиттера транзистора и VT2, играющего роль расщепителя фаз (парафазный усилитель). Основной транзистор VT5 должен пропускать на землю значительные Поскольку при размещении ТТЛШ-элементов на печатных платах больших размеров на длинных проводниках могут накапливаться значительные паразитные заряды, диоды VD1-VD3 открываясь, поглощают их энергию и тем самым защищают эмиттерные переходы транзистора VT1 от пробоя. Все описанные схемотехнические приемы позволили в Рачительной мере повысить эксплуатационную надежность ТТЛШ-микросхем, что особенно важно при их массовом применении За счет использования транзисторов с барьером Шоттки удалось почти на порядок повысить быстродействие ТТЛШ-элементов, а благодаря Последним достижениям в технологии производства ИС и несколько снизить их энергопотребление. Однако существенному повышению экономичности всех ТТЛ-схем препятствует то, что по принципу работы они встатических состояниях потребляют входные токи На рис.6.9,а представлена схема КМОП-инвертора, содержащего комплементарную пару МОП-транзисторов VT1 и VT2, индуцированные каналы которых (соответственно, р- и n-типов) включены последовательно. Принцип работы этого инвертора подобен принципу работы сложного инвертора (см.рис.6.8) ТТЛШ-элементов, но применение комплементарной пары выходных транзисторов позволило исключить фазорасщепи- тель и тем самым упростить его схему. При низком (нулевом) уровне напряжения на затворах транзисторов VT1 и VT2 потенциал затвора VT1 окажется ниже потенциала его истока и подложки типа п, в результате чего в ее поверхностном слое вблизи затвора индуцируется канал с проводимостью типа р. Транзистор VT1откроется, n-канальный транзистор VT2 будет закрыт, и на выходе инвертора появится высокий уровень напряжения.

Рис.6.9. Схемы КМОП- элементов: а- схема инвертора; б- элемент 2И-НЕ; в- лемен 2ИЛИ-НЕ С другой стороны, при высоком уровне напряжения на затворах транзисторов VT1 и VT2 потенциал затвора VT2 будет выше потенциала его истока и подложки типа р, из-за чего в ее поверхностном слое вблизи затвора индуцируется канал с проводимостью типа п. ТранзисторVT2откроется, р -канальный транзистор VT1 будет закрыт, и на выходе появится низкий уровень напряжения. Поскольку в цепях затворов полевых транзисторов токи практически отсутствуют, в статических состояниях КМОП-микросхемы не потребляют энергии от источника питания Еп. Кратковременные импульсы тока будут возникать только в моменты переключения инвертора из одного состояния в другое. При построении КМОП-элементов с несколькими входами для каждого входа используют инвертор (рис.6.9,а), определенным образом соединяя каналы транзисторов VT1 и VT2 . Схемы КМОП-элементов типа 2И — НЕ и 2ИЛИ — НЕ показаны на рис.6.9,б,в. Например, если транзисторы VT1 (VT10 и VT11 ) двух инверторов включить параллельно, а транзисторы VT2 (VT20 и VT21) — последовательно, низкий уровень на общем выходе (рис.6.9,б) появится только в том случае, когда на обоих входах (x1,x0 ) одновременно присутствуют высокие уровни напряжения, что соответствует элементу 2И — НЕ. Рассуждая аналогично, приходим к выводу, что при соединении каналов транзисторов VT 10 и VT 11 двух инверторов по схеме 6.9,а последовательно, а транзисторов VT20 и VT21 — параллельно, получим схему (см.рис.6.9,в), высокий уровень на выходе которой будет только в том случае, когда на обоих входах (ххх0 ) одновременно присутствуют низкие Уровни напряжения, что соответствует элементу 2ИЛИ — НЕ. Недостаток микросхем на полевых транзисторах —несколько меньшее быстродействие по сравнению с ТТЛ- и ТТЛШ-элементами. Помимо рассмотренных существуют логические элементы других типов, например. ЭСЛ-элементы (эмиттерно-связанная логика), обладающие высоким быстродействием. Однако увеличение быстродействия в них достигается це- «ой значительно большего потребления энергии источника питания. В настоящее время выпускается широкий набор ИЛЭ в составе микросхем различных серий. Выбор подходящих ИЛЭ при построении более Ложных ЦЭУ производится по некоторым их параметрам, к числу которых помимо напряжения питания и средней мощности потребления

Рис .6.10. Функциональный состав микросхемы типа 2 (2 х 2И — 2 ИЛИ — НЕ)

Перед обозначением типа логического элемента обычно цифрой указывают количество его входов. Если в составе ИЛЭ, реализу ющего некоторую комбинацию булевых функций, имеются однотипные логические элементы, их количество указывают цифрой слева, за которой следует символ X. Наконец, в одном корпусе ИС может быть выполнено несколько однотипных ИЛЭ. При описании состава такой ИС обозначение ИЛЭ помещают в круглые скобки, а перед ними цифрой указывают количество элементов в одном корпусе. Например, описание 2(2 х 2И — 2ИЛИ — НЕ) соответствует ИС. содержащей в одном корпусе два однотипных комбинированных логических элемента. Каждый из них представляет собой два двухвходовых элемента И, выходы которых подключены к двухвходовому элементу ИЛИ — НЕ (рис. 6.10) . Коэффициентом разветвления по выходу Иногда возникает необходимость объединения выходов нескольких ИЛЭ с целью перехода к общей выходной цепи (выходной шине). При этом часто используют так называемое «монтажное ИЛИ», для чего выпускаются специальные ИЛЭ (расширители), выходные цепи которых выполняют по схеме с открытым коллектором (реже с открытым эмиттером). Открытые коллекторы нескольких расширителей можно объединить и через общий резистор подктючить к источнику питания (или соответственно к общему проводу ). В последнее время широкое распространение получили логические элементы, в которых при наличии специального управляющего импу льса возможно отключать их выходы от нагрузки. Такое управляемое отключение выхода ИЛЭ называют переходом в третье состояние. Обычно в схемах ИЛЭ с третьим состоянием применяют инверторы (см рис.6.8 или 6 9). но помимо обычных двух состояний 1 и 0. когда один из выходных транзисторов заперт, в них предусмотрено третье состояние, при котором одновременно закрыты все транзисторы выходного каскада Время задержки распространения сигнала припереключении ИЛЭ из состояния 1 в 0 (t310) и наоборот определяется интервалом времени между моментами достижения выходным и входным напряжением уровня половины амплитуды соответствующего сигнала. Чаще всего для сравнительной оценки быстродействия различных ИЛЭ используют среднее время задержки t3 , равное полусумме времен Для характеристики общего уровня достижений в схемотехнике и технологии производства различных типов И С применяют обобщенный параметр, называемый работой переключения А (работа попереносу одного бита информации совхода на выход ИЛЭ). Работа переключения А равна произведению средней мощности потребления Рср на среднюю задержку распространения t3 (А= Рсрt3). Если Рср взять в милливатах (мВт), at3 — в наносекундах (нс), работа переключения А будет выражаться в пикоджоулях (пДж). В табл. 6.1 для сравнительной оценки достигнутого уровня приведены параметры различных серий отечественных ИЛЭ, выполненных по различным видам технологии их производства. Из табл.6.1 следует, что наименьшая работа переключения в наиболее совершенной из серий ИС на биполярных транзисторах (ТТЛШ серия 1533), в основном, достигнута путем существенного повышения их быстродействия. Более низкая работа переключения ИЛЭ на полевых транзисторах (при типичных значениях задержки КМОП-микросхем порядка нескольких десятков наносекунд) объясняется малым значением Рср . Дальнейшего снижения значений А для современных лучших ИС этого типа удалось достигнуть лишь после создания МОП-транзисторов с исключительно малой (до 1,2 мкм) длиной канала.

Общие сведения о микросхеме указываются в ее условном обозначении, нанесенном на корпусе ИС. Оно включает в себя номер серии ИС (обычно три или четыре цифры), перед которым может быть одна или две буквы. У микросхем широкого применения первой ставят букву К, вторая буква характеризует материал корпуса для защиты от воздействия внешней среды (Р — пластмассовый, М или С — металло- или стеклокерамический, соответственно). За номером серии следуют две буквы, поясняющие функциональное назначение ИС. Для всех ИЛЭ первой из них следует буква Л, вторая буква определяет тип логического элемента (И — элемент И, Л — ИЛИ, Н— НЕ, Д — расширитель по ИЛИ, А — элемент И — НЕ, Е — элемент ИЛИ — НЕ. Р — комбинированный элемент И — ИЛИ — НЕ). Цифра в конце условного обозначения соответствует порядковому номеру разработки ИС в составе данной серии. Например, микросхема КР1533ЛА24 представляет собой ИС широкого применения (первая буква К), в пластмассовом корпусе (вторая буква Р), имеет номер серии 1533 (ТТЛШ-схемотехника), относится к группе ИЛЭ (буква Л), а по функциональному назначению это элемент типа И—НЕ (вторая буква А) с порядковым номером разработки 24. Вопрос 6.1. Каким будет выходной сигнал одного из элементов (см.рис.6.10), если на один из его входов подать сигнал x, а на все три оставшихся входа — сигналы высокого уровня? Варианты ответа: 6.1.1. Выходное состояние элемента будет повторять сигнал л. 6.1.2. Выходное состояние элемента будет инверсным сигналу jc. 6.1.3. Независимо от состояния на входе х на выходе будет сигнал низкого уровня. 6.1.4. Независимо от состояния на входе л на выходе будет сигнал высокого уровня. ТРИГГЕРЫ Вместе с ИЛЭ к базовым элементам относят и триггеры*[2], которые находят самостоятельное применение и широко используются при построении более сложных ЦЭУ. Триггером называют устройство, кото- рое может находиться в одном из двух устойчивых состояний и переходить из одного состояния в другое под воздействием активного уровня логических сигналов, поступающих на его информационные входы. Состояние триггера определяется по выходному сигналу. При этом говорят, что триггер установлен, если на его выходе присутствует логическая 1, и сброшен — если 0. В триггерах с прямым управлением активным уровнем считается уровень логической 1, а в триггерах с инверсным управлением — уровень логического 0. Существенно отметить, что после переключения триггера входной активный уровень может быть снят, но триггер продолжает оставаться в том состоянии, которое он приобрел под воздействием этого сигнала. Таким образом триггер является простейшим элементом памяти, способным хранить один бит информации (либо 1, либо 0). Как правило, для удобства использования триггеры имеют два выхода, один из которых называют прямымQ,а другой — инверсным Помимо информационных входов, обозначаемых буквами R,S,J,K,D,T, триггеры могут содержать и вспомогательные (управляющие) входы, например, предварительной установки или вход синхронизации С, при наличии которого переключение триггера может происходить только в строго фиксированные моменты времени, когда на этом входе присутствует активный уровень сигнала синхронизации. Триггеры, которые реагируют на информационные сигналы только при наличии сигнала синхронизации, называют синхронными.В отличии от них асинхронные триггеры реагируют на информационные сигналы в момент их поступления. Синхронные триггеры, в свою очередь, могут быть со статическим и динамическим управлением. Для того чтобы синхронный триггер со статическим управлением смог воспринимать сигналы на информационных входах, на его входе синхронизации Сдолжен присутствовать уровень логической единицы (прямой Г-вход) или логического нуля (инверсный С-вход). Синхронный триггер с динамическим управлением реагирует на информационные сигналы только в момент изменения сигнала на С-входе от 0 до 1 (прямой динамический С-вход), либо от 1 до 0 (инверсный динамический С-вход). На рис. 6.11,а,б показаны соответственно обозначения синхронного триггера с прямым и инверсным динамическим управлением. Для синхронного триггера со статическим управлением иногда используют обозначение С-входа, показанное на рис.6.11,в, но чаще всего у ( С-входа вообще не ставят никаких специальных значков.

Рис.6.11. Обозначения синхронного триггера, а — с динамическим прямым С-входом; б — с динамическим инверсным С-входом; в — со статическим управлением

По функциональным возможностям различают: триггер с раздельной установкой состояний 0 и 1 (триггер с установочными входами, RS-триггер); триггер со счетным входом (счетный триггер, T-триггер); триггер задержки с приемом информации по одному входу (D-триггер); универсальный триггер с информационными входами К и J (JK- триггер) Для полного описания триггера достаточно задать закон его функционирования и структурную схему Асинхронный RS-триггер с раздельной установкой состояний 1 и 0 имеет всего лишь два информационных входа — S (вход установки) и R (вход сброса)*. При активном уровне сигнала на входе установки S и пассивном уровне на входе R триггер, независимо от предыдущего состояния, принимает на выходе Q состояние 1. С другой стороны, при активном уровне сигнала на входе сброса R и пассивном уровне на входе S независимо от предыдущего состояния триггер переводится в состояние Q=0 (сбрасывается). При пассивном уровне сигнала на обоих входах состояние триггера не изменяется (режим хранения предыдущего состояния). Наконец, последняя из возможных комбинаций, когда на обоих входах одновременно присутствуют активные уровни, для триггеров этого типа просто запрещается, так как по описанному закону работы его выходное состояние будет непредсказуемым Сформулированный выше словесно закон функционирования на рис. 612 представлен в виде таблицы переходов асинхронного RS -триггера, где обозначено Qt—выходное состояние триггера до момен га подачи соответствующей комбинации уровней (RtStна его информационные входы, Qt+1 — состояние триггера после этого момента, А — активный, П — пассивный уровень. Как следует из этой таблицы, выходное состояние триггера Qt+1 представляется булевой функцией трех переменных RtSt и Qt Запрещенное состояние следует рассматривать как факультативные условия, доопределяя которые различным образом, можно получать разные структурные схемы /^-триггера.

рис 6 13. Карта минимизации для асинхронного RS-триггера Вначале запишем аналитические выражения, а по ним построим структурные схемы двух наиболее распространенных реализаций Я S-триггера (на элементах ИЛИ—НЕ и на элементах И—НЕ). Используя прямую логику на входе (А= 1 П=0), рассмотрим таблицу переходов (рис.6.12). В строке с номером 0, соответствующей режиму хранения, единичное состояние на выходе будет при Дополняя на факультативных условиях Фзначения |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2018-05-10; просмотров: 419. stydopedya.ru не претендует на авторское право материалов, которые вылажены, но предоставляет бесплатный доступ к ним. В случае нарушения авторского права или персональных данных напишите сюда... |

равна 1, если все три ее переменные или любая пара.из них равны 1, в противном случае

равна 1, если все три ее переменные или любая пара.из них равны 1, в противном случае  . По принципу работы некоторых цифровых электронных устройств отдельные конкретные наборы переменных могут быть исключены (запрещенные наборы), что трактуется как наличие факультативных условий. Обычно на факультативных наборах булевую функцию доопределяют таким образом, чтобы получить наиболее простую ее запись.

. По принципу работы некоторых цифровых электронных устройств отдельные конкретные наборы переменных могут быть исключены (запрещенные наборы), что трактуется как наличие факультативных условий. Обычно на факультативных наборах булевую функцию доопределяют таким образом, чтобы получить наиболее простую ее запись. . Построенную таким образом таблицу называют таблицей истинности. Как правило, в таблице истинности наборы переменных располагаются £ порядке нарастания десятичного эквивалента их двоичного кода. В качестве примера на рис.6.1 представлена таблица истинности некоторых булевых функций трех переменных и в том числе функции

. Построенную таким образом таблицу называют таблицей истинности. Как правило, в таблице истинности наборы переменных располагаются £ порядке нарастания десятичного эквивалента их двоичного кода. В качестве примера на рис.6.1 представлена таблица истинности некоторых булевых функций трех переменных и в том числе функции  (6.2а)

(6.2а) . (6.26)

. (6.26)

) стремятся выбрать наиболее компактный, в котором перечислено меньшее количество наборов переменных

) стремятся выбрать наиболее компактный, в котором перечислено меньшее количество наборов переменных  принимает значение 0 независимо от значения аргумента

принимает значение 0 независимо от значения аргумента  независимо от

независимо от  . Наконец, функция

. Наконец, функция  принимает инверсные значения аргумента и определяет операцию инверсии (отрицания), которую обозначают чертой сверху аргумента

принимает инверсные значения аргумента и определяет операцию инверсии (отрицания), которую обозначают чертой сверху аргумента

и 1

и 1  , а также повторения и инверсии переменных:

, а также повторения и инверсии переменных:  ;

;  ;

;  . Далее отметим пару взаимно инверсных функций

. Далее отметим пару взаимно инверсных функций  . Функция

. Функция  принимает значение 1, если входящие в нее переменные имеют различные значения, и называется функцией неравнозначности (суммы по модулю2). Операция суммы по модулю 2 обозначает' ся символом 0 и выполняется по следующим правилам:

принимает значение 1, если входящие в нее переменные имеют различные значения, и называется функцией неравнозначности (суммы по модулю2). Операция суммы по модулю 2 обозначает' ся символом 0 и выполняется по следующим правилам:

;

;  ;

;  .

. , а также

, а также  . Обозначение элемента И, реализующего операцию конъюнкции, приведено нарис. 6.3,г. Элемент, реализующий функцию

. Обозначение элемента И, реализующего операцию конъюнкции, приведено нарис. 6.3,г. Элемент, реализующий функцию  , инверсную конъюнкции, называют элементом И — НЕ (элементом Шеффера).Его обозначение дано на рис. 6.3,д.

, инверсную конъюнкции, называют элементом И — НЕ (элементом Шеффера).Его обозначение дано на рис. 6.3,д. . Обозначение элемента ИЛИ показано на Рис.6.3,е. Функцию

. Обозначение элемента ИЛИ показано на Рис.6.3,е. Функцию  , инверсную дизъюнкции, записывают в виде

, инверсную дизъюнкции, записывают в виде  ).Для этого рассмотрим произведение

).Для этого рассмотрим произведение  , в которое переменная

, в которое переменная  ). По определению конъюнкции, функция равна 1; если оба сомножителя равны 1, что соответствует набору с номером 1, откуда получаем запись

). По определению конъюнкции, функция равна 1; если оба сомножителя равны 1, что соответствует набору с номером 1, откуда получаем запись

(см.рис.6.4), принимающую единственное значение 0 на наборе с номером 2 (

(см.рис.6.4), принимающую единственное значение 0 на наборе с номером 2 (  l,

l,  принимает единственное значение 0 именно на наборе с номером 2.

принимает единственное значение 0 именно на наборе с номером 2. . Каждому из этих наборов сопоставим конъюнкцию,в которой переменную берем без инверсии, если она входит в набор созначением 1 или с инверсией, если в данном наборе она равна 0. Указанные конъюнкции объединяем операцией дизъюнкции, что дает запись

. Каждому из этих наборов сопоставим конъюнкцию,в которой переменную берем без инверсии, если она входит в набор созначением 1 или с инверсией, если в данном наборе она равна 0. Указанные конъюнкции объединяем операцией дизъюнкции, что дает запись

;

;

.

. 2)х

2)х  = 03)х +

= 03)х +  8)

8)

,

,

удобному для ее реализации на элементах И—НЕ.

удобному для ее реализации на элементах И—НЕ.

.

. , таблица истинности которой приведена на рис.61.

, таблица истинности которой приведена на рис.61. логического нуля, направленный из эмиттера в сторону входа. Значение этого тока определяется сопротивлением резистора RБ в цепи базы, а также прямым сопротивлением перехода (типичное значение тока

логического нуля, направленный из эмиттера в сторону входа. Значение этого тока определяется сопротивлением резистора RБ в цепи базы, а также прямым сопротивлением перехода (типичное значение тока  По принципу работы ТТЛШ-элементы. в основном, подобны обычным ТТЛ-элементам, но выгодно отличаются от них помимо применения транзисторов с барьером Шоттки более сложной схемой инвертора(рис.6.8), что позволило увеличить его нагрузочную способность и снизитьвлияние технологического разброса параметров транзистороъ на эксплуатационные характеристики ТТЛШ-элементов при их массовом выпуске.

По принципу работы ТТЛШ-элементы. в основном, подобны обычным ТТЛ-элементам, но выгодно отличаются от них помимо применения транзисторов с барьером Шоттки более сложной схемой инвертора(рис.6.8), что позволило увеличить его нагрузочную способность и снизитьвлияние технологического разброса параметров транзистороъ на эксплуатационные характеристики ТТЛШ-элементов при их массовом выпуске. ограничивает сквозной ток от источника питания Еп на землю в моменты переключения инвертора, когда на короткое время все его выходные транзисторы оказываются открытыми. При частых переключениях

ограничивает сквозной ток от источника питания Еп на землю в моменты переключения инвертора, когда на короткое время все его выходные транзисторы оказываются открытыми. При частых переключениях

(Равной полусумме мощностей потребления в состоянии 1 и 0) относятся вид реализуемых булевых функций или некоторой их комбинации, коэффициент разветвления по выходу, характеризующий нагрузочную способность ИЛЭ, время задержки распространения сигнала, определяющее быстродействие элемента, и др.

(Равной полусумме мощностей потребления в состоянии 1 и 0) относятся вид реализуемых булевых функций или некоторой их комбинации, коэффициент разветвления по выходу, характеризующий нагрузочную способность ИЛЭ, время задержки распространения сигнала, определяющее быстродействие элемента, и др. называют максимально допустимое количество входов однотипных ИЛЭ, которые могут быть подключены к выходу7 данного элемента. Для разных видов ИЛЭ значение

называют максимально допустимое количество входов однотипных ИЛЭ, которые могут быть подключены к выходу7 данного элемента. Для разных видов ИЛЭ значение  и

и

. Если триггер установлен (в состоянии 1), на его прямом выходе будет логическая 1, а на инверсном — логический 0.

. Если триггер установлен (в состоянии 1), на его прямом выходе будет логическая 1, а на инверсном — логический 0. Строка с номером 1 (режим установки в 1) доставляет

Строка с номером 1 (режим установки в 1) доставляет  что дает еще два слагаемых

что дает еще два слагаемых