Студопедия КАТЕГОРИИ: АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция |

Синтезировать модификации схем ТТЛ с простым и сложным инверторами с низкоомным путем для рассасывания заряда Q2.Стр 1 из 12Следующая ⇒ Сравнительный анализ схемотехнических базисов ЭВМ. Взаимосвязь логического, схемотехнического и конструкторского этапов проектирования.

КБиС- комплементарные биполярные схемы (биполярные схемы, содержащие как n-p-n, так и p-n-p транзисторы). БиКМОП – схемы, содержащие биполярные тр-ры одного типа и МОП тр-ры обоих типов (n- канальные и p- канальные). КБиКМОП – схемы содержащие биполярные тр-ры обоих типов и МОП тр-ры обоих типов. Лидером по быстродействию является схема ЭСЛ, но она же и занимает «первое» место по порождению помех. Если выбирать лидера по совокупности параметров, то им являются n-МОП схемы. Претендентами для исполнения в нанотехнологиях являются элементы с оптимальными математическими моделями, приспособленными для вертикальной интеграции. Это n-МОП схемы и практически все схемы переходной схемотехники. 2. Реализация функции Монтажное ИЛИ в ЭСЛ-схемотехнике.

Если включить параллельное соединение транзисторов, то будет реализована вспомогательная функция ИЛИ. Достоинства:Функционально полный базис; Маленький логический перепад. Недостатки: Маленькая помехоустойчивость; Rвых = [кОм] Þ большое время задержки. Для уменьшения выходного сопротивления используется стандартный прием- подключение к выходу эмиттерных повторителей, выходное сопротивление которых определяется сопротивлением открытого тр-ра.

При объединении выходов эмиттерных повторителей реализуется функция Монтажное ИЛИ.

Пример:

Вывод: использование эмиттерных повторителей в ЭСЛ дает два преимущества.

Синтезировать принципиальную схему ТТЛШ без резисторов, разработать структуру (математическую модель-дерево); сделать 3-х мерный вариант; описать работу полученного элемента. Схемотехника МОП-вентилей. Принципы синтеза. МОП вентиль И-НЕ.

Недостаток: разница в проводимости нагрузочного транзистора T3 и транзисторов логической части Т1 и Т2.((R1+R2)<<R3). Это может привести к увеличению площади топологии схемы пропорционально количеству входов вентиля.

МОП вентиль ИЛИ-НЕ.

Принципы синтеза. 1. Общая инверсия реализуется с помощью нагрузочного МОП транзистора, включенного между выходом и напряжением питания. 2. Зависимое ИЛИ реализуется параллельным соединением МОП транзисторов или подсхем, включенных между выходом и «землей». 3. Зависимое И реализуется последовательным соединением МОП транзисторов или подсхем, включенных между выходом и «землей».

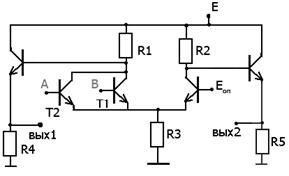

Синтезировать модификации схем ТТЛ с простым и сложным инверторами с низкоомным путем для рассасывания заряда Q2. Модификации схемы ТТЛ со сложным инвертором (варианты оптимизации). 1. Схема отличается от стандартной тем, что диод из эмиттерной цепи Т4 перенесен в базовую.

Для исправления передаточной характеристики используется схема оптимизации 2.

2. В этой схеме вместо сопротивления R3 используется ключ R3-R5-T5. Транзистор Т3 открывается только тогда, когда будет открыт не только Т2, но и Т5. А Т2 и Т5 открываются одновременно. Фактически, Т2-Т5 – это как бы единый транзистор.

3. Оптимизация нагрузочной способности.

Быстродействие здесь становится немного хуже, т.к. емкость увеличивается. Транзисторы Т4-Т5 составляют пару Дарлингтона. Улучшение быстродействия схемы ТТЛ со сложным инвертором. Алгоритмы улучшения: 1. быстро уменьшать заряды Q2, Q3 Или 2. не накапливать эти заряды. 4. Использование медленного диода.

При подаче запирающего напряжения диод еще открыт. Const = Q = ¯t * Ip Ip – ток рассасывания Медленный диод формирует низкоомный путь для рассасывания Q3. 5.

Данный вариант способствует уменьшению Q3. ¯Q3 ® ¯ tp tp – время рассасывания. 6. Использование диодов Шоттки.

Диоды Шоттки формируют низкоомный путь для отвода Q3 из базы насыщенного транзистора Т3. 7. Схема, в которой Q2=Q3=0 в режиме насыщения.

Qi=0 tТТЛШ = 3 нс tТТЛ = 10 нс

|

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2018-06-01; просмотров: 339. stydopedya.ru не претендует на авторское право материалов, которые вылажены, но предоставляет бесплатный доступ к ним. В случае нарушения авторского права или персональных данных напишите сюда... |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

- нагрузочная способность

- нагрузочная способность