Студопедия КАТЕГОРИИ: АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция |

Выходы с открытым коллекторомИногда требуется логически соединять выходы многих элементов. Например, для 20 выходов потребовалось бы проложить 20 проводов к элементу с 20 входами. Использование элементов с открытым коллектором позволяет обойти эту трудность. У подобного элемента выходным каскадом служит n‑p‑n транзистор, эмиттер которого соединен с землей (рис. 5.9).

Рис. 5.9. Реализация логической функции путем соединения выходов элементов с открытым коллектором В отличие от обычных двухтактных выходных каскадов такие выходы можно соединять параллельно друг другу и подключать к общему коллекторному резистору. Выходное напряжение принимает значение, соответствующее состоянию H, только в том случае, когда все выходы оказываются в состоянии H. В позитивной логике это равнозначно функции И. Вместе с тем выходное напряжение соответствует низкому уровню L, когда один или несколько выходов оказываются в состоянии L. Так реализуется функция ИЛИ в отрицательной логике. Поскольку подключения осуществляются с помощью внешнего монтажа, такие соединения называют «монтажным» И и «монтажным» ИЛИ. Выходы элементов характеризуются низким выходным сопротивлением только в состоянии L (логический нуль), поэтому их называют также схемами с низкоомным выходным активным нулем. Недостаток применения выходов с открытым коллектором заключается в более медленном нарастании выходного напряжения по сравнению с двухтактным выходом, так как паразитные емкости могут заряжаться только через резистор RC.

Трехстабильные выходы Имеется еще одно важное применение параллельного включения выходов логических элементов, упрощающее схемы, – ситуация, когда один из нескольких элементов по выбору должен определять логическое состояние сигнального проводника.  В таком случае говорят о системе с шинной организацией. Проблема решается также посредством элементов с открытым коллектором, если все выходы переводятся в высокоомное состояние H. Здесь удается обойти принципиальный недостаток медленного нарастания сигнала, применив элементы не с открытым коллектором, а с трехстабильным выходом. Это схема с двухтактным выходом, отличающимся тем, что он может переводиться в состояние с высоким выходным сопротивлением при помощи специального управляющего сигнала. Описанное состояние называют состоянием Z. Принцип схемотехнической реализации показан на рис. 5.10. Когда разрешающий сигнал EN = 1, схема работает как обычный инвертор: при x = 0 имеем z1 = 0 и z2 = 1, то есть T1 заперт, а T2 открыт. При x = 1 T1 открыт, а T2 заперт. Но если управляющая переменная EN = 0, z1 = z2 = 0, так что оба выходных транзистора заперты, получаем состояние Z с высоким выходным сопротивлением.

Рис. 5.10. Инвертор с трехстабильным выходом и его условное обозначение.

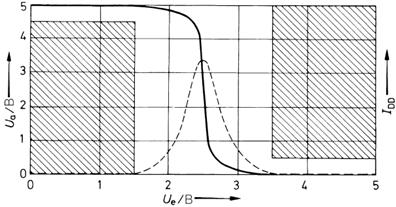

Комплементарная МОП логика Семейство логических схем типа КМОП отличается особой экономичностью по электропитанию. Схема КМОП инвертора приведена на рис. 5.11. Характерно, что она образована исключительно МОП транзисторами с индуцированным каналом. При этом истоковые выводы n‑канального МОП транзистора соединены с землей, а p‑канального – с источником напряжения питания VDD. Таким образом, оба МОП транзистора функционируют в схеме с общим истоком, усиливают и инвертируют входное напряжение, причем в каждый момент времени один из них играет роль рабочего нагрузочного резистора для другого. Модуль порогового напряжения обоих МОП транзисторов составляет около 1,5 В, поэтому при напряжении питания 5 В по крайней мере один из них открыт. При Ue = 0 открыт p‑канальный МОП транзистор T2, а n‑канальный T1 закрыт. Выходное напряжение становится равным VDD. При Ue = VDD закрыт T2, а T1 открыт и выходное напряжение принимает нулевое значение. Ясно, что в стационарных условиях ток через схему не идет. Слабый сквозной ток протекает только при переключении, пока входное напряжение находится в пределах |Up| < Ue < VDD – |Up|. Изменение

Рис. 5.11. КМОП инвертор Рис. 5.12. Передаточная характеристика логического КМОП элемента при напряжении питания 5 В. Заштрихованы допустимые пределы; пунктир обозначает изменение тока.

этого тока и передаточная характеристика показаны на рис. 5.12. Логические уровни зависят от выбора напряжения питания. Диапазон допустимого напряжения питания КМОП приборов весьма широк. У схем с кремниевым затвором он лежит между 3 и 6 В, а у схем с металлическим затвором простирается от 3 до 15 В. По соображениям симметрии порог переключения всегда выбирают равным половине напряжения питания. Поэтому при питающем напряжении 5 В уровень H должен быть выше 3,5 В (см. рис. 5.12). По указанной причине для управления КМОП элементом с помощью ТТЛ выхода требуется дополнительный резистор установки рабочей точки. Зато полностью совместимы с ТТЛ элементами схемы типа HCT, на входе которых имеется специальный преобразователь уровня. Потенциал на открытых входах КМОП не определен («плавающий»). Поэтому их необходимо соединять с землей или VDD. Это рекомендуется даже для неиспользуемых элементов, иначе возникает входной потенциал и через оба транзистора начинает течь более или менее значительный сквозной ток, вызывая неожиданно большие потери. 5.5.1. Логические КМОП элементы На рис. 5.13 представлен КМОП элемент ИЛИ–НЕ, функционирующий по тому же принципу, что и описанный инвертор. Чтобы сделать управляемый резистор высокоомным при переходе одного из входных напряжений в состояние H, требуется последовательная цепочка из соответствующего числа p‑канальных полевых транзисторов. Заменяя последовательную цепочку параллельной, вместо логического элемента ИЛИ–НЕ получают элемент И–НЕ (рис. 5.14).

Рис. 5.13. КМОП элемент ИЛИ–НЕ Рис. 5.14. КМОП элемент И–НЕ Представление чисел Цифровые схемы способны обрабатывать только двоичные данные, поэтому приходится переводить числа из привычной десятичной системы счисления в двоичную, чтобы иметь возможность представлять числа посредством логических переменных, сами числа должны отображаться в виде последовательности двоичных чисел, то есть способных принимать только два значения. Двоичную цифру называют битом. Существует особая двоичная форма представления чисел с помощью двоичных знаков (двоичная система счисления), в которой разряды числа упорядочены по возрастающей степени числа 2. При этом цифра 1 отождествляется с логической единицей, а цифра 0 – с логическим нулем. Будем обозначать строчными буквами логическую переменную, характеризующую отдельное знакоместо в числе, а прописными буквами – все число. Тогда для представления числа из N разрядов в двоичном виде можно записать:

Разумеется, следует всегда четко разграничивать вычислительные операции с числами и составление функций из логических переменных. Еще раз поясним это различие на примере. Рассчитаем выражение 1 + 1. Полагая, что знак (+) обозначает сложение в десятичной системе счисления, получим соотношение: 1 + 1 = 2. Сложение в двоичной системе дает 1 + 1 = 102 (читается: единица–нуль). Если полагать, что знак (+) означает дизъюнкцию логических переменных, находим: 1 + 1 = 1. 5.6.1. Положительные целые числа в двоичном коде Самым простым средством представления двоичных чисел служит двоичный код. Разряды упорядочены по возрастанию степени числа 2. В соответствии с десятичной системой просто записывают последовательность цифр {zN–1…z0} и мысленно складывают соответствующие степени числа 2. Пример.

5.6.2. Восьмеричный код Очевидно, двоичный код воспринимается с трудом. Поэтому пользуются сокращенной формой записи, при которой каждые три разряда двоичного кода сводятся к одной цифре, а значение такого 3-разрядного двоичного числа записывается в десятичном виде. Поскольку соответствующие числа упорядочены по возрастанию степеней 23 = 8, такой код называют восьмеричным. Пример.

5.6.3. Шестнадцатеричный код Еще один распространенный способ сокращенной записи состоит в том, чтобы сводить к одному числу по четыре двоичных разряда. В таком случае возникающие числа упорядочиваются по возрастанию степени числа 24 = 16, в силу чего код получил название шестнадцатеричного. В каждом разряде числа могут принимать значения от 0 до 15, но для этого десятичных цифр уже недостаточно, и потому цифры от 10 до 15 отображаются символами от A до F. Пример.

|

||

|

Последнее изменение этой страницы: 2018-04-12; просмотров: 1055. stydopedya.ru не претендует на авторское право материалов, которые вылажены, но предоставляет бесплатный доступ к ним. В случае нарушения авторского права или персональных данных напишите сюда... |