Студопедия КАТЕГОРИИ: АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция |

Схемотехническая реализация основных логических функцийМы рассматриваем логические схемы, не вдаваясь в подробности их внутреннего устройства. Такой подход оправдан тем, что в современной цифровой технике имеют дело почти исключительно с интегральными микросхемами, у которых есть только вышеупомянутые входы, выходы и выводы для подключения питания. Для реализации отдельных основных логических функций имеется множество схемотехнических средств, различающихся энергопотреблением, напряжением питания, уровнями 0 и 1, быстродействием логического элемента и нагрузочными свойствами. Для выбора оптимального варианта надо хотя бы в общих чертах знать внутреннее устройство таких схем. Поэтому далее будут представлены важнейшие типы интегральных микросхем. Соединяя микросхемы, нередко к одному выходу подключают несколько входов других логических элементов. Максимально допустимое количество схем определенного типа, подключаемых к выходу без ущерба для запаса по помехоустойчивости, характеризуется коэффициентом разветвления по выходу. Если он равен 10, то к выходу можно подключать до 10 логических элементов. При недостаточной величине данного коэффициента вместо стандартного логического элемента применяется элемент повышенной мощности (буфер). У логического элемента каждому состоянию входа соответствует определенное состояние выхода. Таким состояниям присваиваются обозначения 1 или 0 в зависимости от того, будет ли напряжение больше уровня UH или меньше уровня UL. Функцию логического элемента можно описать с помощью таблицы уровней. Однако этим еще не определяется тип функции, которая реализуется посредством данного логического элемента, поскольку не указано соотношение между уровнем и логическим состоянием. Выбор названного соответствия произволен, но внутри конкретного прибора он задается однозначно. Соответствие верхнего уровня H единице, а нижнего L – нулю называется положительной логикой. Обратное соответствие называется отрицательной логикой.  5.2.1. Транзисторно-транзисторная логика У стандартной схемы ТТЛ (рис. 5.7) собственно логическая операция выполняется транзистором T1 с несколькими эмиттерами. Когда все входные уровни отвечают состоянию H, ток через резистор R1 протекает по открытому в прямом направлении переходу база–коллектор входного транзистора в цепь базы транзистора T2 и переводит его в открытое состояние. Если на один из входов подан низкий потенциал, соответствующий переход база–эмиттер открывается и потенциал базы T2 оказывается близким к нулю, вследствие чего T2 запирается, а выходное напряжение соответствует состоянию H.

Рис. 5.7. Стандартный логический элемент ТТЛ И–НЕ типа 7400; потребляемая мощность PV = 10 мВт; быстродействие логического элемента tpd = 10 нс.

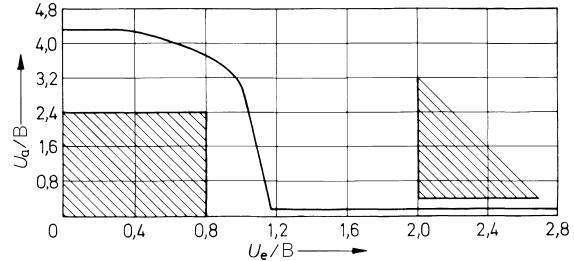

В схемах ТТЛ усилитель состоит из управляющего транзистора T2 и двухтактного оконечного каскада. Когда T2 открыт, T3 также открыт, а T4 заперт. На выходе возникает сигнал уровня L, и транзистор T3 приобретает способность пропускать большие токи, например от подключенных входов логических элементов (в состоянии L ток вытекает из этих входов!). T3 запирается вместе с T2, но при этом открывается T4, что приводит к появлению уровня H на выходе. В таком случае транзистор в режиме эмиттерного повторителя может создавать в нагрузке большие выходные токи и, следовательно, быстро заряжать емкости нагрузки. Стандартные схемы ТТЛ, подобные показанной на рис. 5.7, в настоящее время не находят применения из‑за недостаточного быстродействия, обусловленного насыщением транзисторов. Включение диода Шоттки параллельно переходу коллектор–база предотвращает насыщение транзистора. При открытом транзисторе благодаря обратной связи по напряжению диод не позволяет напряжению коллектор–эмиттер упасть ниже 0,3 В. На рис. 5.8 показан логический элемент ТТЛ, который построен из подобных «транзисторов Шоттки», представляющих собой маломощный ТТЛ элемент с диодами Шоттки. Номиналы резисторов схемы выбираются впятеро более высокоомными по сравнению со схемой стандартного логического элемента ТТЛ, благодаря чему потребляемая мощность снижается столько же раз и достигает всего 2 мВт. При этом быстродействие элемента не ухудшается, оставаясь равным 10 нс. Диодный входной логический элемент строится на раздельных диодах. Транзистор Дарлингтона T3 заменяет здесь диод D в оконечном каскаде, необходимый для смещения потенциала в стандартной схеме (см. рис. 5.7). Передаточная характеристика маломощного инвертора ТТЛ с диодом Шоттки показана на рис. 5.9. Порог переключения по входу составляет около 1,1 В, что с большим запасом перекрывает заданные допуски: при максимально допустимом уровне L на входе величиной 0,8 В выходное напряжение получается равным 2,4 В, что отвечает уровню H. При минимальном входном уровне H величиной 2,0 В выходной уровень L должен составлять не более 0,4 В.

Рис. 5.8. Маломощный логический элемент ТТЛ с диодом Шоттки типа 74LS00; потребляемая мощность PV = 2 мВт; быстродействие логического элемента tpd = 10 нс.

Рис. 5.8. Передаточная характеристика маломощного ТТЛ инвертора с диодом Шоттки (заштрихованы допустимые области) |

||

|

Последнее изменение этой страницы: 2018-04-12; просмотров: 816. stydopedya.ru не претендует на авторское право материалов, которые вылажены, но предоставляет бесплатный доступ к ним. В случае нарушения авторского права или персональных данных напишите сюда... |