Студопедия КАТЕГОРИИ: АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция |

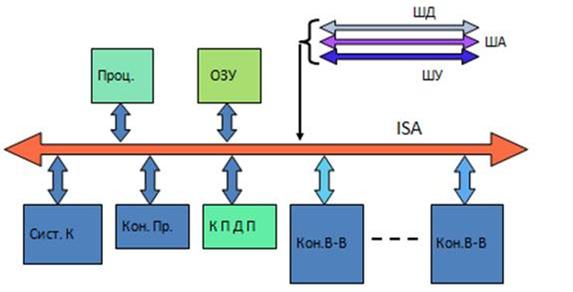

Шина ISA (Industry Standart Architekture)Архитектура шины: - однопроцессорная, трехшинная (рис. 3.12), 8(16) разрядов данных,20(24) разряда шины адреса - адресуют 1(16) Мбайт памяти; - асинхронная - роизводительность 4(16)мбайта/сек, частота 8(16)мгц; - 16 линий прерывания,7 линий ПДП; - задатчики: ЦПр, КПДП, пл.расш.; - блочной передачи нет - два адресных пространства: ОЗУ, регистры Вв/Выв.

Контроллер прерываний позволял обслуживать 16 линий запросов на прерывания

Шина PCI (Peripheral component interconnect) – шина для подключения плат расширения к материнской плате, разработанная в 1992 году компанией Intel. Также долгое время использовалась для связи северного моста с южным (рис. 3.13). Однако по мере повышения производительности плат расширения ее пропускной способности стало не хватать. Она была вытеснена более производительными шинами вначале из задач связи северного и южного моста, а потом и для связи с платами расширения . Для этой цели стали использовать более быструю шину – PCI express. Основные характеристики шины PCI: многопроцессорная; двухшинная архитектура; 32, 64 – разрядная адресация данных; синхронная шина; частота 33 МГц – 133 МГц, производительность 133 Мбайт/сек (32бит/33МГц) и 533 Мбайт/сек (64бит/66МГц) использование памяти технологий DDR и QDR(стат.память); пакетная передача данных, транзакции; арбитраж; три адресных пространства: ОЗУ, регистры ввода/вывода, регистры автоконфигурации; поддержка автоконфигурации; контроль четности. В данной шине применен усовершенствованный периферийный APIC (AdvancedPeripheral Interrupt Controller) – контроллер прерываний,подддерживающий до 255 линий прерываний (рис. 3.15). Для организации механизма Plag and Play в устройствах, подключенных к этой шине, вводится память автоконфигурации (рис 3.16). Память занимает объем 256 32 -х битных слов. После включения питания и прохода теста POST процессор по программе записанной в BIOS начинает последовательный опрос памяти конфигураций всех устройств, подключенных к шине и выделяет каждому устройству запрашиваемые ресурсы: адреса по которым можно обращаться к устройству, номер линии прерывания, диапазон адресов для внутренней оперативной и постоянной (ROM) памяти устройства (если она имеется) и др.

19.Сравнительный анализ последовательных и параллельных интерфейсов(шин). Достоинства параллельных шин: с параллельными шинами передачи данных микропроцессорам проще работать, они обеспечивают лучшую производительность при меньшей частоте. Недостатки : их сложнее использовать на высоких частотах так как при этом сильно повышаются требования к физической разводке шины, из за увеличения различия времени распространения сигнала в отдельных проводниках шины, параллельные шины занимают значительную площадь на плате. Последовательные шины. Так как себестоимость производства чипа выходит примерно одинаковой ,то дешевле делать более сложный кристалл контроллера шины, чем изготавливать многочисленные контакты и проводники параллельной шины. Поэтому с развитием технологий стали переходить на последовательные шины. Достоинства последовательных шин : - Использование различных носителей например оптических; - Экономия пространства и снижение сложности монтажа (рис 3. 17); -Проще реализовывать горячие подключения и динамическую конфигурацию устройств; - Переход от разделяемых шин с арбитражем и непредсказуемыми прерываниями, неудобными для надежных/критических систем к более предсказуемым соединениям точка-точка; - Лучшая с точки зрения затрат и более гибкая с точки зрения топологии масштабируемость;

20.Основные хар-ки шины PSI Express.Топология шины. Масштабируемость шины.Последовательно - параллельная шина общего назначения; PCI Express, на стадии проектирования была также известна как 3GIO (Ввод-вывод третьего поколения); PCI Express 1.0 - 2002годPCI Express 2.0 – 2007годPCI Express 3.0 – 2010год Фактически — сов-ть независимых самостоятельных последовательных каналов передачи данных. Стандартизированы 1, 2, 4, 8, 12,16 и 32 канальные варианты. Каждый канал состоит из двух дифференциальных сигнальных пар (необходимо только 4 контакта). Сигнальный уровень 0.8 вольт. Поддерживает систему связи «точка—точка», подобную HyperTransport AMD, а не многоточечную схему, используемую в параллельной шинной архитектуре PCI. Это устраняет потребность в шинном арбитраже, обеспечивает низкое время ожидания и упрощает «горячее» подключение-отключение устройств. Теоретическая пропускная способность (в одном направлении/в обоих направлениях) Гбайт/сек: Реальная скорость передачи данных ниже из-за необходимости передачи избыточного кода, а также различной служебной информации(пакеты подтверждения и.т.д.); Вся контрольная информация передается по тем же линиям что и данные, используется стек протоколов, из нескольких уровней, включая маршрутизацию данных; Стандарт предусматривает и альтернативные носители сигнала, такие как оптические волноводы; Возможность динамического подключения и конфигурации устройств; Прерывания организуются с помощью передачи специальных сообщений(пакетов), получателем которых, является контроллер прерываний, расположенный в главном (северном)мосту. Топология шины. Шина PCI Express - локальная сеть в пределах компьютера.Разработчики PCI Express взяли за основу новой шины наработки в области сетевого оборудования. Получилось что-то очень напоминающее GigabitEthernet с топологией многоуровневой звезды. В центре звезды находится главный мост (HostBridge) и несколько оконечных пунктов (устройств ввода-вывода), соединенных между собой с помощью специальных элементов - коммутаторов(рис 3.19), логически представляющих собой несколько виртуальных мостов PCI-PCI, соединяющих порты коммутатора со своей внутренней локальной шиной. Каждое соединение PCI Express с помощью виртуальных мостов отображается в виде логической шины PCI со своим номером. Логически устройства отображаются в конфигурационном пространстве как устройства PCI, каждое из которых может иметь 1-8 функций со своим набором конфигурационных регистров.

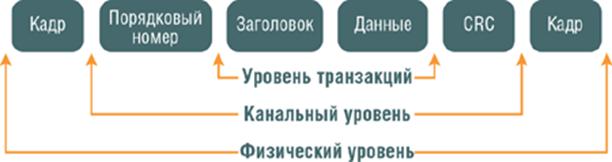

21.Многоуровневая модель шины PSI Express Назначение отдельных уровней. Формат пакетов. PCI Express использует традиционную многоуровневую модель, аналогичную сетевой модели OSI.

Для передачи или приема данных через шину PCI приложения обращаются к операционной системе. Она обслуживает инфраструктуру всех PCI-устройств, обрабатывает события — подключение устройств, присвоение им уникального адреса, нахождение подходящего драйвера для работы с конкретным устройством. Далее операционная система обращается к драйверам обслуживающим конкретные устройства PCI Express. На том уровне совместимость с PCI стопроцентная. То есть на программном уровне отличия PCI Express от PCI очень малы - обеспечена полноценная совместимость старой и новой шин. Драйвер устройства обращается в свою очередь к среде пердачи, которая состоит из трех уровней и реализуется аппаратно и кардинально отличается от реализации шины PCI. Уровень транзакций, отвечает за сборку и разборку пакетов TLP (Transaction Layer Packet - пакет уровня транзакций). Эти пакеты используются для транзакций чтения и записи, а также для сообщений о событиях некоторых типов. Этот уровень прибавляет к каждому блоку данных заголовок. Заголовок пакета, описывает тип пакета, адрес получателя, приоритет и другие свойства. Канальный уровень, промежуточный в стеке, отвечает за управление связью, обнаружение ошибок и организацию повторных передач. К пакетам, полученным от уровня транзакций, канальный уровень добавляет свои заголовки (номера пакетов, чтобы пакеты можно было отличить друг от друга и собрать в нужной последовательности и контрольные коды рис. 3.21) Физический уровень добавляет к пакету кадр. Кадр это начальная и конечная последовательность бит необходимых для распознавания начала и конца каждого пакета. После этого физический уровень осуществляет непосредственную передачу кадра рис 3.22.. Физический уровень состоит из двух субблоков. Логический субблок при передаче выполняет распределение данных по линиям, скремблирование, кодирование по схеме 8В/10В1, кадрирование и преобразование в последовательный код. При приеме выполняются обратные действия. Символы, добавляемые при кодировании 8В/10В (для стандарта PCI Express 3.0 используется кодирование 128b/130b), используются для служебной информации. Логический субблок отвечает и за согласование соединения, инициализацию и т. п. Электрический субблок отвечает за электрическое согласование, синхронизацию, обнаружение приемника. Основные поля заголовка: FMT – задает вид пакета(длину заголовка, присутствие или отсутствие в пакете поля данных) Type — тип пакета (один из четырех основных типов - Memory, I/O, Config, Message); RequestorID — получатель пакета (шина, PCI Express устройство, функция устройства); Address/Routing — адрес в памяти, куда предназначается пакет (32- или 64-разрядный) или иная информация о маршрутизации пакета; Length — объем передаваемых в пакете данных;

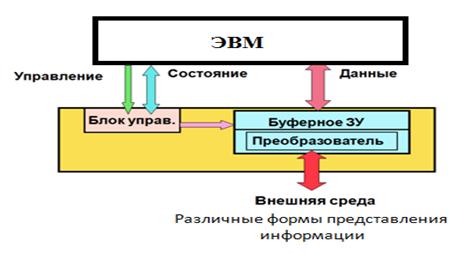

22.Определение периферийного устройства, обобщенная структура ПУ, классификация ПУ. Периферийные устройства предназначены для преобразования разнообразных форм представления информации во внешнем мире в электрические сигналы, воспринимаемые компьютером и обратного преобразования электронного представления информации в формы понятные человеку (рис. 3.25). ПУ можно разделить на категории : - устройства ввода информации - устройства вывода информации - запоминающие устройства (ВЗУ); - устройства коммуникации(например, модемы ) ПУ состоит из механической части и электронной части. Электронная часть называется контроллером и служит для управления механической частью устройства с одной стороны и связью устройства с процессором (с помощью шины ввода вывода компьютера) с другой стороны. У каждого контроллера для связи с центральным процессором имеется несколько регистров (портов). Путем записи в эти регистры операционная система может давать команды устройству на предоставление данных, на принятие данных, на его включение или выключение или на выполнение каких-нибудь других действий. Считывая данные из этих регистров, операционная система может узнать о текущем состоянии устройства, о том, готово ли оно принять новую команду, и т. д. Для согласования скоростей работы процессора и внешнего устройства оно может иметь буфер данных, из которого операционная система может считывать данные и в который она может их записывать.

23.Назначение контроллеров ПУ. Способы адресации портов контроллеров ПУ. Существует три способа адресация портов контроллеров на шине ввода - вывода. Два отдельных адресных пространства ввода – вывода и памяти . Портам ввода вывода назначаются адреса, являющиеся целым числом(например 0xСFС). Набор всех портов ввода-вывода формирует пространство портов ввода-вывода, которое защищено от доступа от обычных пользовательских программ. В этом случае команды записи и чтения для портов и ячеек памяти разные (рис 3.26а). Ввод – вывода отображаемый на пространство памяти . Порты ввода вывода отображаемые на память. Каждому порту выделен уникальный адрес в общем поле памяти, который физически не располагается в оперативной памяти. Выделяемые адреса находятся в верхней части адресного пространства. В этом случае команды записи и чтения для портов и ячеек памяти одинаковы (рис 3.26б). Гибридный вариант, в котором в устройстве внутренняя память , отображаемые на пространство памяти, и отдельные порты ввода-вывода для регистров управления. Такая архитектура используется в семействе машин Pentium (рис 3.26б).

24.Организация взаимодействия с ПУ: программный ввод/вывод ,ввод/вывод по прерыванию, прямой доступ к памяти. Для обмена данными с портами достаточно только двух ассемблерных команд микропроцессора: - in аккумулятор, номер_порта – ввод в аккумулятор из порта с номером номер порта (чтение порта); - out номер_порта, аккумулятор – вывод содержимого аккумулятора в порт (запись в порт). В Turbo Pascal и Delphi 1.0 для доступа к портам ввода/вывода используются предопределённые массивы Port и PortW. Оба массива одномерные и каждый элемент массива представляет порт с адресом соответствующим индексу элемента. Индекc имеет тип Word. Элементы массива Port имеют тип Byte, а массива PortW – Word. Port[номер_порта] := данные; – вывод данных в порт; Переменная := Port[номер_порта] ; – ввод данных из порта. Язык С Windows : Запись в порт: - оutport(номер портa, данные); -оutportb (0x3d5,0x05) Запись байта. В порт(регистр) номер 0x3d5 записывается число 0x05 Чтение порта. а= inportb(0x3d5); –чтение байта . Linux : unsigned char inb(unsigned short int port); чтение байта voidoutb(unsigned char value, unsigned short int port); запись байта в порт

25.Характеристики и принципы функционирования параллельного интерфейса(LPT порт). Параллельный порт представляет собой трехшинную архитектуру (рис.3.27). Режимы работы параллельного порта. SPP – стандартноднонаправл-й (симплексный)режим (150 Кбайт/сек). Полубайтн режим – вывод байта целиком и ввод байта за два цикла(по 4 бита). EPP (EnhancedParallelPort) – режим – двунаправленный байтовый обмен(2 Мбайт/сек). Эффективен при работе с с устройствами внешней памяти. Он позволяет подключать устройства количеством до 64 в цепочку. Для этого некоторые устройства (например, ZIP-дисковолы) имели два разъема - один на вход, другой на выход для следующего устройства. ECP (ExtendedCapabilityPort) – режим – двунаправленный с возможностью аппаратного сжатия обмен(2,5 Мбайт/сек).возможность работы в режиме DMA. Аппаратное сжатие позволяет ещё больше повысить реальную скорость передачи Эффективен для работы с принтерами и сканерами.

Получив сигнал готовности(низкий уровень)BUSY от устройства компьютер выставляет на шину данных данные и подтверждает это сигналом SТROBE. Получив сигнал SТROBE устройство снимает сигнал готовности BUSY и вырабатывает сигнал подтверждения приема ASK (3.28).

26.Характеристики и принципы функционирования последовательного интерфейса(COM порт).Интерфейс RS-485. Универсальный внешний последовательный интерфейс - СОМ-порт (Communications Port — коммуникационный порт) Этот порт обеспечивает : - Асинхронный, дуплексный интерфейс. - Скорость передачи данных может достигать 115 200 бит(бод)/с. - Максимальное расстояние между передатчиком и приемником -15м. - Компьютер может иметь до четырех последовательных портов СОМ1-СОМ4 . Порты занимают в пространстве ввода-вывода по 8 смежных 8-битных регистров каждый и могут располагаться по стандартным базовым адресам 3F8h (СОМ1), 2F8h (COM2), 3E8h (COM3), 2E8h (COM4). Порты могут вырабатывать аппаратные прерывания IRQ4 (обычно используются для СОМ1 и COM3) и IRQ3 (для COM2 и COM4). Схема соединения по интерфейсу приведена на рис3.29

В состав соединенных по RS232 устройств входят: тактовый генераторы ,которые задают тактовую частоту приемопередатчика для данной скорости связи диапазоне скоростей: 2400 … 115200 бод . Перед началом связи между двумя устройствами необходимо настроить их приемопередатчики на одинаковую скорость связи и формат кадра. Приемник, поймав падающий фронт старт-бита, который передает передатчик отсчитывает несколько тактов и следующие три такта считывает (семплирует) порт RX. Это как раз середина старт-бита. Если большинство значений семплов - "0", старт-бит считается состоявшимся, иначе приемник принимает его за шум и ждет следующего падающего фронта После удачного определения старт-бита, приемник точно также семплирует серединки битов данных и по большинству семплов считает бит "0" или "1", записывая их в сдвиговый регистр. Стоп-биты тоже семплируются (рис 3.31) Представляет интерес модификация прокола RS232 - в RS 485,которая легко получается при использовании специальных микросхем (рис. 3.33) D (driver) - передатчик; R (receiver) - приемник; DI (driverinput) - цифровой вход передатчика; Передаваемые данные RO (receiveroutput) - цифровой выход приемника; Принимаемые данные DE (driverenable) - разрешение работы передатчика; RE (receiverenable) - разрешение работы приемника A - прямой дифференциальный вход/выход; B - инверсный дифференциальный вход/выход Y - прямой дифференциальный выход (RS-4 Z - инверсный дифференциальный выход (RS-422). Интерфейс RS 485 обеспечивает: - Подключение до 32 приёмопередатчиков в одном сегменте сети (рис. 3. 34). - Максимальная длина одного сегмента сети: 1200 метров. -Только один передатчик активный. - Максимальное количество узлов в сети — 256 с учётом магистральных усилителей. - Скорость обмена/длина линии связи: 62,5 кбит/с 1200 м (одна витая пара), 375 кбит/с 500 м (одна витая пара),10000 кбит/с - 10 м. Дифференциальная передача данных. По одному проводу (условно A) идет оригинальный сигнал, а по другому (условно B) - его инверсная копия. Высокая помехозащищенность |

||||||

|

Последнее изменение этой страницы: 2018-04-12; просмотров: 757. stydopedya.ru не претендует на авторское право материалов, которые вылажены, но предоставляет бесплатный доступ к ним. В случае нарушения авторского права или персональных данных напишите сюда... |