Студопедия КАТЕГОРИИ: АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция |

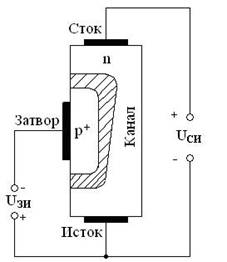

Уровень операционной системы.Стр 1 из 10Следующая ⇒ Биполярный транзистор. Транз-р сод-т в себе 2 p-n-перехода и им 3 вывода: базу, эмиттер и коллектор. Если подать на выводы напряж-е (р.1.10) оба перехода изначально включены в обратннаправл-и и ток не пройдет при люб напряж-и на колл-р-эмиттере. Если подать на базу напряж-е, то запретн слой перехода база-эмиттер сужается и ч/з него начинает течь ток. Под действием эмиттерного тока электроны устремятся из эмиттера с проводимостью n в базу с проводимостью p. При этом часть электронов заполнят дырки, находящиеся в области базы и ч/з базовый вывод протекает незначительн ток, - ток базы Iб. База тонкая и дырок в ней немного. Остальн электроны, кот-м не хватило дырок в тонк базе, устремляются в коллектор и извлекаются оттуда более высоким потенциалом коллектор-эмиттер Eкэ. Под воздействием этого напряж-я электроны преодолеют 2-й потенциальн барьер (переход) и ч/з источник питания вернутся в эмиттер. Т.о., небольшоенапряж-е, приложенное к переходу база–эмиттер, способствует открыванию перехода база – коллектор, смещенному в обратном направлении. Такое включ-е позволяет управлять большим током коллектора с помощью маленького тока базы. Токи связаны м/у собой соотнош-ем:IК = β*IБ,где β - статический коэфф-т передачи. Биполярнтранз-ры бывают 2 типов p-n-p и n-p-n Полевые транзисторы. Каналом полевого транз-раназ-ют область в полупроводнике, в кот-й ток основн носителей заряда регулир-сяизмен-ем ее поперечного сечения. Электрод (вывод), ч/з кот-й в канал входят основн носители заряда, - исток. Электрод, ч/з кот-й из канала уходят основн носители заряда, - сток. Электрод, служащий для регулир-я поперечного сечения канала за счет управляющего напряж-я, - затвор.  При измен-и напряж-е затвор-исток измен-ся ширина проводящего канала. При этом затвор изолирован от канала, поэтому входной ток затвора стремится к нулю. Поэтому полевыетранз-ры в отличие от биполярных управляются не током, а напряж-ем.

В завис-ти как изолирован затвор от канала бывают транзисторы, у кот-х затвор изолирован p-n переходом, изолирован диэлектриком - МДП-транзисторы и МОП (MOSFET) – транзисторы, у кот-х затвор изолирован от канала окислом Транзисторы могут работать в 2 основных режимах линейном и ключевом. В ключевом режиме мощность рассеиваемая на транзисторе меньше чем линейном. Так как P=I2*R, то при открытом транзисторе R стремится к нулю и рассеиваемая мощность стремится к нулю. В закрытом состоянии ток стремится к нулю и мощность также стремится к нулю. Операционный усилитель. Усиливает только разность входныхнапряж-й.Коэфф-т усиления при разомкнутой цепи обратной связи стремится к бесконечности,имеет выс входное сопротивл-е.

Различают 2 основных схемы включения операционных усилителей: инвертирующее и не инвертирующее включение. Коэффициент усиления в этом включении определяется по формуле: При инвертирующем включении сигнал на выходе имеет противоположную полярность относительно входного сигнала. Коэффициент усиления в этом включении определяется по формуле: 2. Базовое логические функции цифровой техники. Все цифровые устр-ва строятся с помощью 5 основных логических ф-й, кот-е в свою очередь аппаратнореализ-ся с помощью биполярных и в особ-ти полевых транзисторов.

Комбинационной логикой (комбинационной схемой) называют двоичную логику функционирования устройств комбинационного типа у которых состояние выхода однозначно определяется набором входных сигналов. Это отличает комбинационную логику от логики с памятью, в которой выходное значение зависит не только от текущего состояния входных сигналов, но и от предыстории функционирования цифрового устройства (от предыдущих состояний). Эта логика предполагает наличие памяти, которая в комбинационной логике не предусмотрена. Основные узлы комбинационного типа: шифраторы, дешифраторы, мультиплексоры, цифровые компараторы. Шифратор (кодер) преобразует единичный сигнал на одном из входов в n-разрядный двоичный код. Наибольшее применение он находит в устройствах ввода информации (пультах управления) для преобразования десятичных чисел в двоичную систему счисления. Предположим, на пульте десять клавиш с гравировкой от 0 до 9. При нажатии любой из них на вход шифратора подается единичный сигнал (Х0, ..., Х9). На выходе шифратора должен появиться двоичный код (Y0, ..., Y9) этого десятичного числа. Как видно из таблицы истинности, в этом случае нужен преобразователь с десятью входами и четырьмя выходами.

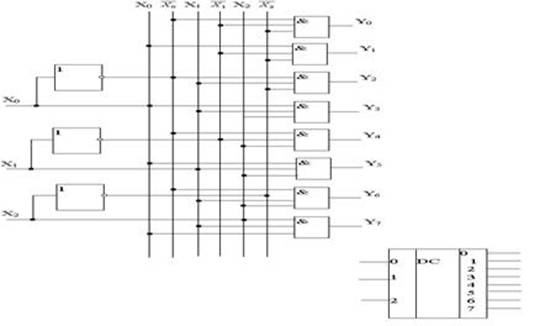

Дешифратор (декодер) - это узел, преобразующий код, поступающий на его входы, в сигнал только на одном из его выходов. Дешифраторы широко применяются в устройствах управления, для построения распределителей импульсов по различным цепям и т.д. Дешифратор двоичного n-разрядного кода имеет 2n выходов, т.к. каждому из 2nзначений входного кода должен соответствовать единичный сигнал на одном из выходов дешифратора.

Цифровой мультиплексор пропускает(коммутирует) сигнал с одного из входов на один выход.

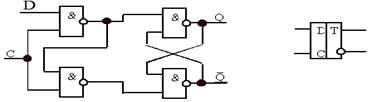

Цифровой компаратор сравнивает два двоичных числа 3. Элементы цифровой техники с памятью: триггер, регистр, счетчик – структура и принципы работы. Узлы последовательного типа это узлы с памятью, в кот-х выходнзнач-е зависит не только от тек сост-я входнсигн-в, но и от предыстории функционир-я цифрового устройства(от предыдущих состояний). RS-триггер – устр-во с 2устойчивымисост-ями, имеющ2информац-х входа R и S. Воздействие на вход Set приводит триггер в единичнсост-е, а воздействие на Reset - в нулевсост-е. Одновременн подача сигн-в на оба входа запрещена.При снятии входнсигн-в выходн сигналы измен-ся.

D-триггер. Когда на вход С подан логический 0, триггер хранит инф-ю. Если на вход С подать логическую 1, то триггер записывает знач-е с информационного входа D.

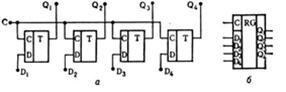

Регистры. Если объед-тьнеск-ко триггеров в группу можно получить эл-т хранящий группу неск-ко двоичн разрядов. Такой эл-т наз-ся регистром. Двоичные данные могут записыв-ся в регистр параллельнои(или) последоват-но (побитно).Рег-ры содержат специальн входы для сдвига инф-и в нем. Некот-е регистры имеют выходы с 3сост-ями (0,1 и высокоимпеданснсост-е). Наличие 3-госост-я позволяет объединять выходы регистров м/у собой, образовывая т. о. схему "монтажного ИЛИ". Это св-во позволяет подсоед-ть выходы неск-х устр-в к одной общей шине связи для передачи инф-и м/у ними. Когда 2устр-вапередают друг другу инф-ю остальные переводят свои выходн каскады в 3сост-е и отключ-ся от линии. Рег-рымбобъединены между собой последовательно, образуя цепочку. Двоичные счетчики. Двоичные счетчики служат для подсчета двоичных импульсов. Они имеют счетный вход Т и параллельные выходы, а также выход переноса, кот-й позволяет соединять счетчики м/у собой для наращивания коэфф-та пересчета. По фронту очередного тактируемого импульса счетчики меняют свое сост-е.

4. Аналоговое кодирование дискретных данных и цифровое кодирование дискретных данных. Физическое кодирование данных.В природе сущ-ет два типа сигналов:- аналоговые(непрерывные); - цифровые(дискретные) . Физическое кодирование – сп-бы представл-я данных в виде электрич-х, оптич-х или радиоимпульсов. Для представл-я цифр-х двоичных данных используют 2 типа физ-го кодир-я дискретных данных:- аналоговое;- цифровое. С помощью аналогового кодирования дискретные данные представляются в виде амплитуды, частоты или фазы аналогового сигнала.

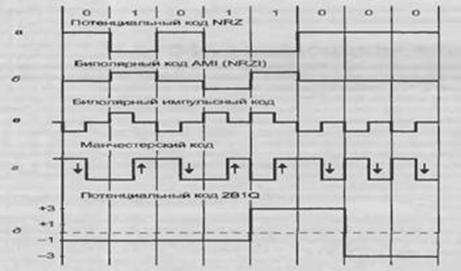

Амплитудная модуляция (АМ, AM – AmplitudeModulation) единица и ноль представляются разными амплитудами аналогового сигнала; Частотная модуляция (ЧМ, FM – FrequencyModulation) единица и ноль представляются разными частотами аналогового сигнала; Фазовая модуляция (ФМ, PM – PhaseModulation) единица и ноль представляются разными фазами аналогового сигнала; Используется в аналоговых модемах и беспроводных сетях Цифровое кодирование делится на: -Потенциальное (главн пар-ром явл-сяур-ньнапряж-я - потенциал сигнала); -Импульсное(в импульсных кодах данные кодируются или полярностью импульса или же его частью – фронтом)

Потенциальные коды: - NRZ - Без возврата к нулю (non-return-to-zero ) - для передачи единиц и нулей используются два устойчивых состояния 0 и 1; - NRZI – инвертированный (Non-return-to-zeroinverted)-смена сигнала происходит при передаче 1, а передача 0 не приводит к измен-ю напряжения. Импульсный код - манчестерский код. Используется фронт импульса. 1 кодируется переходом от низкого потенциала в высокий (передний фронт), а логичекий0 переходом от высокого потенциала к низкому (задний фронт). Используется в сетях Ethernet 10 мбит/сек Потенциальные коды «передаются» быстрее, но при их использ-и особоезнач-е приобретает задача синхронизации приемника с передатчиком, так как при передаче длинных последовательностей 0 или 1 сигнал на входе приемника не изменяется и приемнику сложно определить момент съема очередного бита данных. По этой причине потенциальные коды требуют дополнительной корректировки (избыточноекодиров-е, скрэмблирование). Избыточное кодир-е - введение избыточных битов в исходнданн (например коды типа 4В/5В когда 4 бита исходного кода кодируются 5 битами. Скрэмблирование - это обратимое преобразов-е исходного цифрового потока без измен-я скорости передачи (с целью получ-я св-в случайной последовательности.). После скремблирования появление «1» и «0» в выходной последовательности равновероятны. Потенциальные избыточные и скэмблированные коды используются в сетях FastEthernet, GigabitEthernet. 5. Аналого-цифровые и цифро-аналоговые преобразователи. Аналого-цифровые преобразователи (АЦП) предназн-ны для преобразов-я аналоговой величины в цифров код. Это устр-ва, кот-е принимают аналоговые сигналы и генерируют соотв им цифровые (дискретные) коды. Дискретизация - это преобразов-е непрерывной ф-и (аналогового сигнала) в виде ряда последоват-ти дискретных отсчетов. Промежутки времени между отсчетами Δt– частота дискретизации.

Теорема Котельникова - частота дискретизации должна быть вдвое больше максимальной частоты сигнала. Основными характер-ками АЦП явл-ся разрядность представл-я двоичных данных (10,12, 14, 24 бита) и время дискретизации (разрядность и Δt). Аналоговое входное напряж-е Uвх подается на вход аналоговых компараторов и сравнив-ся с набором опорных напряж-й, снимаемых с делителя. На выходе компаратора, где входное напряж-е больше соотв опорного, будет лог. 1, на остальных - лог. 0. Шифратор предназначен для преобразования полученной группы нулей и единиц в двоичный код.

Цифроаналоговый преобразователь (ЦАП)предназн-н для преобразов-я цифрового кода (сигнала) в аналоговый. Принцип работы ЦАП заключ-ся в суммир-и аналоговых сигн-в (ток или напряж-е). Суммир-е производится с коэфф-тами, равными 0 или 1 в завис-ти от знач-я соотв разряда кода. Основн характер-ки – разрядность, частота дискретизации. Пример использования АЦП - для контроля питающих напряжений компьютерного блока питания. С помощью АЦП уровни питающих аналоговых сигналов преобразуются в цифровые коды и записываются в регистр, после чего они поступают в процессор для обработки.

6. Принстонская (фон Неймана)и Гарвардская архитектуры компьютера. Их сравнительный анализ. Джон фонНе́йман изложил основн принципы построения и арх-ру ЭВМ. Изложенные принципы лежат в основе построения больш-ва современных ЭВМ. Принципы фон Неймана: 1. Принцип программногоуправл-я. Прогр-ма состоит из набора команд, кот-евып-ся процессором друг за другом в определенной последовательности. 2. Принцип однородности памяти. Как программы (команды), так и данные хранятся в одной и той же памяти (и кодируются в одной и той же системе счисления - лучше всего в двоичной). Над командами можно выполнять такие же действия, как и над данными. 3. Принцип адресуемости памяти. Структурно основная память состоит из пронумерованных ячеек; процессору в произвольный момент времени доступна любая ячейка.

ГорвардомЭйкеном была предложена гарвардская арх-ра ЭВМ, отличительными признаками которой являются: 1. Коды команд и данные хранятся на разных физ-х устр-вах памяти.

Сравнительный анализ архитектур. Достоинства гарвардской архитектуры следующие: - Применение небольшой по объему памяти данных способствует ускорению поиска информации в памяти и увеличивает быстродействие МП. - Гарвардская архитектура позволяет организовать параллельное выполнение программ – выборка следующей команды может происходить одновременно с выполнением предыдущей в результате чего сокращается время выборки команды. Недостатком гарвардской архитектуры является усложнение архитектуры МП и необходимость генерации дополнительных управляющих сигналов для памяти команд и памяти данных. Основное преимущество архитектуры Фон-Неймана – упрощение устройства МП, так как реализуется обращение только к одной общей памяти. Кроме того, использование единой области памяти позволяло оперативно перераспределять ресурсы между областями программ и данных, что существенно повышало гибкость МП с точки зрения разработчика программного обеспечения. Размещение стека в общей памяти облегчало доступ к его содержимому. Неслучайно поэтомуфон-неймановская архитектура стала основной архитектурой универсальных компьютеров, включая персональные компьютеры.

7. Назначение отдельных уровней 6-уровневой модели компьютера. В общем случае компьютер можно представить в виде шести уровней (рис.2.11).

Цифровой логический уровень. На 0-мур-не располаг-ся цифровые микросхемы реализованные с помощью 5 базовых логических ф-й (кот-е в свою очередь реализованы на транз-х). Уровень микропрогр-м. Каждая машинная команда, ур-ня машинных команд для своего выполн-я на цифровлогическур-не требует выполн-я элементарн опер-й управляющих аппаратными устр-вами процессора. Поэтому каждая машинная команда разбивается уровнем микрокоманд на последоват-сть элементарных опер-й (микрокоманд). Эта последоват-стьмбреализована с помощью микропрогр-мы зашитой в управляющую память микропрогр-м процессора или реализована аппаратно с помощью цифровых комбинационных схем(> быстрый метод, но требует больших аппаратных затрат.) Уровень машинных команд.При поставке производители процессоров поставляют набор машинных команд, кот-е он может выполнять. Ур-ньмашинн команд — это тот ур-нь, на кот-м комп-р представляется прогр-сту, пишущемупрогр-мы на машинн языке. Поскольку сейчас ни один нормальный прогр-ст таких прогр-м не пишет, то прогр-маур-ня машинн команд — это то, что получ-ся в рез-те работы компил-ра. Чтобы получить прогр-муур-ня машинных команд, создатель компилятора должен знать, какая модель памяти использ-ся в машине, какие регистры, типы данных и команды имеются в наличии, и т. д. Вся эта инф-я в совок-сти и определяет ур-нь машинных команд. Уровень операционной системы. С т зрпрогр-ста, ОС — это прогр-ма, добавляющая ряд команд и ф-й к командам и ф-ям, предлагаемым ур-нем машинн команд. Все команды ур-няОС доступны для прикладных прогр-стов. Это — практически все машинные команды более низкогоур-ня, а также новые команды, добавленные ОС. Новые команды называются системными вызовами. Они вызывают предопределеную службу операционной системы. Каждый системный вызов операционной системы в итоге выполняются с помощью последовательности машинных команд.

Уровень ассемблера Язык, на котором изначально была написана программа, называется входным, или исходным, языком, а язык, на который она транслируется, — выходным, или целевым. Трансляторы можно разделить на две группы в зависимости от отношения между входным и выходным языками. Если входной язык является символическим представлением числового машинного языка, то транслятор называется ассемблером, а входной язык — языком ассемблера, или просто ассемблером. Если входной язык является языком высокого уровня (например, Java или С), а выходной язык является либо числовым машинным языком, либо символическим представлением последнего, то транслятор называется компилятором.

8. Обобщенная структура, назначение регистров и принципы функционирования 8 разрядного микропроцессора. Обобщенная архитектура 8 разрядного микропроцессора

Арифметико – логическоеустр-во (АЛУ) вып-етобраб-ку данных. Типичными опер-ями, выполняемыми АЛУ явл-сяслож-е, инвертиров-е, сдвиг, а также опер-и инкремента и декремента. АЛУ содержит 2входных порта и 1 выходной порт. Порты снабжены буферами, роль кот-х вып-ют регистры временногохран-я данных – буферные регистры. Необх-ть в таких регистрах вызванаотс-ем в АЛУ своего запоминающего устр-ва. В состав АЛУ включены только комбинационные схемы и поэтому при поступл-и исходных данных на входы АЛУ немедленно появл-ся рез-т на его выходе. Рез-т сущ-ет на выходе комбинационной схемы до тех пор пока сущ-ют данные на её входе. Рез-т помещается вспецбуферн регистр –аккум-р.Работа АЛУ без регистров временн хранения данных невозможна. Аккум-р – главный регистр МП при разл-х манипуляциях с данными. Рез-т опер-и АЛУ размещается в аккум-ре. При этом исходное содержимое аккум-ра теряется. Для выполн-я любой опер-и над данными прежде всего их необх-мо поместить в аккум-р. На пути прохождения данных из аккум-ра в АЛУ находится буфер аккум-ра. Большинство арифметических и логических операций осуществляется путём использования АЛУ и аккумулятора. Счетчик команд (ProgramCounter (РС) - программный счётчик) Для корректноговыполн-я прогр-мы её команды должны поступать в строго определённом порядке. Счетчик команд следит за тем, какая команда вып-ся, а какая подлежит выполн-ю след-й. После извлеч-я команды из памяти МП автомат-ски даёт приращение содержимому счетчика команд. Это приращ-е СК получает как раз в тот момент, когда МП начинает выполнять команду, только что извлеченную из памяти. С этого момента СК указ-ет, какой будет след команда. СК содержит адрес след-ей выполняемой команды на протяж-и всего времени выполн-я тек команды. Перед вып-ем прогр-мы СК загружается адресом ячейки памяти, содержащей 1-ю команду программы. Регистр адреса памяти. При каждом обращении к памяти ЭВМ регистр адреса памяти указывает (содержит) адрес ячейки памяти, которая подлежит использованию МП. Регистр адреса памяти содержит двоичное число – адрес области памяти. Выход этого регистра называется адресной шиной. Регистр команд. В ходе извлеч-я команды из памяти её 1-й байт (КОП) передаётся в регистр команд. Содержимое регистра доступно дешифратору команд. Регистр команд предназначен исключительно для хран-я тек-й выполняемой команды. Регистр команд соединён с внутренней шиной данных, однако он может только принимать данные – посылать данные на шину он не может. При извлеч-и команды из области памяти копия команды помещается на внутр шину данных и пересылается в регистр команд. Далее дешифратор команд считывает содержимое регистра команд, сообщая МП что делать для реализации операций команды. Регистр состояния (Слово состояния программы PSW) Данный регистр предназн-н для хран-я рез-в некот-х проверок сост-я аккум-ра, осуществл-х в проц-се выполн-я прогр-мы. Регистр сост-я сод-т одноразрядные биты индикаторы, содержимое этих индикат-в использ-ся для условноговетвл-я программ. Этот регистр ещё называют регистром признаков или словом сост-я прогр-мы. В этом регистре находятся также биты управления приоритетом ЦП. Указатель стека(SP) представляет регистр, кот-й сод-т адрес последнего помещенного в стек байта. Указатель стека декрементируется при каждом помещении в стек и инкрементируется при каждом извлечении из него. Регистры общего назн-я (РОН) служат в кач-ве запоминающих устр-в, это позволяет повысить быстродействие микро-ЭВМ за счет сокращ-я пересылок кодов м/у МП и памятью. РОН представляет собой сверхоперативную память МП. Схема управл-я (микропрогр-гоуправл-я). Схема управл-я состоит из дешифр-ра команд и устр-вауправл-я и синхрониз-и. Одна из главн ф-й схемы управл-я – декодиров-е команды. Для этого служит дешифр-р команд. Он анализ-ет отдельные биты команды находящиеся в регистре команд и передаёт код опер-и в устр-во управл-я. Основу устр-вауправл-я составляет управляющ память микропрогр-м. Каждой машинн команде соотв-етопределенн микропрогр-ма зашитая в ПЗУ. Для повыш-я быстродействия микропрогр-е управл-е мб в виде комбинац-й схемы на программируемых логических матрицах(ПЛМ). Устр-во управл-я получает сигналы от дешифр-ра команд для определ-я природы выполняемой команды. Устр-во управл-я получает также инф-ю от регистра сост-я в случае условного перехода. Сигналы управл-я и синхрониз-и передаются во все блоки МП для координации выполне-я команд и управл-я внешними устр-вами (ОЗУ, ПЗУ, УВВ). Работа процессора. Программн счётчик выдаёт адрес команды на шину адреса. Память помещает команду, находящуюся по этому адресу на шину данных. Проц-р вводит команду в свой регистр команды. Там команда дешифр-ся, определ-ся код опер-и, определ-ся длина команды в байтах. Если команда использует слово из памяти, определяет, где нах-ся это слово. Проц-р переносит слово, если это необх-мо, в регистр центральнпроц-ра. Сама команда после её обработки регистром команды, вып-ся остальными устр-вами процессора. Программн счётчик адресует след команду, находящуюся по адресу на длину команды от предыдущей. Когда выполнение текущей команды завершается содержимое программного счётчика помещается на шину адреса и цикл повторяется. 9. CISC и RISC архитектуры микропроцессоров и их сравнительный анализ. В настоящее время существуют две основных архитектуры процессоров CISC и RISC CISC (ComplexInstructionSetComputer) - архитектура реализована во многих типах микропроцессоров, выполняющих большой набор разноформатных команд с использованием многочисленных способов адресации. Они выполняют более 200 команд разной степени сложности, которые имеют размер от 1 до 15 байт и обеспечивают более 10 различных способов адресации. Такое большое многообразие выполняемых команд и способов адресации позволяет программисту реализовать наиболее эффективные алгоритмы решения различных задач. CISC— компьютер это компьютер с полным набором сложных команд выполняющихся за несколько тактов RISC (ReducedInstructionSetComputer) - архитектура отличается использованием ограниченного набора простых команд фиксированного формата. Современные RISC-процессоры обычно реализуют около 100 команд, имеющих фиксированный формат длиной 4 байта. Также значительно сокращается число используемых способов адресации. Обычно в RISC-процессорах все команды обработки данных выполняются только с регистровой или непосредственной адресацией. RISC - компьютер это компьютер с сокращенным набором простых команд выполняющихся за один такт. Существуют гибридные варианты. Так, процессоры Intel, начиная с процессора 486, содержат RISC-ядро, которое выполняет самые простые (и обычно самые распространенные) команды за один цикл, а по обычной технологии CISC выполняются более сложные команды. В результате обычные команды выполняются быстро, а более сложные и редкие - медленно.

10.Взаимодействие процессоров(ядер) между собой и оперативной памятью.SMP,NUMA,кластерные системы. Когда повыш-е частоты работы процессора столкнулось с технологич-м пределом возникла идея вместо повыш-я частоты увелич-ть кол-во ядер проц-ра. При этом независимые процессорн ядра стали изготавл-ся по 2 вариантам: - каждое со своей кэш-памятью, расположенной на одном кристалле. - неск-ко одинак-х ядер расположены на разных кристаллах, но объед-ны вместе с одном корпусе проц-ра (например, многочиповый процессор на ядре Presler) Для повыш-я производительности работы процессоров стали использовать кэш Идея кэша состоит в том, что когда определенн слово вызывается из памяти, оно вместе с соседними словами переносится в кэш-память, что позволяет при очередн запросе быстро обращаться кслед словам уже находящимися в кэше По способам взаимодействия ядер(процессоров) между собой и с оперативной памятью различают три архитектуры: - SMP-системы (SymmetricalMultiProcessorsystems). – симетричныемультипроцессорныые системы; - NUMA-системы (Non-UniformMemoryAccesssystems) Архитектура с неравномерной памятью время доступа к памяти определяется её расположением по отношению к процессору. - Кластерные системы SMP-системы. Процессоры имеют равноправный доступ к общей оперативной памяти (рис. 2.7). Достоинство - хорошо подходит для многопоточных приложений. Недостатки -сложная аппаратная реализация (наличие общих линий обращения к памяти). Снижение производительности с ростом количества ядер(процессоров)

В NUMA-системах время доступа к памяти определяется её расположением по отношению к процессору (2.8). Память становится «неоднородной». Обращения к «своей» памяти происходят быстро, к «чужой» - медленнее, причем чем «дальше» чужая память расположена, тем медленнее получается доступ к ней. Достоинство - проще аппаратная реализация чем у SMP систем . Недостатки сложно написать эффективную программу без учета неоднородности памяти. Противоречие с принципами Фон–Немана так ка память становится не однородной.

Кластеры. В таких системах самостоятельные узлы (компьютеры) объединенны быстродействующими линиями связи. У каждого узла своя память. Достоинство - низкая стоимость. Недостаток - сложно программировать.

Intel предпочитает создавать SMP-системы (рис. 2.10), AMD, IBM и Sun – различные варианты NUMA - систем(2.11). Кластерные системы используются для создания суперкомпьютеров. Способы связи между ядрами (процессорами): - разделяемая шина; -сеть с коммутатором- общая кэш - память.

Весь этот комплект объединяется в единое целое специальным коммуникационным процессором – «северным мостом» (Northbridge) чипсета. |

||

|

Последнее изменение этой страницы: 2018-04-12; просмотров: 913. stydopedya.ru не претендует на авторское право материалов, которые вылажены, но предоставляет бесплатный доступ к ним. В случае нарушения авторского права или персональных данных напишите сюда... |

. Широко используются в линиях передачи сигналов в качестве приемо-передатчиков. Например, во входных каскадах провода витой пары для локальных сетей.

. Широко используются в линиях передачи сигналов в качестве приемо-передатчиков. Например, во входных каскадах провода витой пары для локальных сетей.

Базовые логические функции и их реализация

Базовые логические функции и их реализация

.

.