Студопедия КАТЕГОРИИ: АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция |

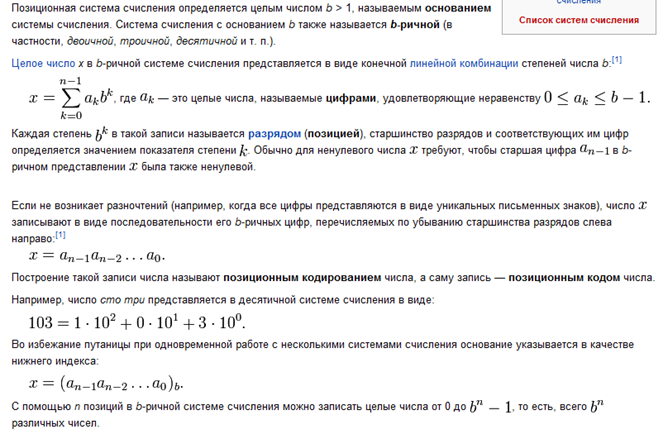

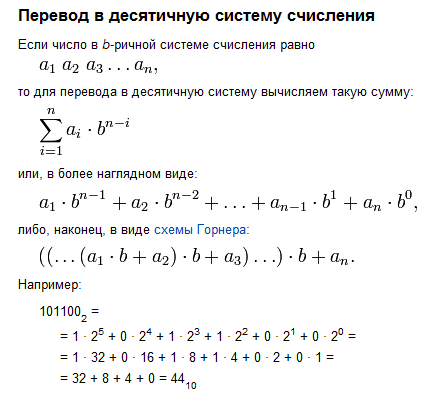

Схемотехническая реализация.Стр 1 из 18Следующая ⇒ ЭКЗАМЕНАЦИОННЫЙ БИЛЕТ № 1 1. Дайте определение понятий «алфавит системы счисления», «основание системы счисления». Приведите общую форму для представления чисел в позиционной системе счисления. Опишите процесс перевода чисел из системы счисления с основанием q, где q ≠ 10, в систему счисления с основанием q=10. Приведите примеры.

В позиционных системах счисления вес каждой цифры изменяется в зависимости от ее положения (позиции) в последовательности цифр, изображающих число. Позиционную систему счисления характеризуют три основные понятия - алфавит, основание, базис.

Алфавит – набор символов, образующих числа в данной системе счисления. Основание – количество символов в алфавите. Базис – вес разрядов.

Наиболее распространенная, широко используемая и хорошо каждому из нас известная ПСС – десятичная.

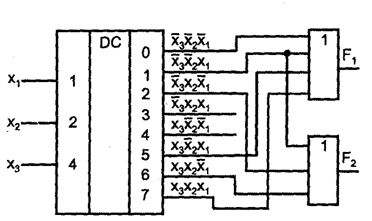

2. Двоичные дешифраторы. Назначение. Схемная реализация. Описание функционирования. Схемотехническая реализация. Наращивание размерности. Схема воспроизведения произвольных логических функций с помощью дешифратора.

Дешифратор – преобразователь кода, а конкретно двоичный дешифратор – преобразовывает двоичный код в код 1 из N. Двоичный дешифратор, имеющий n входов, должен иметь 2n выходов, соответствующих числу разных комбинаций в n-разрядном двоичном коде. В зависимости от входного двоичного кода на выходе дешифратора возбуждается одна и только одна из выходных цепей. Если часть входных наборов не используется, то дешифратор называют неполным, и у него число выходов меньше 2n. Схемная реализация:

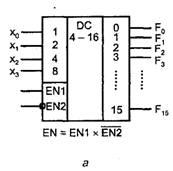

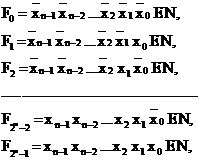

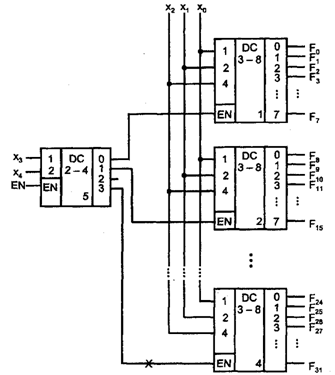

В условном обозначении дешифраторов проставляются буквы DC. Входы дешифратора принято обозначать их двоичными весами. Кроме информационных входов дешифратор обычно имеет один или более входов разрешения работы обозначаемых как EN. При наличии разрешения по этому входу дешифратор работает описанным выше образом, при его отсутствии все выходы дешифратора пассивны. Если входов разрешения несколько, то сигнал разрешения работы образуется как конъюнкция сигналов отдельных входов. Часто дешифратор имеет инверсные выходы. В этом случае только один выход имеет нулевое значение, а все остальные единичное. При запрещении работы дешифратора на всех его выходах будет присутствовать логическая единица. Функционирование дешифратора описывается системой конъюнкций:

Схемотехническая реализация. Как известно, корпуса ИС с большим числом выводов изготовлять сложно, и они дороги. С этой точки зрения дешифраторы относятся к крайне неудачным схемам, т. к. у них при простой внутренней структуре и малом числе схемных элементов много внешних выводов. Для размещения в обычном недорогом корпусе годится только дешифратор с 4 информационными входами. Более "размерных" дешифраторов в сериях ИС нет. Наращивание размерности: Малоразрядность стандартных дешифраторов ставит вопрос о наращивании их разрядности. Из малоразрядных дешифраторов можно построить схему, эквивалентную дешифратору большей разрядности. Для этого входное слово делится на поля. Разрядность поля младших разрядов соответствует числу входов имеющихся дешифраторов. Оставшееся поле старших разрядов служит для получения сигналов разрешения работы одного из дешифраторов, декодирующих поле младших разрядов.

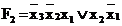

В качестве примера на рис. приведена схема дешифрации пятиразрядного двоичного кода с помощью дешифраторов "3-8" и "2-4". Для получения нужных 32 выходов составляется столбец из четырех дешифраторов "3-8". Дешифратор "2-4" принимает два старших разряда входного кода. Возбужденный единичный выход этого дешифратора отпирает один из дешифраторов столбца по его входу разрешения. Выбранный дешифратор столбца расшифровывает три младших разряда входного слова. Каждому входному слову соответствует возбуждение только одного выхода. Например, при дешифрации слова х4х3х2х1х0= 110012 = 2510 на входе дешифратора первого яруса имеется код 11, возбуждающий его выход номер три (показано крестиком), что разрешает работу DC4. На входе DC4 действует код 001, поэтому единица появится на его первом выходе, т. е. на 25 выходе схемы в целом, что и требуется. Схема воспроизведения произвольных логических функций с помощью дешифратора. Дешифраторы совместно со схемами ИЛИ можно использовать для воспроизведения произвольных логических функций. Собирая нужные термы по схеме ИЛИ, можно получить любую функцию данного числа аргументов. На рис. в качестве примера показана схема выработки двух функций

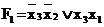

Для проверки правильности схемы удобно перевести функции F1 и F2 в СДНФ.

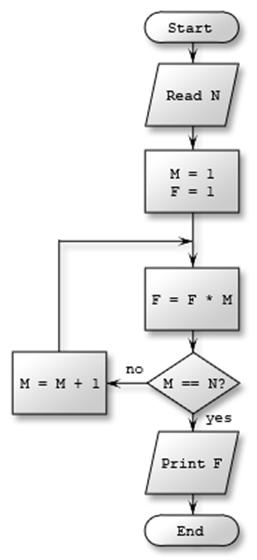

3. Понятие алгоритма. Свойства, способы описания. Дать понятие алгоритма. Описать виды алгоритмов, их свойства, способы описания. Продемонстрировать графическую форму представления алгоритма – блок-схему.

Алгори́тм —набор инструкций, описывающих порядок действий исполнителя для достижения результата решения задачи за конечное время. Неформальное определение Каждый алгоритм предполагает существование начальных (входящих) данных и в результате работы приводит к получению определенного результата. Работа каждого алгоритма происходит путем выполнения последовательности некоторых элементарных действий. Эти действия называют шагами, а процесс их выполнения называют алгоритмическим процессом. Таким образом проявляется свойство дискретности алгоритма. Важным свойством алгоритмов является массовость, или возможность применения к различным входным данным. То есть, каждый алгоритм призван решать класс однотипных задач. Необходимым условием, которому удовлетворяет алгоритм, является детерминированность, или определенность. Это означает, что выполнение команд алгоритма происходит по единому образцу и приводит к одинаковому результату для одинаковых входных данных. Входные данные алгоритма могут быть ограничены набором допустимых входных данных. Применение алгоритма к недопустимым входным данным может приводить к тому, что алгоритм никогда не остановится или попадет в тупиковое состояние (зависание), из которого не сможет выйти. Виды алгоритмов прикладные алгоритмы - предназначенные для решения определённых прикладных задач. Алгоритм считается правильным, если он отвечает требованиям задачи (например, даёт физически правдоподобный результат). Алгоритм (программа) содержит ошибки, если для некоторых исходных данных он даёт неправильные результаты, сбои, отказы или не даёт никаких результатов вообще. рекурсивные алгоритмы - алгоритмы, вызывающие сами себя до тех пор, пока не будет достигнуто некоторое условие возвращения Параллельный алгоритм -противопоставляемый традиционным последовательным алгоритмам, — алгоритм, который может быть реализован по частям на множестве различных вычислительных устройств с последующим объединением полученных результатов и получением корректного результата.

ЭКЗАМЕНАЦИОННЫЙ БИЛЕТ № 2 1. Дайте характеристику позиционных систем счисления, используемых в ЭВМ (основание, алфавит). Постройте таблицы сложения и умножения для систем счисления с основаниями q=2 и q=8. Приведите примеры выполнения арифметических действия в позиционных системах счисления с основанием q=2 ( *, /, +, - ); q=8 ( *, /, +, - ); q=16 (+, - ).

|

|||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2018-04-12; просмотров: 548. stydopedya.ru не претендует на авторское право материалов, которые вылажены, но предоставляет бесплатный доступ к ним. В случае нарушения авторского права или персональных данных напишите сюда... |

и

и  .

.