Студопедия КАТЕГОРИИ: АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция |

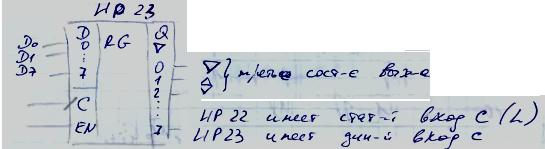

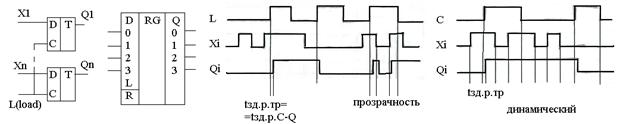

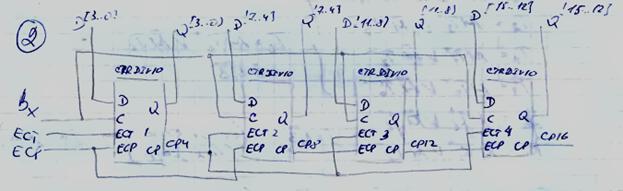

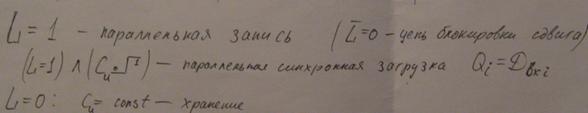

Наращивание разрядности регистров и счетчиков.⇐ ПредыдущаяСтр 18 из 18 Наращивание рег-ов - наращивание разрядности. НАРАЩИВАНИЕ ПАРАЛЛЕЛЬНЫХ РЕГИСТРОВ. Регистры памяти (параллельные регистры).Запись, хранение, выдача информации. Для временного хранения информации в течении 1 или нескольких циклов работы устройства. Чаще всего с однофазным вводом на основе D-триггеров (как со статическим, так и с динамическим управлением записью). Инф-ые входы рег-а используют для вводв опер-ов. По вх. синхр-ии отдельные рег-ы объединяются К555ИР22 К555ИР23

С динамическим управлением записью. Данные триггера непрозрачны. Вход R установки в начальное нулевое состояние – асинхронный. Это расширяет возможности регистра –возможна очистка регистра.

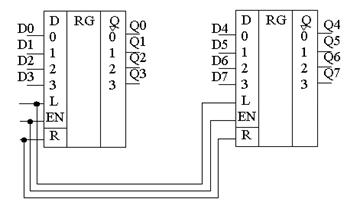

Для хранения 16-ти разрядных необходимо 2 регистра. В секции параллельных регистров запараллеливают по С, по линии сброса в 0, и по другим управляющим сигналам.

-НАРАЩИВАНИЕ

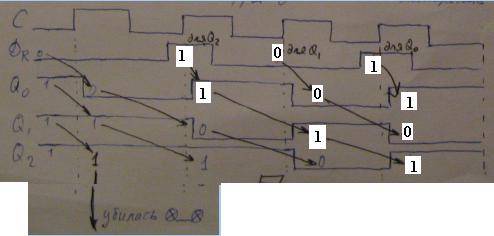

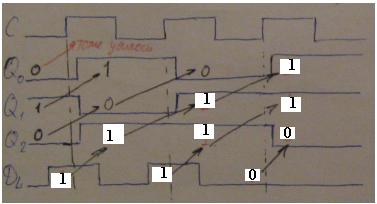

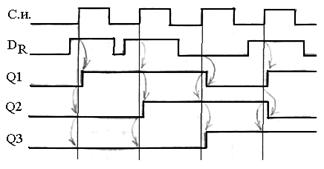

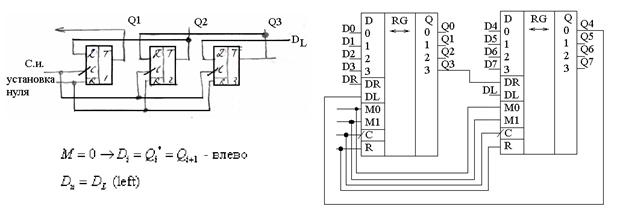

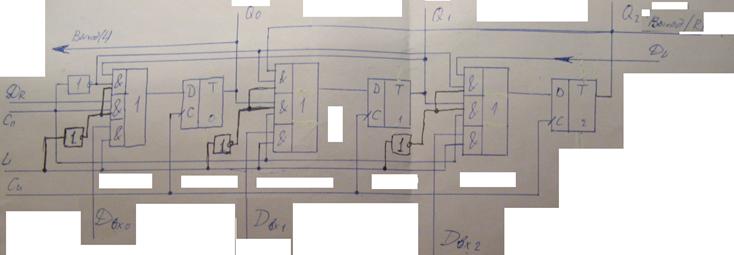

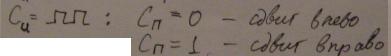

НАРАЩИВАНИЕ УНИВЕРСАЛЬНЫХ РЕГИСТРОВ. Регистры сдвига строятся, как правило, или на триггерах с динамическим управлением записью (одноступенчатые), или на триггерах с двухступенчатым запоминанием информации. Регистры сдвига состоят из элементов памяти и комбинационных схем (для передачи информации из разряда в разряд). Как правило, схема однородная, кроме первого и последнего разрядов. Регистры сдвига обычно строятся на D-триггерах. Сдвиг информации осуществляется тактовыми сигналами, поступающими на входы С всех триггеров регистра. Таблица переходов i-го разряда.

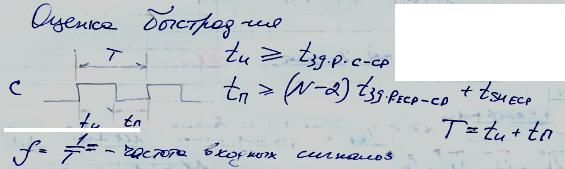

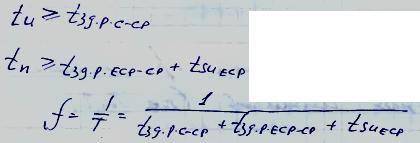

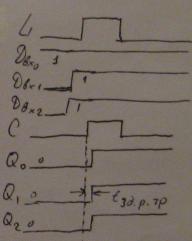

За один такт – сдвиг на один разряд (за счет динамического управления записью) Вход последовательный - Выход параллельный - Т.о. возможно преобразование последовательного кода в параллельный. Также код может сниматься последовательно с Оценка быстродействия:

-НАРАЩИВАНИЕ

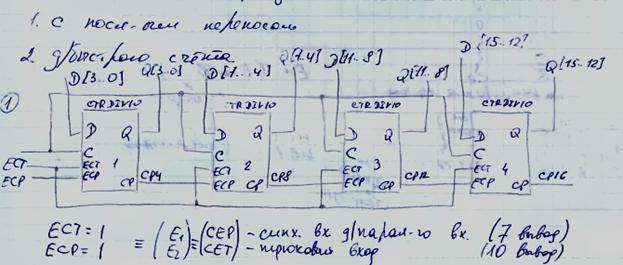

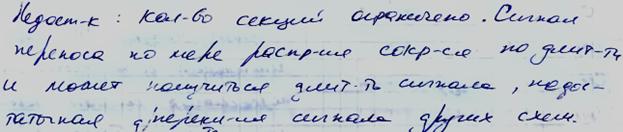

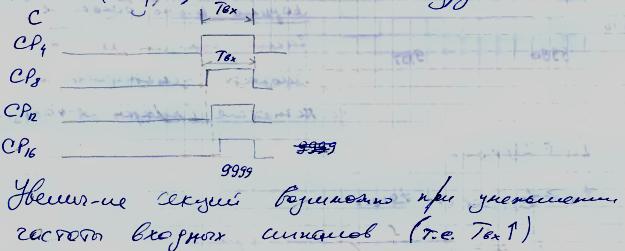

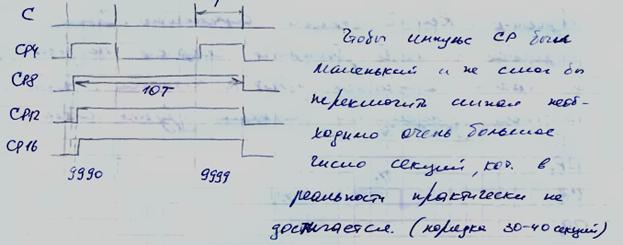

НАРАЩИВАНИЕ СЧЕТЧИКОВ

Далее на следующей странице для быстрого счета.

К 26 и 27 вопросу. Билет 4б и 5б.!!!! К 26 – синтез реверсивного регистра с || загрузкой. – билет 4б!!!

вправо - значит ввод слова в послед. Коде слева направо.- вывод

- последовательно записали 101

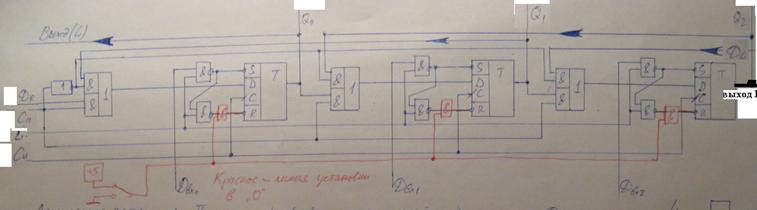

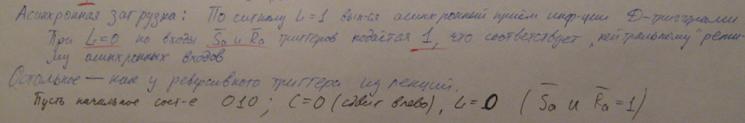

К 27 – реверсивный регистр сдвига с аинхронной загрузкой и установкой в 0 – билет 5б

где 5 вольт и все что от него идет – это линия установки в 0.(с уножением)

последовательно записали 110

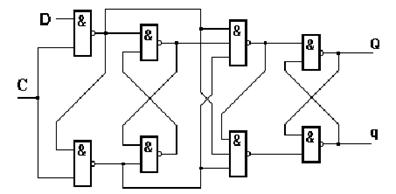

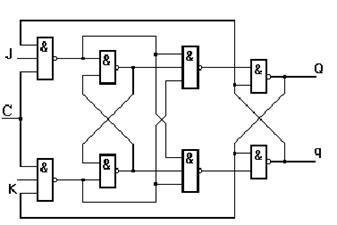

Универсальность DV и JK триггеров. В ЭВМ широко используют универсальные двухступенчатые JK-триггеры с групповыми J и K и дополнительными установочными R и S входами. Каждая группа входов J и K объединена конъюнкцией (рисунок 3.8), что позволяет расширить логические возможности JK-триггеров.

Схемы двухступенчатых (двухтактных) триггеров универсального типа имеют повышенную стабильность и помехоустойчивость работы. Универсальность триггеров достигается наличием входов несинхронизируемой установки R и S, с помощью которых, при отсутствии синхроимпульса (С=0), триггер может быть установлен в состояние 1 путем подачи S=1, либо в состояние 0 путем подачи R=1. При установленных сигналах R=S=0, не меняющих состояние схемы, переключение триггера осуществляется под воздействием синхронизирующих и информационных входов (при наличии С=1).

Независимо от типа универсальных двухступенчатых триггеров (RS, D, JK и т.д.) принцип их построения одинаков: синхронный двухтактный триггер составляется из двух частей, одновременный прием информации в которых запрещен. Для построения первой и второй ступеней используются синхронные триггеры со статическим управлением записью. Если на синхронизирующий вход подается С=1, то первой ступенью принимается входная информация в течение действия синхроимпульса. Триггер первой ступени называют основным. Если состояние синхронного входа равно 0 (С=0), то прием входной информации в первую ступень запрещается, разрешается смена сигналов на информационных либо установочных входах триггера, а вторая ступень принимает (копирует) информацию (состояние), хранимую в первой ступени.

Синхронный двухступенчатый JK-триггер

Синхронный двухступенчатый D-триггер, использует на первой ступени синхронный D-триггер со статическим управлением записью на второй - RS-триггер.

|

||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2018-05-31; просмотров: 635. stydopedya.ru не претендует на авторское право материалов, которые вылажены, но предоставляет бесплатный доступ к ним. В случае нарушения авторского права или персональных данных напишите сюда... |

при

при  - вправо

- вправо

за счет последовательного сдвига. Т.е. возможно преобразование параллельного кода в последовательный.

за счет последовательного сдвига. Т.е. возможно преобразование параллельного кода в последовательный. . Все разряды переключаются одновременно.

. Все разряды переключаются одновременно.

влево – значит ввод слова в послед. Коде справа налево. – возможен посл.

влево – значит ввод слова в послед. Коде справа налево. – возможен посл.