Студопедия КАТЕГОРИИ: АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция |

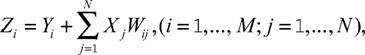

Основные вычислительные блоки векторного процессораОсновные блоки векторного поцессора определяют возможности процессора NM6403 в выполнении следующих операций: - умножение с накоплением, называемое также взвешенным суммированием; - арифметические и логические операции на векторном АЛУ; - маскирование данных; - функции активации; - сдвиг операнда Х при выполнении взвешенного суммирования. Помимо этого, приведен порядок выполнения преобразований над данными, если эти преобразования заданы в одной векторной команде. Взвешенное суммирование Операция умножения с накоплением выполняется на рабочей матрице, входящей в состав операционного узла ВП. Схематично она представлена на (см. Рис. 1-4). Математически операция взвешенного суммирования, выполняемая на операционном узле ВП, записывается следующим образом:

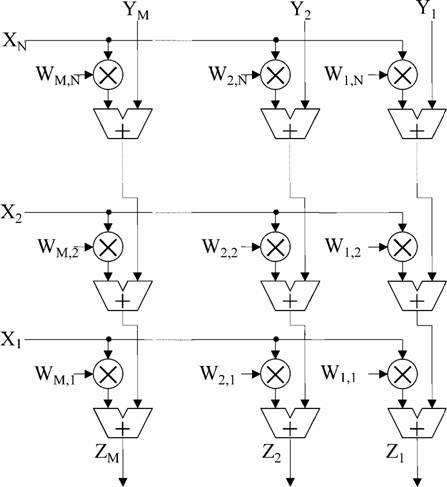

где Z i - элемент выходного вектора X j - элемент данных, поступающих на вход Xоперационного узла ВП, Y i - частичная сумма, накопленная на предыдущем шаге взвешенного сумми рования, W ij - весовой коэффициент, расположенный в соответствующей ячейке рабочей мат рицы процессора, M - количество столбцов и N - количество строк рабочей матрицы, соответственно. Рабочая матрица имеет два входа Xи Y(см. Рис. 1-5). На эти входы подаются данные, расположенные во внешней памяти, либо во внутренних буферах ram и afifo, работающих по принципу FIFO. Данные из буферов или из памяти могут быть поданы как на вход X, так и на Y. То есть, например, вектор 64-х разрядных слов, хранящийся в ram, может быть передан на обработку в операционный узел через вход Xи/или Y. Для управления потоком данных из внешней памяти используется логический буфер data. В качестве входа Yможет также быть использован векторный регистр vr. Кроме этого в качестве входов могут выступать так называемые "нулевые" устройства, что означает, что данные на вход не поступают.  Рис. 1-4 Схематичное представление операции взвешенного суммирования.

Входы Xи Yимеют различное предназначение при вычислениях. Данные, поступающие на вход X, умножаются на ячейки матрицы, и суммируются в пределах столбца. Данные, со входа Yдобавляются к результату умножения со сложением, выполненного над данными входа X. В рабочую матрицу предварительно загружаются весовые коэффициенты. Разбиение матрицы на строки определяется регистром sb2. Этот же регистр определяет разбиение 64-х разрядных слов входных данных, поступающих на вход X. В sb2 предварительно записывается слово, определяющее границы разбиения. Разбиение рабочей матрицы на столбцы задается регистром nb2. Он же определяет разбиение 64-х разрядных данных на входе Y, и разрядности результатов вычислений, содержащихся в буфере afifo. Рис. 1-5 показывает, какие действия может выполнить ВП при помощи одной процессорной инструкции. Допустим, в буфер данных ram было предварительно загружено из памяти 32 длинных слова. При операции взвешенного суммирования из памяти по очереди подчитываются слова входных данных, каждое из которых направляется на вход Xоперационного узла ВП. Параллельно из буфера ram подчитывается очередное слово и направляется на вход Y. Каждый элемент, составляющий слово на входе X, умножается на весовой коэффициент, находящийся в соответствующей ячейке рабочей матрицы, результаты умножения складываются в пределах столбца, а затем к ним добавляется значение элемента, находящегося на соответствующей позиции в слове, поступившем на вход Y. Результат операции записывается в буфер afifo. Данные, находящиеся в буферах FIFO векторного процессора, хранятся в 64-х разрядных словах. Для них на этом этапе разбиение на элементы не определено. Такое разбиение появляется только тогда, когда они поступают на вход Xили Yрабочей матрицы, или на вход векторного АЛУ. В зависимости от того, на какой вход, Хили Y, поступают данные, они делятся на элементы тем или иным образом. Рис. 1-5 Схема выполнения операции взвешенного суммирования на ВП.

Данные, находящиеся в буферах FIFO векторного процессора, хранятся в 64-х разрядных словах. Для них на этом этапе разбиение на элементы не определено. Такое разбиение появляется только тогда, когда они поступают на вход Xили Yрабочей матрицы, или на вход векторного АЛУ. В зависимости от того, на какой вход, Хили Y, поступают данные, они делятся на элементы тем или иным образом. Например, если разбиение входа X – 8 бит, то есть каждое слово представляется как 8 элементов по 8 бит, а разбиение Y – 16 бит, то в зависимости от того, куда будут направлены данные, хранящиеся в ram, на вход Xили Y, они будут трактоваться либо как массив 8-ми, либо 16-ти битных элементов. |

||

|

Последнее изменение этой страницы: 2018-05-10; просмотров: 418. stydopedya.ru не претендует на авторское право материалов, которые вылажены, но предоставляет бесплатный доступ к ним. В случае нарушения авторского права или персональных данных напишите сюда... |