Студопедия КАТЕГОРИИ: АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция |

Язык конфигурирования программируемых логических схем Verilog.Стр 1 из 12Следующая ⇒ Логические функции (1,2,3 выводные). Законы де Моргана. Нульарные функции При n = 0 количество булевых функций сводится к двум 220 = 21 = 2, первая из них тождественно равна 0, а вторая 1. Их называют булевыми константами — тождественный нуль и тождественная единица.

Унарные функции При n = 1 число булевых функций равно 221 = 22 = 4. Определение этих функций содержится в следующей таблице.

Бинарные функции При n = 2 число булевых функций равно 222 = 24 = 16.

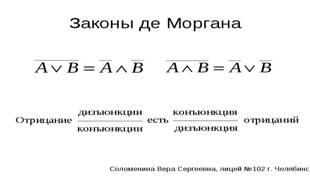

Законы де Мо́ргана (правила де Мо́ргана) — логические правила, связывающие пары дуальных логических операцийпри помощи логического отрицания. Открыты шотландским математиком Огастесом де Морганом.

Минимизация функций алгебры логики (ФАЛ). Разложение ФАЛ в различных базисах.

Язык конфигурирования программируемых логических схем Verilog. Verilog, Verilog HDL (англ. Verilog Hardware Description Language) — это язык описания аппаратуры, используемый дляописания и моделирования электронных систем. Разработчики Verilog сделали его синтаксис очень похожим на синтаксис языка C, что упрощает его освоение. Verilog имеет препроцессор, очень похожий на препроцессор языка C, и основные управляющие конструкции «if», «while» также подобны одноимённым конструкциям языка C. Соглашения по форматированию вывода также очень похожи (см. printf).Следует отметить, что описание аппаратуры, написанное на языке Verilog (как и на других HDL-языках) принято называть программами, но в отличие от общепринятого понятия программы как последовательности инструкций, здесь программа задает структуру системы. Так же для языка Verilog не применим термин "выполнение программы". Обзор:Существует подмножество инструкций языка Verilog, называемое синтезируемым. Модули, которые написаны на этом подмножестве, называют RTL (англ. register transfer level — Уровень регистровых передач). Они могут быть физически реализованы с использованием САПР синтеза. Данные САПР по определенным алгоритмам преобразуют абстрактный исходный код на Verilog в netlist — логически эквивалентное описание, состоящее из элементарных логических примитивов (например, AND, OR, NOT, триггеры), которые доступны в выбранной технологии производства СБИС или программирования БМК и ПЛИС. Дальнейшая обработка netlist в конечном итоге порождает фотошаблоны для литографии или прошивку для FPGA. Создание Verilog-95. Во время увеличивающейся популярности языка VHDL, Cadence приняла решение добиться стандартизации языка. Cadence передала Verilog в общественное достояние. Verilog был послан в IEEE и принят как стандарт IEEE 1364—1995 (часто называемый Verilog-95). Verilog 2001. Дополнения к языку Verilog-95 были приняты как IEEE 1364—2001 (или Verilog-2001).Verilog-2001 является значительно обновленным по сравнению с Verilog-95. Во-первых, он добавил поддержку знаковых переменных (в формате дополнительного кода). Прежде авторам кода приходилось реализовывать знаковые операции с использованием большого количества битовых логических операций. Та же функциональность на Verilog-2001 описывается встроенными операторами языка: +, -, /, *, >>> Был улучшен файловый ввод-вывод. Для улучшения читаемости кодов был немного изменен синтаксис, например always @*, переопределение именованных параметров, объявление заголовков функций, задач и модулей в стиле Си.Verilog-2001 является самым часто используемым диалектом языка и поддерживается в большинстве коммерческих САПР для электроники (см. EDA). Verilog 2005. Verilog 2005 (стандарт IEEE 1364—2005) добавил небольшие исправления, уточнения спецификаций и несколько новых синтаксических конструкций, например, ключевое слово uwire.Отдельная от стандарта часть, Verilog-AMS, позволяет моделировать аналоговые и аналого-цифровые устройства.

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2018-04-12; просмотров: 1089. stydopedya.ru не претендует на авторское право материалов, которые вылажены, но предоставляет бесплатный доступ к ним. В случае нарушения авторского права или персональных данных напишите сюда... |