Студопедия КАТЕГОРИИ: АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция |

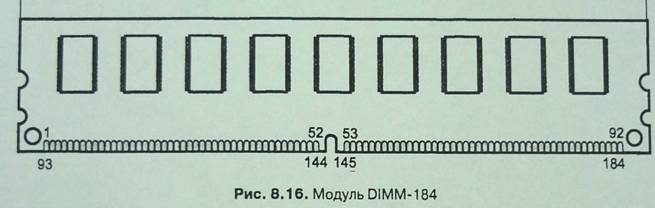

Применение модулей DRAM в оперативной памятиМодули DIMM-184 DDR SDRAM Модули DIMM-184 предназначены для микросхем DDR SDRAM. По габаритам они аналогичны модулям DIMM-168, но у них имеются дополнительные вырезы по бокам (рис. 8.16) и отсутствует левый ключ. Разрядность — 64 или 72 битов (ЕСС), имеются варианты с регистрами в адресных и управляющих цепях (Registered) и без них (Unbuffered). Напряжение питания — 2,5 В. Идентификация последовательная (SPD). Состав сигналов в основном повторяет набор для DDDR SDRAM. Модули отличаются большим количеством стробирующих сигналов DQSx — по линии на каждые 4 бита данных. Вход тактовой частоты только один, но дифференциальный — раздачу сигналов по микросхемам памяти и регистрам осуществляет микросхема DLL. 133,35

Модули DIMM-240 DDR2 SDRAM Модули DIMM-240 предназначены для микросхем DDR2 SDRAM. По габаритам они аналогичны модулям DIMM-184, но у них используется более мелкий шаг выводов (1 мм) и вырезы по бокам находятся несколько выше (рис. 8.17). Разрядность — 64 или 72 бита (ЕСС), имеются варианты с регистрами в адресных и управляющих цепях (Registered) и без них (Unbuffered). Напряжение питания — 1,8 В. Идентификация последовательная (SPD).

Модули RIMM Модули RIMM (Rambus Interface Memory Module), по форме похожие на обычные модули памяти (рис 8.18), специально предназначены для памяти RDRAM. У них 30-проводная шина проходит вдоль модуля слева направо, и на эту шину без ответвлений напаиваются микросхемы RDRAM в корпусах BGA. Модуль RIMM содержит до 16 микросхем RDRAM, которые всеми выводами (кроме двух) соединяются параллельно. Микросхемы памяти закрыты пластиной радиатора. В отличие от модулей SIMM и DIMM, у которых объем памяти кратен степени двойки, модули RIMM могут иметь более равномерный ряд объемов — в канал RDRAM память можно добавлять даже по одной микросхеме.  Маркировка Маркировка микросхем занимается специальный отдел фирмы по стандартенализаци, разных фирм между собой отдел не согласуются, поддерживаясь лишь общих правил, таких как. MCM416400J-70 400-разрядность ячейки 16 емкость-микро схемы в Мбайтах 70-время доступа к микросхеме нано секундах. J- тип корпуса микросхемы. 4-выполняемая функция. MCM-производитель.

Банк памяти Это минимально количество памяти, которая может адресовать процессор, за один раз. Разрядность банка должна быть равна разрядности банка шины данных процессора. Модули памяти могут объединятся в банки, чтобы обеспечивать, Чтобы обеспечивать соответствие разрядности модуля шины и процессора, или для организации Интерлевенг. В банк могут быть объединены только однотипные модули. Интерлевенс (чередование памяти), после обращения к ячейки динамической памяти она занята восстановлением. То есть, занята микросхема и модуль, на котором это микросхема находится. Процессору приходится простаивать пока память не восстановится, основываясь на том, что алгоритм программы большой части линеен, а следовательно наиболее вероятно обращение к ячейке памяти обращение следующей после считаемой, программы команд буду хранится друг за другом, и для увеличения производительности их разделяют на 2 банка.

Кэш память Является сверх оперативной запоминающим устройством, хранящим копии блоков оперативной памяти, в котором более вероятно обращение в ближайшее время, система сама определяет какую информацию записать в кэш память, команд к обращении кэш памяти не существует программист не может к ней обратится. Кэш предназначен для согласование быстрого процессора с относительно медленной оперативной памяти. Кэш память может разделятся на архитектуры. Гарвардская архитектура для хранения данных и команд используется разные типы памяти. Данные команды хранятся в одной памяти. По организации кэш память. Кэш память делится на уровни: · Кэш первого уровня L1-размешается на кристалле процессора и работает на его внутренней частоте относительно не большого объёма. · Кэш второго уровня L2, в первые появился у процессора i 486 DX до процессора Pentium 3 располагался на материнской плате и работал с половиной частотой относительно частоты процессора. · Кэш третьего уровня L3, обычно применялся в северных много процессорных системах. На сегодняшний день применяется настольных системах. Скорость работы меньше чем у кэш второго уровня. Под многоуровневой иерархией кэш памяти понимают необходимость использовании нескольких уровней кэш памяти, для увеличения общего объёма. Так как есть технологические приделы при изготовлении микросхем памяти каждого из уровня. Кэш память по организации может быть:

L1 L2 L3 Эксклюзивная- то есть каждый уровень кэш памяти хранит уникальные данные, и совокупный объём всей кэш памяти системы. Будет определятся как сумма объёма каждого уровня. L2 L1 L3 Инклюзивная организация памяти характеризуется тем, что более старшие уровни копируют информацию хранящеюся в младших уровнях. Совокупный объём инклюзивной кэш памяти будет равен объёму кэш памяти самого высокого уровня.

Варианты установки кэш: · Устанавливается в пластмассовые разъёмы для микросхем в кроватки. · Распаивается на материнской плате. · Устанавливается специальный слот COAST. · Процессор Pentium 2 устанавливается вместе с процессором на картридже. · В процессорах Pentium 3 и старше кэш интегрирован в кристалл процессора. Архитектура кэш памяти по свойству определения соответствия строки кэш памяти и оперативной памяти. Функция отображения Чтобы показать, как происходит выборка блоков данных из памяти в кэш, мы обратимся к простому примеру предположим у нас имеется кэш состоящий из 128 блоков по 16 слов в каждом то есть с общим количеством слов равным 2048 (2К), и основная память, адресуемая с помощью 16 разрядных адресов. Основная память имеет объём 64К слов, которые мы будем рассматривать как 4К блоков по 16 слов. Чтобы облегчить восприятие излагаемого матерела, будем считать, что последовательные адреса указывают на последовательные слова Прямое отображение. Простейшим способом сопоставлением адресов блоков в кэше и памяти, является прямое отображение. При использовании этих технологий блок j основной памяти отображается на блокj по модулю 128 кэша. Кэш с прямым отображением Основная память

Кэш

Блок 128

Тег Слово Блок

5 7 4 -Адрес основной памяти

Таким образ когда загружается один из блоков основной памяти начинающихся по адресам 0, 128, 256 и т. д. Он записывается в блок кэша 0. Блоки 1, 129, 257 и. д. записываются в блок кэша 1 и т. д.. По сколько на каждый блок кэша отображается более одного блока основной памяти то даже при не до конца заполненного кэша. Может возникнуть состязание за некоторую позицию. Например, команды программы начавшейся в блоке один после перехода могут продолжиться в блоке 129. В результате выполнения программы оба этих блока должны быть скопированы блок 1 кэша. Конфликт разрешается просто: старый блок заменяется новым. Таким образом, место положения блока в кэша, определяется на основе его адреса в памяти. Адрес памяти может быть разделён на два поля. Четыре младших разряда задают одно из 16 слов блока. Когда в кэш записывается новый блок, 7 разрядное поле номера блока данного кэша, определяет его место положения. 5 старших разрядов задают адрес блока в памяти. При записи блоков кэш они указываются в специальном поле тега (дескрипторе), такое поле имеется в кэше, для каждого из его поля. Оно определяет, какому из 32 блоков памяти отображаемых на данный момент блок кэша соответствует хранящейся здесь информации. Во время выполнения программы процессор генерирует адреса, каждым из которых 7 разрядное поле номера, блока кэша указывает на конкретный блок в нём. Тег этого блока сравнивается с со старшими блоками 5 разрядного этого адреса, и если они совпадают, значит данное слова уже имеется в кэше. В противном случаи блок содержавшие данное слово нужно извлечь из основной памяти. И поместить в кэш, технология прямого отображения очень проста. Но ей недостаёт гибкости. Ассоциативное отображение

Кэш Блок 0 Основная память

Блок 1

Блок j

Блок 4095 Тег Слово

-Адрес основной памяти 5 5

На этом рисунке показана схема гораздо более гибкого метода отображения. Согласно которому блок основной памяти можно помешать в любой блок кэша. При этом для идентификации хранящейся в кэше блоков памяти необходимо иметь уже не 5 а 12бит. При выполнении программы как бы биты сгенерированного процессором адреса по очереди сравниваются с теговыми битами каждого блока кэша. Если совпадения найдено, значит содержащий данное слово блок уже содержится в кэше. Такая технология называется ассоциативным отображением она представляет полную свободу выбора места блоков в кэше. Благодаря чему пространство кэша может использоваться более эффективно. Новые блоки заменяют на уже хранящеюся в кэше только в том случаи, если кэш заполнен, при чём для этой цели необходим алгоритм выбором удаляемого блока. Подобных алгоритмов довольно много стоимость ассоциативного кэша выше, чем кэша с прямым отображением. По сколько в нем выполняется просмотр всех 128 тегов блоков. Поиск блоков в кэше называется ассоциативным поиском. Для того чтобы он выполнялся быстро теги должны просматриваться параллельно. |

||

|

Последнее изменение этой страницы: 2018-04-12; просмотров: 505. stydopedya.ru не претендует на авторское право материалов, которые вылажены, но предоставляет бесплатный доступ к ним. В случае нарушения авторского права или персональных данных напишите сюда... |