Студопедия КАТЕГОРИИ: АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция |

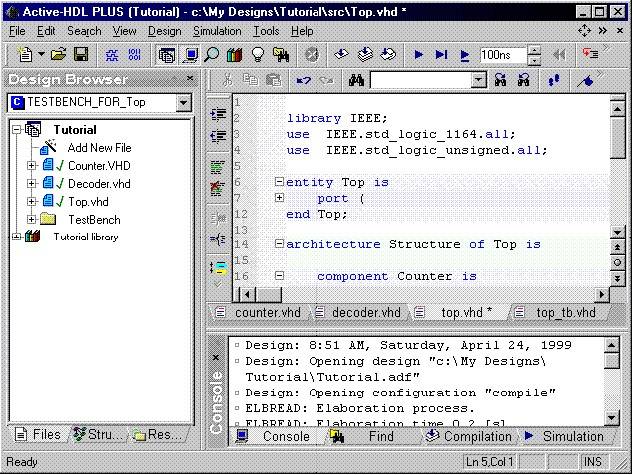

Розробка та моделювання декодера для семисегментного індикатораЛабораторна робота №1 Вивчення інтегрованого середовища автоматизованого проектування Active-HDL фірми Aldec Inc Мета роботи: ознайомитись з принципами автоматизованого проектування ПЛІС за допомогою пакету Active-HDL, вивчити структуру VHDL-проекту, навчитися працювати з засобами управління проектом. Теоретична частина Одним із світових лідерів в розробці систем автоматизованого проектування (САПР) для створення програмованих логічних інтегральних схем на базі мов описання апаратного забезпечення є корпорація Aldec Inc. Структура Active-HDL базується на стандартному GUI-інтерфейсі. Загальний вигляд екрана при роботі з САПР Active-HDL:

Головними частинами Active-HDL є: Design Browse вікно перегляду проекту, призначене для для відображення інформації про складові елементи (компоненти) проекту: HDL Editor редактор HDL-тексту з можливістю відображення заданих синтаксичних конструкцій мови різними кольорами; завдяки інтеграції редактора із симулятором компонент дозволяє виконувати зручне покрокове відлагодження пристрою і швидко виявляти помилки. Console вікно призначене для інтерактивного виводу текстової інформації, зокрема повідомленнь середовища; компонент також призначений для вводу команд середовища (Active-HDL commands). Waveform Editor редактор, призначений для графічного відображення та редагування результатів симуляції - часових діаграм.  Language Assistant компонент є зручним засобом, який дозволяє розробнику використовувати бібліотеку шаблонів опису стандартних примітивних конструкцій та функціональних блоків; Language Assistant дозволяє розміщувати вибрані шаблони безпосередньо в редагованому файлі та створювати свої власні шаблони. Порядок виконання роботи: 1. Запустити Start -> Programs -> Active-HDL. У діалоговому вікні Getting Started вибрати Cancel. 2. У вікні Active-HDL відкрити підручник по роботі з пакетом: Help \ On-line Documentation \ HDL Entry and Simulation Tutorial. Використовуючи цей підручник, ознайомитись з інтегрованим середовищем пакету, процесом створення проекту, редагування коду і його симуляції (отримання часових діаграм). 3. Відкрити проект Modulator з наборуі VHDL-прикладів (File \ Open Design \ Samples \ Modulator) та вивчити його склад і структуру за допомогою Design Browser. Скласти повний перелік об'єктів, що входять до складу проекту Modulator, описати їх інтерфейси. 4. Вивчити порядок застосування та функціональні можливості Майстра Нового Проекту (New Design Wisard). Створити за допомогою New Design Wisard порожній проект. 5. Описати на VHDL об'єкт, що являє собою RS-тригер. Інтерфейс цього об'єкта: 6. Згенерувати такий же об'єкт в окремому файлі за допомогою Майстра (Design Browser \ Add New File \ Wizards \ VHDL Source Code Wizard). Порівняти об'єкт, створений вручну із згенерованим автоматично об'єктом. 7. Згенерувати за допомогою Майстра об'єкт, що реалізує 4-бітний лічильник. Його інтерфейс: 8. Підготувати звіт до захисту. Зміст звіту 1. Назва та мета виконання лабораторної роботи. 2. Опис засобів Active-HDL для управління проектами. 3. Опис структури VHDL-проекту. 4. Перелік об'єктів проекту Modulator та їх інтерфейси. 5. Склад та структура проекту, сформованого в результаті роботи. 6. Перелік об'єктів проекту, сформованого в результаті роботи, та їх інтерфейси. 7. Висновки. Лабораторна робота №2 Розробка та моделювання декодера для семисегментного індикатора Мета роботи: вивчити методи опису поведінки об'єктів за допомогою архітектур та процесів, шляхи застосування оператора вибору case, навчитись моделювати поведінку об'єктів в САПР Active-HDL. Теоретична частина Для візуалізації процесів, що протікають в складному цифровому пристрої, необхідно виводити значення сигналів на 7-сегментний індикатор. Необхідно розробити на VHDL пристрій "декодер", що перетворює вхідний 4-розрядний двійково-десятковий код у сигнал для одного розряду 7-сегментного індикатора. Кожний розряд індикатора являє собою 7 сегментів, подання логічної одиниці на які викликає їх свічення. Наприклад, подання на індикатор числа "1101101" приведе до висвічення цифри "3":

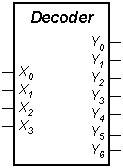

Інтерфейс декодера: · 4-розрядний вхідний порт X типу std_logic_vector (3 downto 0), · вихідний 7-розрядний порт Y типу std_logic_vector (6 downto 0):

кщо на вхід Х пристрою об'єкта поданий код від 0 до 9, декодер сформувати на виході Y сигнал, який задає зображення цього числа. Для кодів 10..15 на виході формується сигнал "0000000" (жоден сегмент індикатора не світиться). Декодер повинен оновлювати сигнал Y кожний раз, коли змінюється значення вхідного порту Х. Рекомендації до створення VHDL-опису: · Можливі значення вихідного сигналу задавати за допомогою констант. · Для перетворення вхідного сигналу з типу std_logic_vector в тип integer використовувати функцію Conv_Integer. Приклад її застосування: · При застосуванні оператора case використати можливість вибору алтернативи для всіх можливих значень змінної або сигналу. Порядок виконання роботи: 1. Створити новий проект в Active-HDL. 2. Створити об'єкт декодера та описати на VHDL його поведінку. 3. Скомпілювати створений об'єкт (меню Design \ Compile, або клавіша <F11>). 4. У вікні Design Browser для встановлення верхнього рівня моделювання (Top Level) вибрати об'єкт-декодер. 5. Ініціалізувати моделювання об'єкта (меню Simulation \ Initialize Simulation). 6. Створити в проекті новий файл Waveform Viewer (меню File \ New \ Waveform). 7. Вставити в вікно Waveform Viewer вхідний та вихідний сигнали декодера (меню Waveform \ Add Signals). 8. Призначити вхідному сигналу декодера стимулятори (меню Waveform \ Stimulators). 9. Запустити процес симуляції декодера (меню Simulation \ Run). 10. Вивчити отримані часові діаграми роботи декодера. 11. Змінюючи стимулятори на вхідних портах декодера, перевірити коректність його роботи для всіх можливих значень на вході. 12. Підготувати звіт до захисту. Зміст звіту 1. Назва та мета виконання лабораторної роботи. 2. Опис засобів Active-HDL для моделювання об'єктів. 3. Текст VHDL -опису декодера. 4. Часові діаграми роботи декодера. 5. Висновки.

|

||

|

Последнее изменение этой страницы: 2018-05-29; просмотров: 267. stydopedya.ru не претендует на авторское право материалов, которые вылажены, но предоставляет бесплатный доступ к ним. В случае нарушения авторского права или персональных данных напишите сюда... |