Студопедия КАТЕГОРИИ: АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция |

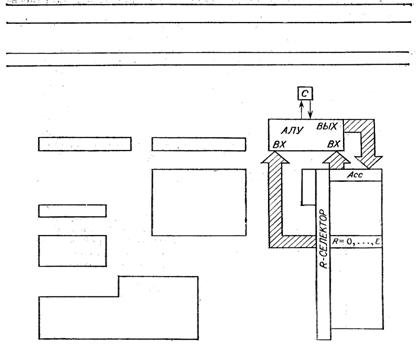

Арифметические и логические командыВсе рассмотренные выше команды были либо командами переходов, либо командами пересылки информации. Обратимся теперь к командам обработки информации. К ним относятся команды сложения, вычитания, логического И, логического ИЛИ, команды сдвигом и т. д. В качестве типичного представителя этого класса рассмотрим «сложение с- регистром и переносом» ADC R. На рис. 4.13 показаны потоки информации, когда R задает любой общий регистр в диапазоне 016, . . ., Е16. В соответствии с табл. 4.2 это однобайтовая команда. Следовательно, после второго синхроимпульса первого и единственного машинного цикла содержимое аккумулятора и регистра R может быть подано на входы АЛУ в качестве операндов. АЛУ по этим двум операндам и переносу С (считая его переносом в младший разряд) вычисляет 8-разрядную сумму и новое значение переноса.

Рис. 4.13 Информационные потоки в фазе выполнения команды ADC R, когда R ¹11112

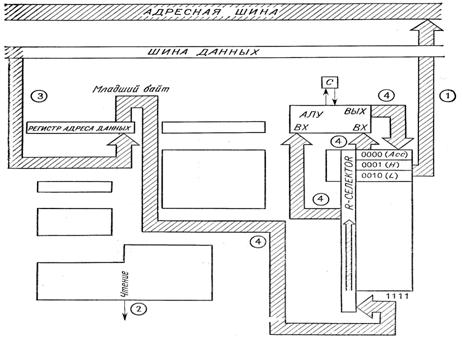

Таким образом, по третьему синхроимпульсу машинного цикла сумма передается в аккумулятор, а результирующий перенос — в триггер переноса С. Выполнение команды ADC R при R = 11112 показано на рис. 4.14.

Рис. 4.14 Информационные потоки в фазе выполнения команды ADC R, когда R = 11112

В этом случае второй машинный цикл затрачивается на выборку операнда из памяти по адресу на регистрах Н и L. Этот операнд временно заносится в младшие разряды регистра адреса данных и оттуда через R-селектор в нужный момент подается на вход АЛ У.

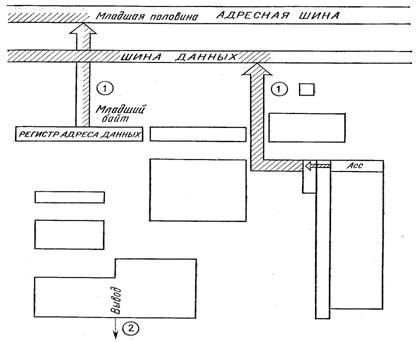

Команды ввода/вывода Теперь рассмотрим группу команд, обеспечивающих передачу информации между микропроцессором и устройствами ввода/вывода. Для конкретности остановимся на команде OUT. Поскольку это двух байтовая команда, второй байт во втором машинном цикле будет помещен в регистр адреса данных в младшую его половину. В связи с задержками распространения сигнала в шинах, а также в логических схемах устройств вывода и самого микропроцессора в фазе выполнения команды используется третий машинный цикл.  Этот цикл иллюстрирует рис. 4.15

Рис. 4.15 Информационные потоки в фазе выполнения команды OUT

По первому синхроимпульсу третьего машинного цикла содержимое младшей половины регистра адреса данных подается на адресную шину, а содержимое аккумулятора через г-селектор — на шину данных. Все устройства вывода декодируют содержимое младшей половины адресной шины. Однако только то устройство, которое опознает код на адресной шине как свой код, подает разрешающий сигнал на прием информации с шины данных в свой входной регистр. По второму синхроимпульсу третьего машинного цикла БУС подаст сигнал на линию «вывод» шины управления, который стробирует передачу содержимого шины данных в открытый для приема регистр.

Специальные команды Это последний класс команд в наборе команд микропроцессора. Они улучшают как эффективность программ, так и удобство их написания. Поскольку пару общих регистров Н и L можно использовать для обращения к ячейкам памяти при косвенной адресации, команды IHL и DHL увеличения и уменьшения значения, хранящегося в этих регистрах, оказываются очень удобными для модификации адресов. Команды разрешения и запрещения прерываний необходимы для обслуживания запросов прерывания различных устройств. Пустая команда (NOP) реализует программную задержку времени. Она бывает нужна при взаимодействии с медленными устройствами ввода/вывода. Команда останова (HLT), очевидно, позволяет закончить выполнение программы. Две оставшиеся команды в классе специальных команд это команды PUSH и POP, работающие со стеком. Когда выполняется подпрограмма или программа обработки прерывания, ей для ввода, вывода и обработки данных нужны общие регистры. Однако, как правило, они содержат информацию, нужную основной программе или подпрограмме. Поэтому содержимое трех верхних общих регистров Асс, Н и L вместе с содержимым триггера переноса С можно запомнить в стеке командой PUSH и затем в нужный момент восстановить командой POP. Это позволяет использовать регистры Асс, Н, L и триггер С при выполнении подпрограммы и вместе с тем сохранять их содержимое. Более того, поскольку информация сохраняется в стеке, процедура сохранения/восстановления может быть повторена в подпрограмме или в программе обработки прерываний, обеспечивая много уровней вложения. Фаза выполнения команды PUSH проходит за два синхроимпульса. По третьему синхроимпульсу командного цикла в стек опускается значение переноса С и аккумулятора, а затем по следующему синхроимпульсу, который фактически будет первым импульсом в следующем командном цикле, в стек опускается значение регистров Н и L. Такое совмещение командных циклов в данном случае вполне допустимо, поскольку информационные потоки не интерферируют друг с другом. Потоки информации в фазах выполнения команд POP и PUSH в точности противоположны. В приложении в конце книги приведены все команды нашего иллюстративного микропроцессора. Табл. П1 содержит команды в алфавитном порядке, а табл. П2 — в порядке кодов операций.

Способы адресации В процессе изучения системы команд мы видели, что некоторые команды ссылаются на ячейки памяти. Для одних команд — это ячейки, откуда нужно прочитать или куда нужно записать обрабатываемые данные, для других — это ячейки с командами, на которые нужно передать управление. И в том, и в другом случае адрес ячейки каким-то образом должен быть задан. Вообще говоря, часть команды, которая используется для задания адреса памяти, называется полем адреса. Поле адреса может содержать: фактический адрес ячейки памяти, как, например, в команде «загрузка регистра» LDR; или же номер общего регистра, содержащего адрес ячейки памяти, как, например, в команде ADD при R = 1111; или же само поле адреса может быть объектом ссылки, как, например, в команде LRI. В последнем случае само поле адреса содержит данные, участвующие в выполняемой операции. Способами адресации называются различные режимы интерпретации поля адреса команды. Мы отмечали, что команды могут, вообще говоря, состоять из различного числа байтов. В нашем микропроцессоре были однобайтовые, двухбайтовые и трехбайтовые команды. Число слов в команде зависит от используемых способов адресации, допустимого размера памяти и архитектуры микропроцессора. Поэтому, стремясь к эффективности программ, создатели микропроцессоров обычно предусматривают в них несколько способов адресации. В этом разделе мы рассмотрим наиболее распространенные способы адресации, хотя, вообще говоря, ни один конкретный микропроцессор, в том числе и наш иллюстративный, не обязан иметь их все. Для краткости изложения содержимое поля адреса будем называть исходным адресом, а адрес ячейки памяти, на которую в конце концов формируется ссылка и которая содержит перерабатываемые данные, будем называть эффективным адресом. Прямая адресация Наиболее естественный способ адресации — это прямая адресация. При прямой адресации в команде просто задается эффективный адрес, т. е. исходный адрес равен эффективному. Если при обращениях к памяти пользоваться только прямой адресацией, то команды, вообще говоря, будут состоять из нескольких слов. В 8-разрядном микропроцессоре, например, при памяти размером в 65536 байтов для прямой адресации нужен адрес из двух байтов (16 разрядов). Предположив, что еще один байт нам потребуется для задания самой команды, мы получим команду из 3 байтов. Примером команды с прямой адресацией в нашем микропроцессоре является команда загрузки регистра LDR. Два байта из трех в команде содержат фактический адрес ячейки памяти, которая содержит операнд, загружаемый в указанный в команде общий регистр. Непосредственная адресация При непосредственной адресации операнд команды просто является частью команды. В этом случае операнд в памяти расположен непосредственно вслед за ячейкой, содержащей «операционную» часть команды. Например, в команде LRI второй байт команды представляет собой константу, которая загружается в указанный в команде регистр. Индексная адресация В некоторых микропроцессорах эффективный адрес может быть получен сложением исходного адреса с содержимым заданного регистра. Такой способ называется индексной адресацией, а соответствующий регистр называется индекс-регистром. Обычно предусматриваются специальные команды для увеличения и уменьшения содержимого индексных регистров, и это облегчает последовательную обработку элементов таблиц в программных циклах. Иногда содержимое индекс-регистров автоматически увеличивается или уменьшается каждый раз, когда регистр используется для образования эффективного адреса. Этот способ называется автоиндексированием. Косвенная адресация Косвенная адресация — это очень эффективный и важный способ адресации в микропроцессорах. При косвенной адресации исходный адрес служит указателем на ячейку, в которой находится эффективный адрес. Таким образом, исходный адрес это «адрес адреса». Случай, когда исходный адрес указывает на общий регистр, содержащий эффективный адрес, по существу, является частным случаем косвенной адресации. Он называется регистровой косвенной адресацией. Регистровая косвенная адресация повышает эффективность программы, поскольку в команде в этом случае адресное поле должно вмещать только ссылку на общий регистр. Примером регистровой косвенной адресации может служить команда ADD R при R = 1111. Значение 1111 в младших четырех битах команды — это ссылка на общие регистры Н и L. Содержимое этих регистров воспринимается как 16-разрядный эффективный адрес. Относительная адресация Относительная адресация в чем-то близка к индексной. В ней эффективный адрес получается прибавлением исходного адреса к содержимому программного счетчика. Исходный адрес интерпретируется как число со знаком, так что относительная адресация, например, в команде перехода позволяет передать управление вперед или назад от текущего адреса на программном счетчике на заданное в программе «расстояние». Этот способ адресации особенно эффективен в командах переходов, когда переход осуществляется в близкие ячейки, поскольку не требует задания полного адреса, по которому осуществляется переход. Страничная адресация Часто объем памяти микропроцессора превышает «адресное пространство», т. е. максимальное число адресов для данного формата команд. В таком случае память можно разбить на страницы, размер которых определяется максимальным числом ячеек, адресуемых в команде. Например, если на адрес отводится только 8 разрядов, то каждая страница должна содержать 28=256 ячеек. Страницам присваиваются номера в последовательном порядке, начиная с 0. В нашем примере страница 0 будет содержать ячейки от 0 до 255, страница 1 — ячейки 256—511 и т. д. При таком подходе программный счетчик можно считать состоящим из двух частей. Старшие разряды — это номер страницы, а младшие — адрес слова внутри страницы. Метод адресации к текущей странице сводится к тому, что исходный адрес в команде считается адресом внутри той страницы, где находится сама команда, т. е. «сдвигом» относительно начала страницы. Этот метод позволяет адресовать ячейки только в текущей странице, а эффективный адрес получается, как сумма адреса начала страницы и исходного адреса в команде. Таким образом, старшие разряды эффективного адреса — это просто старшие разряды программного счетчика, а младшие разряды — это исходный адрес в самой команде. Другой метод страничной адресации называется адресацией к нулевой странице. Исходный адрес трактуется как адрес внутри нулевой страницы. Старшие разряды эффективного адреса полагаются равными нулю, а младшие — равными исходному адресу. Адресация и к текущей, и к нулевой странице является одной из форм относительной адресации и называется страничной относительной адресацией. Описанные методы страничной адресации позволяют обращаться только к ячейкам нулевой и текущей страниц. Чтобы обратиться к любой ячейке памяти, можно воспользоваться косвенной адресацией. Если, например, нужно обратиться к ячейке в странице 7, а программный счетчик показывает, что текущая команда находится в странице 3, то адрес, относящийся к странице 7, нужно запасти, либо в странице 0, либо в странице 3, и тогда операнд в странице 7 будет доступен по косвенному адресу.

Некоторые другие команды, |

||

|

Последнее изменение этой страницы: 2018-04-12; просмотров: 427. stydopedya.ru не претендует на авторское право материалов, которые вылажены, но предоставляет бесплатный доступ к ним. В случае нарушения авторского права или персональных данных напишите сюда... |