Студопедия КАТЕГОРИИ: АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция |

Последовательные (сдвиговые) регистрыСтр 1 из 6Следующая ⇒ Дешифраторы. Виды двоичных дешифраторов Дешифраторы позволяют преобразовывать одни виды бинарных кодов в другие. Например, преобразовывать позиционный двоичный код в линейный восьмеричный или шестнадцатеричный. Преобразование производится по правилам, описанным в таблицах истинности, поэтому построение дешифраторов не представляет трудностей. Для построения дешифратора можно воспользоваться правилами синтеза логических схем для произвольной таблицы истинности. Десятичный дешифратор Рассмотрим пример разработки схемы дешифратора из двоичного кода в десятичный. Десятичный код обычно отображается одним битом на одну десятичную цифру. В десятичном коде десять цифр, поэтому для отображения одного десятичного разряда требуется десять выходов дешифратора. Сигнал с этих выводов можно подать на десятичный индикатор. В простейшем случае над светодиодом можно просто подписать индицируемую цифру.Таблица истинности десятичного дешифратора приведена в таблице 1. Таблица 1. Таблица истинности десятичного дешифратора.

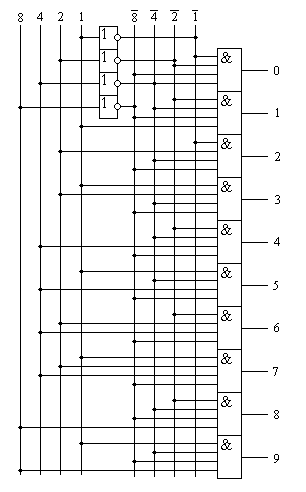

Для реализации принципиальной схемы дешифратора воспользуемся методом СДНФ, так как в его таблице истинности на каждом выходе присутствует всего одна логическая единица. В результате получим схему дешифратора, реализующего таблицу истинности, приведённую в таблице 1. Эта схема приведена на рисунке 1.  Как видно по принципиальной схеме дешифратора, для реализации каждой строки таблицы истинности потребовался логический элемент "4И". Логические элементы "ИЛИ" не потребовались, так как в таблице истинности на каждом выходе присутствует только одна логическая единица. Дешифраторы выпускаются в виде отдельных микросхем или используются в составе более сложных микросхем. В настоящее время десятичные или восьмеричные дешифраторы используются в основном как составная часть других микросхем, таких как мультиплексоры, демультиплексоры, ПЗУ или ОЗУ. Условно-графическое обозначение микросхемы дешифратора на принципиальных схемах приведено на рисунке 2. На этом рисунке приведено обозначение двоично-десятичного дешифратора, полная внутренняя принципиальная схема которого изображена на рисунке 1.

Точно таким же образом можно получить принципиальную схему и для любого другого декодера (дешифратора). Наиболее распространены схемы восьмеричных и шестнадцатеричных дешифраторов. Для индикации такие дешифраторы в настоящее время практически не используются. В основном такие дешифраторы используются как составная часть более сложных цифровых модулей. Семисегментный дешифратор Для отображения десятичных и шестнадцатеричных цифр часто используется семисегментный индикатор. Изображение семисегментного индикатора и название его сегментов приведено на рисунке 3.

Для изображения на таком индикаторе цифры 0 достаточно зажечь сегменты a, b, c, d, e, f. Для изображения цифры '1' зажигают сегменты b и c. Точно таким же образом можно получить изображения всех остальных десятичных или шестнадцатеричных цифр. Все комбинации таких изображений получили название семисегментного кода. Составим таблицу истинности дешифратора, который позволит преобразовывать двоичный код в семисегментный. Пусть сегменты зажигаются нулевым потенциалом. Тогда таблица истинности семисегментного дешифратора примет вид, приведенный в таблице 2. Конкретное значение сигналов на выходе дешифратора зависит от схемы подключения сегментов индикатора к выходу микросхемы. Эти схемы мы рассмотрим позднее, в главе, посвящённой отображению различных видов информации. Таблица 2. Таблица истинности семисегментного дешифратора

В соответствии с принципами построения произвольной таблицы истинности по произвольной таблице истинности получим принципиальную схему семисегментного дешифратора, реализующего таблицу истинности, приведённую в таблице 2. На этот раз не будем подробно расписывать процесс разработки схемы. Полученная принципиальная схема семисегментного дешифратора приведена на рисунке 4.

Для облегчения понимания принципов работы схемы на выходе логических элементов "И" показаны номера строк таблицы истинности, реализуемые ими. Например, на выходе сегмента 'a' логическая единица появится только при подаче на вход комбинации двоичных сигналов 0001 (1) и 0100 (4). Это осуществляется объединением соответствующий цепей элементом "2ИЛИ". На выходе сегмента 'b' логическая единица появится только при подаче на вход комбинации двоичных сигналов 0101 (5) и 0110 (6), и так далее. В настоящее время семисегментные дешифраторы выпускаются в виде отдельных микросхем или используются в виде готовых блоков составе других микросхем. Условно-графическое обозначение микросхемы семисегментного дешифратора приведено на рисунке 5.

В качестве примера семисегментных дешифраторов можно назвать такие микросхемы отечественного производства как К176ИД3. В современных цифровых схемах семисегментные дешифраторы обычно входят в состав больших интегральных схем.

Декодеры Декодеры позволяют преобразовывать одни виды двоичных кодов в другие. Например, преобразовывать двоичный код в линейный восьмеричный или шестнадцатеричный. Преобразование производится по правилам, описанным в таблицах истинности, поэтому построение дешифраторов не представляет трудностей. Для построения дешифратора можно воспользоваться правилами синтеза логической схемы для произвольной таблицы истинности.

Регистры Регистром называется последовательное или параллельное соединение триггеров. Они обычно строятся на основе D триггеров. При этом для построения регистров могут использоваться как динамические (flip-flop), так и статические D-триггеры (защелки — lath). Параллельные регистры Параллельный регистр служит для запоминания многоразрядного двоичного (или недвоичного) слова. Количество триггеров, входящее в состав параллельного регистра определяет его разрядность. Схема четырёхразрядного параллельного регистра приведена на рисунке 1, а его условно-графическое обозначение — на рисунке 2.

В условно-графическом обозначении возле каждого входа D указывается степень двоичного разряда, который должен быть запомнен в этом разряде. Точно таким же образом обозначаются и выходы регистра. То, что микросхема является регистром, указывается в центральном поле условно-графического обозначения символами RG. В приведённом на рисунке 2 условно-графическом обозначении параллельного регистра инверсные выходы триггеров не показаны. В промышленно выпускающихся микросхемах параллельных регистров инверсные выходы триггеров часто не выводятся наружу для экономии количества выводов корпуса.

При записи информации в параллельный регистр все биты (двоичные разряды) должны быть записаны одновременно. Поэтому все тактовые входы триггеров, входящих в состав регистра, объединяются параллельно. Для уменьшения входного тока вывода синхронизации C на этом входе в качестве усилителя часто ставится инвертор. Следует помнить, что назначение разрядов является условным. Если по каким либо причинам (например, с точки зрения разводки печатной платы) удобно изменить нумерацию разрядов, то это можно свободно сделать. При перенумерации входов регистров нужно не забывать, точно таким же образом, изменить номера выходов. Для реализации параллельного регистра можно использовать как триггеры с статическим, так и с динамическим входом синхронизации. В переводной литературе при использовании для построения параллельного регистра триггеров-защелок этот регистр, в свою очередь, называют регистром-защелкой. При использовании регистров со статическим входом тактирования следует соблюдать осторожность, так как при единичном потенциале на входе синхронизации C. сигналы с входов регистра будут свободно проходить на его выходы. В таких случаях обычно используется двухтактная синхронизация, подобная рассмотренной в главе, посвященной использованию одновибраторов. Промышленностью выпускаются четырёхразрядные и восьмиразрядные микросхемы параллельных регистров. Для построения восьмиразрядных микросхем обычно используются регистры со статическим входом синхронизации. В качестве примера можно назвать микросхемы К580ИР22 и 1533ИР33 (иностранный аналог 74ACT573). При решении практических задач часто требуется разрядность параллельных регистров большая восьми. В таком случае можно увеличивать их разрядность параллельным соединением готовых микросхем. Принципиальная схема параллельного соединения четырёх регистров приведена на рисунке 3.

В настоящее время параллельные регистры обычно являются частью более сложных цифровых устройств, таких как цифровые фильтры, ОЗУ, синтезаторы частот или схемы прямого цифрового синтеза DDS. Подобные схемы не реализуются на микросхемах средней интеграции, а являются частью больших интегральных микросхем (БИС), таких как микропроцессоры, ASIC или FPGA.

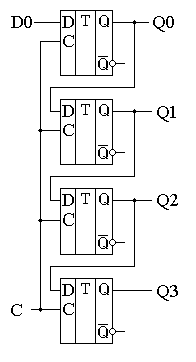

Последовательные (сдвиговые) регистры Кроме параллельного соединения триггеров для построения регистров используются последовательноесоединение этих элементов. Последовательный регистр (регистр сдвига или сдвиговый регистр) обычно служит для преобразования последовательного кода в параллельный и наоборот. Применение последовательного кода связано с необходимостью передачи большого количества двоичной информации по ограниченному количеству соединительных линий. При параллельной передаче разрядов требуется большое количество соединительных проводников. Если двоичные разряды последовательно бит за битом передавать по одному проводнику, то можно значительно сократить размеры соединительных линий на плате (и размеры корпусов микросхем). Принципиальная схема последовательного (сдвигового) регистра, собранного на основе D триггеров и позволяющего осуществить преобразование последовательного кода в параллельный, приведена на рисунке 1. Обратите внимание, что если для параллельных регистров подходили как триггеры работающие по потенциалу (триггеры-защелки), так и триггеры, работающие по фронту, то для реализации последовательного (сдвигового) регистра подходят только D триггеры, работающие по фронту!

Внутри сдвигового регистра триггеры соединены последовательно, то есть выход первого соединён с входом второго и т.д. Условно-графическое изображение рассмотренного последовательного регистра приведено на рисунке 2.

Входы синхронизации в последовательных (сдвиговых) регистрах, как и в параллельных регистрах, объединяются. Это обеспечивает одновременность смены состояния всех триггеров, входящих в состав последовательного (сдвигового) регистра. Преобразование последовательного кода в параллельный в последовательном (сдвиговом) регистре производится следующим образом. Отдельные биты двоичной информации последовательно подаются на вход сдвигового регистра D0. Каждый бит сопровождается отдельным тактовым импульсом синхронизации, который поступает на вход синхронизации последовательного регистра C. После поступления первого тактового импульса логический уровень, присутствующий на входе D0, запоминается в первом триггере последовательного (сдвигового) регистра и поступает на его выход, а так как он соединён с входом второго триггера, то и на его вход. Если бы последовательный (сдвиговый) регистр был собран на D триггерах, работающих по потенциалу, то этот бит тут же записался во второй D триггер! В нашем случае этого не происходит, так как к этому моменту фронт на входе синхронизации C уже закончился. После поступления второго тактового импульса логический уровень, присутствующий на входе второго триггера последовательного (сдвигового) регистра, запоминается в нем и поступает на его выход, а так как он соединён с входом третьего триггера, то и на его вход. Одновременно следующий бит входного последовательного кода запоминается в первом триггере последовательного (сдвигового) регистра. После поступления четвертого тактового импульса в триггерах последовательного (сдвигового) регистра будут записаны логические уровни бит, которые последовательно присутствовали на его входе D0. Теперь этими битами можно воспользоваться, например, для отображения на индикаторах. Пусть на вход последовательного (сдвигового) регистра поступает сигнал, временная диаграмма которого изображена на рисунке 3, тогда состояние выходов этого регистра будет последовательно принимать значения, записанные в таблице 1.

На рисунке 3 вместе с логическими уровнями записываются значения бит, которые передаются по соединительной линии или присутствуют на выходах сдвигового регистра.

В качестве примера реализации последовательного (сдвигового) регистра можно назвать отечественную микросхему 1564ИР1 или иностранную 74НС164.

Универсальные регистры Регистры сдвига выполняют обычно как универсальные последовательно-параллельные микросхемы. Это связано с необходимостью записи в регистр параллельного двоичного кода при преобразовании параллельного кода в последовательный. Переключение регистра из параллельного режима работы в последовательный и наоборот осуществляется при помощи мультиплексора (коммутатора). Использование коммутатора позволяет входы D триггеров универсального регистра либо подключать к внешним выводам микросхемы, либо подключать к выходу предыдущего триггера. Напомню, что двухвходовый мультиплексор можно реализовать при помощи логических элементов “2И-2ИЛИ”. Элементы “И” при этом работают в качестве электронных ключей, а элементы “ИЛИ” объединяют их выходы. Схема универсального регистра с использованием коммутаторов на логических элементах “2И-2ИЛИ” приведена на рисунке 1.

В этой схеме для переключения регистра из последовательного режима работы в параллельный используется вывод V. Подача на этот вход единичного потенциала превращает схему в параллельный регистр. При этом на входы ключей, подключенных к информационным входам D, подаётся единичный потенциал. Это приводит к тому, что сигналы с входов параллельной записи данных поступают на входы логических элементов “ИЛИ”, а на входы ключей, подключенных к выходам предыдущих триггеров, подаются нулевые потенциалы. То есть на выходах этих ключей будут присутствовать нулевые потенциалы, и они не будут мешать работе. Подача на вход V нулевого потенциала приводит к отключению входов параллельных данных от входов триггеров. Сигналы же с выхода предыдущего триггера свободно проходит через верхние логические элементы “И” на вход последующего триггера, так как на его второй вход подаётся единичный потенциал. Инверторы на входах V и C использованы для усиления входного сигнала по току. В результате входной ток микросхемы будет равен не суммарному току четырёх логических элементов “И”, а входному току инвертора. Условно-графическое изображение универсального регистра приведено на рисунке 2. Вход последовательного ввода данных на этом рисунке обозначен как DI и отделён от других групп входов чертой. Точно так же выделены в отдельные группы и входы управления V и синхронизации C.

Счётчики Счётчики используются для построения схем таймеров или для выборки инструкций из ПЗУ в микропроцессорах. Они могут использоваться как делители частоты в управляемых генераторах частоты (синтезаторах). При использовании в цепи ФАП счётчики могут быть использованы для умножения частоты как в синтезаторах, так и в микропроцессорах. Вниманию любителей баннерорезок. Данная статья полностью искажается любыми антирекламными программами. Они очень не любят слово "счетчик", поэтому почти все рисунки вырезаются, насколько искажается текст не вчитывался :) |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2018-04-12; просмотров: 468. stydopedya.ru не претендует на авторское право материалов, которые вылажены, но предоставляет бесплатный доступ к ним. В случае нарушения авторского права или персональных данных напишите сюда... |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||