Студопедия КАТЕГОРИИ: АвтоАвтоматизацияАрхитектураАстрономияАудитБиологияБухгалтерияВоенное делоГенетикаГеографияГеологияГосударствоДомЖурналистика и СМИИзобретательствоИностранные языкиИнформатикаИскусствоИсторияКомпьютерыКулинарияКультураЛексикологияЛитератураЛогикаМаркетингМатематикаМашиностроениеМедицинаМенеджментМеталлы и СваркаМеханикаМузыкаНаселениеОбразованиеОхрана безопасности жизниОхрана ТрудаПедагогикаПолитикаПравоПриборостроениеПрограммированиеПроизводствоПромышленностьПсихологияРадиоРегилияСвязьСоциологияСпортСтандартизацияСтроительствоТехнологииТорговляТуризмФизикаФизиологияФилософияФинансыХимияХозяйствоЦеннообразованиеЧерчениеЭкологияЭконометрикаЭкономикаЭлектроникаЮриспунденкция |

Описание заданного комплекса технических средств

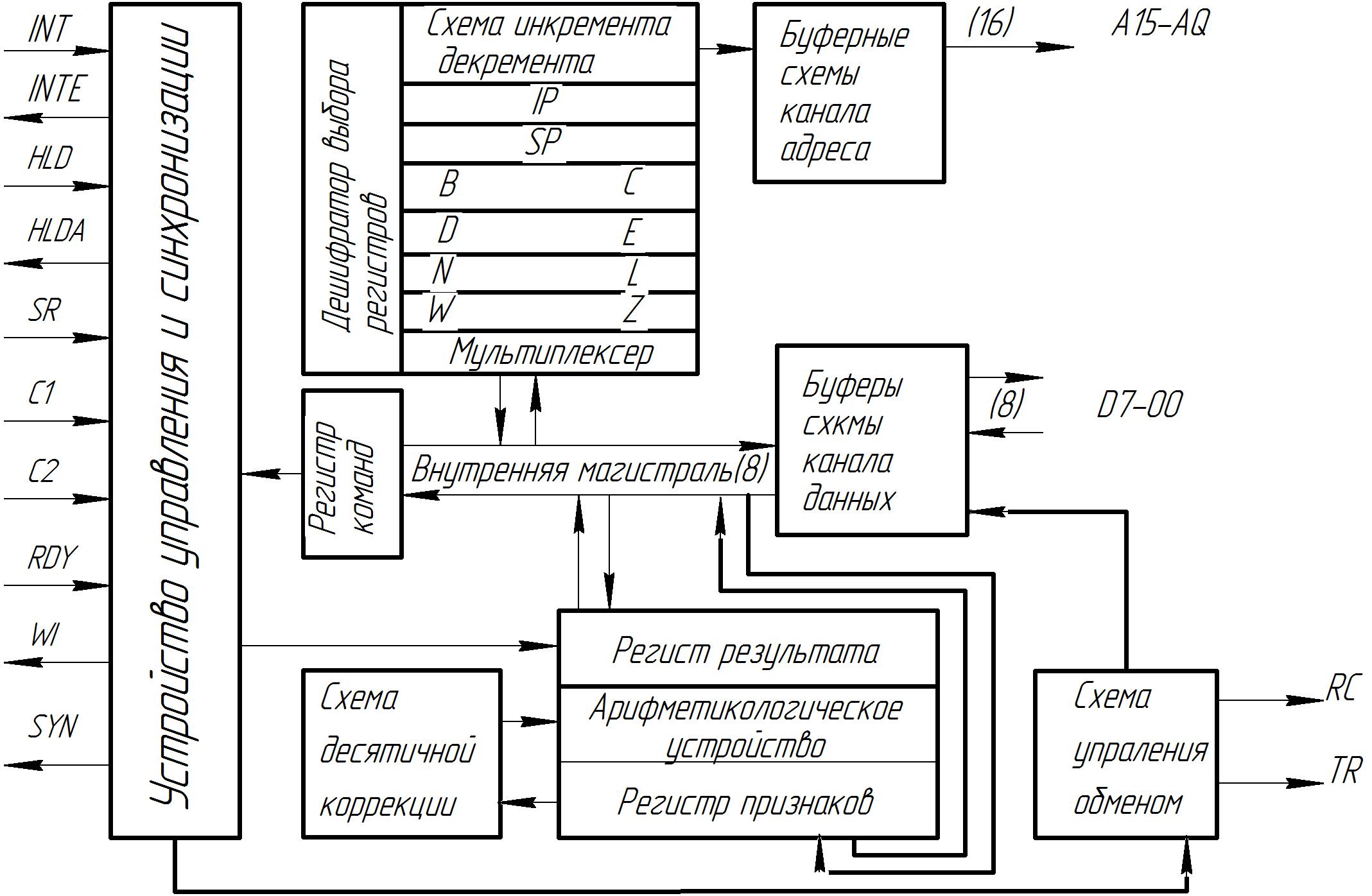

Функционально законченный однокристальный параллельный 8 разрядный микропроцессор с фиксированной системой команд применяется в качестве центрального процессора и устройствах обработки данных и управления. Микропроцессор имеет раздельные 16 разрядный канал адреса и 8 разрядный канал данных. Канал адреса обеспечивает прямую адресацию внешней памяти объемом до 65536 байт 256 устройств ввода и 256 устройств вывода. Восьмиразрядное арифметико-логическое устройство микропроцессора обеспечивает выполнение арифметических и логических операций над двоичными данными, представленными в дополнительном коде, а также обработку двоично-десятичных упакованных чисел. В состав блока регистров входят 16 разрядный регистр адреса команды (IP), 16 разрядный регистр указателя стека (SP), 16 разрядный регистр временного хранения (WZ), 16 разрядная схема инкремента декремента и шесть 8 разрядных регистров общего назначения (B, C,D,E,H,L) которые могут использоваться и как три 16 разрядных регистров (ВС,DE, HL). Микропроцессор выполняет команды по машинным циклам. Число циклов необходимое для выполнения команды зависит от ее типа и может быть от одного до пяти. Машинные циклы выполняются по машинным тактам. Число тактов в цикле определяется кодом выполняемой команды и может быть от трех до пяти. Длительность такта равна периоду тактовой частоты и при частоте 20 МГц составляет 500 нс. В начале каждого машинного цикла микропроцессор вырабатывает сигнал синхронизации, который в сочетании с другими сигналами может быть использован для организации различных режимов работы.

Рисунок 8 - Условное графическое обозначение КР580ВМ80А

На рисунок 8 изображена диаграмма состояний типичного машинного цикла, показывающая последовательность перехода от такта к такту в машинном цикле и влияние внешних сигналов RDY, HLD, и INTна выполнение машинного цикла. После подачи на вывод SRсигнала высокого уровня микропроцессор устанавливается в исходное состояние. В такте Т1 микропроцессор выдает на адресный канал адрес ячейки, в которой хранится команда программы, а через канал данных - информацию в состояния. В такте Т2 анализируются состояния сигналов на входе RDY, «Подтверждение останова» и в зависимости от состояния этих сигналов МП переходит в состояние ожидания, останова или к выполнению такта ТЗ. В такте ТЗ при наличии сигнала высокого уровня на входе RDYМП принимает информацию по каналу данных; анализирует состояние сигнала на входе HLD. При низком уровне сигнала проверяется, кончено ли выполнение команды. Если команда не закончена, то микропроцессор выполняет следующий машинный цикл команды, начиная с такта Т1. В конце каждой команды микропроцессор анализирует состояние сигнала на входе INT. Если сигнал высокого уровня и прерывание было ранее разрешено командой Е1, то микропроцессор переходит к выполнению машинного цикла «Прерывание», начиная с такта Т1. В противном случае выполняется первый машинный цикл новой команды с такта Т1. Таблица 5- Функциональное назначение выводов

Действия, выполняемые микропроцессором в конкретном машинном цикле, определяются 8-разрядной информацией состояния, которая выдается через канал данных в такте Т1 каждого машинного цикла. Эта информация может использоваться для выработки сигналов обращения к ЗУ, УВВ и для организации различных режимов работы микропроцессора.

В зависимости от сочетания сигналов состояния, выдаваемых в конкретном цикле, машинные циклы можно разделить на 10 типов: 1. Цикл Ml- прием первого байта команды в регистр команд. 2. Цикл чтения ЗУ - чтение ЗУ по содержимому программного счетчика или содержимому одного из регистров ВС, DE, HL. 3. Цикл записи в ЗУ - запись в ЗУ по содержимому одного из регистров ВС, DE, HL. 4. Цикл чтения стека — чтение ЗУ по содержимому указателя стека. 5. Цикл записи в стек - запись в ЗУ по содержимому указателя стека. 6. Цикл ввода - ввод информации в регистр результата (аккумулятор) из внешнего устройства. 7. Цикл вывода - вывод информации из регистра результата во внешнее устройство. 8. Цикл прерывания - прием кода команды RST илиCALLиз контроллера прерываний. 9. Цикл останова. 10. Цикл прерывания при останове - прием кода команды RSTили CALL привыводе микропроцессора из режима «Останов» по прерыванию. При выполнении команд микропроцессор может переходить в одно из трех состояний: «ожидание», «захват» и «останов», длительность которых определяется внешними управляющими сигналами. Сигнал высокого уровня на входе RDYобеспечивает автоматическое выполнение команд программы микропроцессором с частотой тактовых сигналов. Если на выводе RDY установлен сигнал низкого уровня, то микропроцессор переходит в режим «Ожидание» и формирует выходной сигнал W1 высокого уровня. СигналRDY может быть использован для согласования работы микропроцессора с работой медленнодействующих устройств, если длительность их цикла обращения составляет более одного периода тактовой частоты, а также для организации пошагового (по циклам) выполнения команды или покомандного выполнения программы. При подаче на входHDL сигнала высокого уровня микропроцессор переходит в состояние «захват» и подтверждает переход в это состояние формирования сигналавысокого уровня на выходе HLDA. Буферные схемы канала адреса и данных микропроцессора переключаются в высокоомное состояние, в выходные управляющие сигналы в состояние низкого уровня (за исключением сигналов TR и HLDA). Микропроцессор переходит в состояние «захват» в такте ТЗ, если выполняется цикл чтения и на входе RDY сигнал высокого уровня, и в такте, следующим за ТЗ, если выполняется цикл записи. Сигналы HLD и НLDА позволяют организовать режим прямого доступа к памяти для любого внешнего устройства, формирующего сигнала HLD.

Рисунок 9 - Диаграмма состояний типичного машинного цикла КР580ВМ80А

При выполнении команды HLTмикропроцессор переходит в состояние «Останов» и переводит буферные схемы канала адреса и данных в высокоомное состояние. Из состояния «останов» микропроцессор выходит при наличии сигнала высокого уровня на одном из его входов: - на входе SR— микропроцессор начинает работать с такта Т1 цикла М1. - на входе HLD- микропроцессор переходит в состояние «захват», а после перехода сигнала HLDна низкий уровень возвращается в состояние «останов». - на входе INT— микропроцессор переходит к выполнению цикла прерывания при останове с такта Т1, если команде HLTпредшествовала команда Е1 «разрешение, прерывания», иначе остается в состоянии «останов». Сигнал высокого уровня на выводе INTпозволяет прерывать выполнение текущей программы и переводить микропроцессор на выполнение подпрограммы обслуживания устройства, выдавшего, выдавшего запрос прерывания. При поступлении сигнала INTмикропроцессор (после окончания текущей команды) переходит с такта Т1к выполнению машинного цикла «Прерывание» в том случае, если прерывание было разрешено ранее командой Е1. При выполнении цикла «Прерывание» в такте Т1 микропроцессор выдает по шине данных сигнал состояния «Подтверждение прерывания», который используется для разрешения выдачи из внешнего контроллера прерывания (КР580ВН59) на канал данных системы команды и адреса перехода на подпрограммы прерывания осуществляют возврат к прерванной программе. Сигнал высокого уровня на входе SR (длительность которого должна быть не менее трех периодов тактовой частоты) устанавливает микропроцессор в исходное состояние триггер разрешения прерывания, триггер захвата, регистр команд, регистр признаков и регистр адреса команды устанавливаются в нулевое состояние. После окончания действия сигнала SRмикропроцессорпроизводит первое обращение за чтением команды к ячейке памяти по адресу OOOO16. Система команд микропроцессора состоит из 78 базовых команд, которые можно разделить на пять групп: - команды передачи данных — используются для передачи данных из регистра в регистр, из памяти в регистр, из регистра в память; - арифметические команды — используются для сложения, вычитания, инкремента или декремента содержимого регистров или ячейки памяти; - логические команды И, ИЛИ, исключающие ИЛИ, сравнение, сдвиги; команды переходов — используются для условных и безусловных переходов, вызова подпрограмм и возврата из них команды управления, ввода вывода и работы со стеком — используются для управления прерыванием, регистром признаков, ввода и вывода информации. В микропроцессоре КР580ВМ80А принят формат информационного слова, представляющего собой 8 разрядное двоичное слово (байт). Формат команды зависит от типа операции может быть одно, двух или трехбайтовым. Байты двух и трехбайтовых команд должны храниться в ячейках памяти, следующих одна за другой.

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Последнее изменение этой страницы: 2018-04-12; просмотров: 559. stydopedya.ru не претендует на авторское право материалов, которые вылажены, но предоставляет бесплатный доступ к ним. В случае нарушения авторского права или персональных данных напишите сюда... |

Рисунок 9 - Структурная схема КР580ВМ80А

Рисунок 9 - Структурная схема КР580ВМ80А